Fターム[5F092AB06]の内容

Fターム[5F092AB06]の下位に属するFターム

マトリックス型 (149)

選択トランジスタを有するもの (815)

Fターム[5F092AB06]に分類される特許

21 - 40 / 470

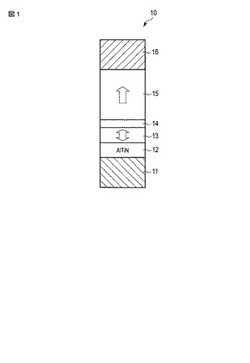

磁気抵抗素子

【課題】書き込み電流の低減を図る。

【解決手段】実施形態による磁気抵抗素子は、膜面に垂直方向の磁気異方性を有し、磁化方向が可変である記録層13と、膜面に垂直方向の磁気異方性を有し、磁化方向が不変である参照層15と、記録層及び参照層間に設けられた中間層14と、記録層の中間層が設けられた面と反対面に設けられ、AlTiNを含有する下地層12と、を具備する。

(もっと読む)

薄膜磁気センサ及びその製造方法

【課題】水分透過量が小さいSi系絶縁膜が回路表面に形成されており、Si系絶縁膜の密着性及び耐クラック性に優れた薄膜磁気センサ及びその製造方法を提供すること。

【解決手段】以下の工程を備えた薄膜磁気センサの製造方法及びこの方法により得られる薄膜磁気センサ。(1)基板表面に薄膜ヨーク、GMR膜、電極及び配線を備えた素子部を形成する素子部形成工程。(2)少なくとも電極の表面の全部又は一部を含む領域(薄膜ヨーク、GMR膜及び配線の表面を除く)にフォトレジスト膜を形成するフォトレジスト膜形成工程。(3)基板の表面にAl2O3膜を形成するAl2O3膜形成工程。(4)Al2O3膜の表面に、Cat−CVD法を用いてSi系絶縁膜を形成するSi系絶縁膜形成工程。(5)フォトレジスト膜、並びに、フォトレジスト膜の上に形成された余分なAl2O3膜及びSi系絶縁膜を除去する除去工程。

(もっと読む)

光不揮発性メモリ

【課題】光信号を直接不揮発的に記憶する光不揮発性メモリを提供すること。

【解決手段】第1導電型を有する第1半導体層12と、前記第1導電型とは異なる第2導電型を有する第2半導体層16と、前記第1半導体層と前記第2半導体層とに挟まれ、逆バイアスが印加されることにより受光し、順バイアスが印加されることにより発光する活性層14と、前記活性層の受光する光の強さによって磁化方向が変化する強磁性体層20と、を具備する光不揮発性メモリ。

(もっと読む)

磁壁移動型の磁気記録素子及び磁気記録方法

【課題】磁壁の移動が可能となる閾値電流密度を、従来技術であるスピントルクを利用して電流で磁壁移動を行った場合と比較して低減する磁壁移動型の磁気記録素子構造及び閾値電流密度を低減化させる磁気記録方法を提供すること。

【解決手段】本発明の磁壁移動型の磁気記録素子は、金属層/磁性層/非伝導層の3層膜から構成される実効磁場発生構造を持ち、前記磁性層に電流を流したときに発生する実効磁場とスピントルクを用いて前記磁性層中の磁壁の位置を制御することを特徴とする。

(もっと読む)

スピン注入磁化反転素子

【課題】MgOを障壁層として磁化反転電流を低減したTMR素子構造を備える光変調素子を提供する。

【解決手段】光変調素子5は、磁化固定層11、MgOからなる障壁層12、磁化自由層13を積層してなるTMR素子構造1と、その上下に接続した上部電極3、下部電極2を備える。下部電極2は、組成がCu1-xCrx(0.07<x<0.42)である非晶質のCu−Cr合金からなり、磁化固定層11は非晶質の磁性体からなり、このような非晶質の層の上に、障壁層12としてMgO膜が形成されるため、MgO膜が強い(001)面配向を示して、TMR素子構造1の磁化反転電流を低減できる。

(もっと読む)

半導体記憶装置

【課題】磁気抵抗効果素子間の磁気的な干渉作用を遮断し、安定した動作を可能にし、且つ、容易に製造することができる半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、半導体基板上にマトリックス状に配列した複数の磁気抵抗効果素子を有し、各磁気抵抗効果素子は、半導体基板上に形成された第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成された第2の磁性層とからなる積層構造を有し、隣り合う各磁気抵抗効果素子の間には、金属、又は、磁性体材料が分散された絶縁膜が埋め込まれている。

(もっと読む)

磁気記録素子及び磁気メモリ

【課題】磁気記録素子のMR比の向上を図る。

【解決手段】実施形態に係わる磁気記録素子は、磁化が可変で磁化容易軸方向が膜面に垂直となる方向の磁気記録層11と、磁化が膜面に垂直となる方向に固定される磁気固着層12と、磁気記録層11と磁気固着層12との間の非磁性バリア層13と、磁気記録層11と非磁性バリア層13との間の挿入層14とを備える。挿入層14は、軟磁性材料、ホイスラー合金、ハーフメタル酸化物、及び、ハーフメタル窒化物のうちの1つを含む。

(もっと読む)

半導体記憶装置

【課題】安定した特性の磁気抵抗効果素子を有する半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、複数の磁気抵抗効果素子を有し、この各磁気抵抗効果素子は、半導体基板上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第2の磁性層と、からなる積層構造を有し、保護膜を介して各磁気抵抗効果素子の側壁を覆うように設けられ、且つ、磁気抵抗効果素子に対して、磁化容易軸に沿った方向に引張応力を与える側壁膜を備え、側壁膜のうちの第1の磁性層を覆う部分は、側壁膜のうちの第2の磁性層を覆う部分と比べて厚い。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】製造コストの増加を抑えつつ、直列に接続されたMTJ素子を所望の特性の抵抗体として機能させることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、磁化方向に応じて抵抗値が変化可能な複数の記憶用MTJ素子が、半導体基板上に配置されたメモリセルアレイ領域を備える。半導体記憶装置は、複数の抵抗用MTJ素子が、前記半導体基板上に第1の方向および前記第1の方向に垂直な第2の方向に沿って配置された抵抗素子領域を備える。前記半導体基板の上面に平行な前記抵抗用MTJ素子の第1の断面の面積は、前記半導体基板の前記上面に平行な前記記憶用MTJ素子の第2の断面の面積よりも、大きい。

(もっと読む)

半導体不揮発性記憶装置およびその製造方法

【課題】高い信頼性で書き込み・消去・読み出しが可能な低コストの半導体不揮発性記憶装置およびその製造方法を提供する。

【解決手段】実施形態の半導体不揮発性記憶装置は、基体Sと、第1の電極2と、機能膜10と、第2の電極50と、を持つ。前記第1の電極2は、前記基体S上に設けられる。前記機能膜10は、前記第1の電極2上に成膜されて記憶媒体をなす。前記第2の電極50は、上面に凸の曲面を有するように、前記機能膜10上または前記機能膜10内に設けられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】MRAMの下層強誘電体層と上層強誘電体層がショートしているか否かを検査することができる。

【解決手段】TEG素子100は、テスト用下層強誘電体層112、テスト用トンネル絶縁膜114、及びテスト用上層強誘電体層116を有している。テスト用下層強誘電体層112は、下層強誘電体層42と同一層に位置し、下層強誘電体層42と同一材料により形成されており、第1テスト用パッド120に接続している。テスト用トンネル絶縁膜114は、トンネル絶縁膜44と同一層に位置し、トンネル絶縁膜44と同一材料により形成されている。テスト用上層強誘電体層116は、上層強誘電体層46と同一層に位置し、上層強誘電体層46と同一材料により形成されており、第2テスト用パッド130に接続している。

(もっと読む)

スピン伝導素子

【課題】出力を向上可能なスピン伝導素子を提供する。

【解決手段】 このスピン伝導素子は、半導体層3と、半導体層3上に第1トンネル障壁層5Aを介して設けられた第1強磁性層1と、半導体層3上に、第1強磁性層1から離間し、且つ、第2トンネル障壁層5Bを介して設けられた第2強磁性層2と、を備え、半導体層3は、第1強磁性層1からその厚み方向に垂直な方向に沿って、第1強磁性層1から離れる方向へ広がる第1領域R1と、第1強磁性層1からその厚み方向に垂直な方向に沿って、第2強磁性層2に向かう方向に延びており、第1領域R1の不純物濃度よりも相対的に高い不純物濃度を有する第2領域R12と、を備えている。

(もっと読む)

磁気抵抗素子の製造方法及び製造装置

【課題】エッチングに用いられるハロゲン系成分による素子の腐食を防止することが可能な磁気抵抗素子の製造装置及び製造方法を提供すること

【解決手段】本発明の磁気抵抗素子10の製造方法は、基板上に強磁性材料からなる第1の強磁性層13を形成する。酸化マグネシウムからなる絶縁層14は、第1の強磁性層13上に形成される。Fe及びCoの少なくとも一方を含有する第2の強磁性層15は、絶縁層14上に形成される。ハロゲン系元素を含むプラズマによるエッチングは、基板11上に第1の強磁性層13、絶縁層14及び第2の強磁性層15が積層された積層体に対して施される。積層体は、H2Oを含むプラズマであるH2Oプラズマに曝露される。

(もっと読む)

不揮発性光メモリ、光記憶装置、ネットワークルータ

【課題】本発明は、光信号の情報を記憶させておくために電力を消費することがなく、光信号の情報の書込み、および読出しを高速にかつ簡単な構成で行なうことができる不揮発性光メモリを提供する。

【解決手段】本発明は、電子のスピン偏極状態を利用して光信号を記憶する半導体レーザー構造を備えた不揮発性光メモリ10である。不揮発性光メモリ10は、GaAs基板1と、GaAs基板1上に、異なる屈折率の半導体膜を交互に積層することで形成してある分布ブラッグ反射層2と、分布ブラッグ反射層2上に、量子井戸構造を有する半導体活性層3とを備えている。発光領域10aの半導体活性層3上に、異なる屈折率の半導体膜を交互に積層することで形成してある分布ブラッグ反射層4と、受光領域10bの半導体活性層3上の一部に、半導体活性層3の表面に対して垂直の磁化方向を有する強磁性電極5とを備えている。

(もっと読む)

膜形成方法および不揮発性記憶装置

【課題】より良質な膜を形成する。

【解決手段】実施形態の膜形成方法は、下地の上に設けられた酸素及び窒素の少なくともいずれかを含む膜の表面に、酸素及び窒素の少なくともいずれかを含むイオン化されたガスクラスタを照射して、前記ガスクラスタを照射した後の前記膜の密度を前記ガスクラスタを照射する前の前記膜の密度よりも高くする。

(もっと読む)

スピン伝導素子及び磁気ヘッド

【課題】 トンネル層における面抵抗の低減が図られたスピン伝導素子及び磁気ヘッドを提供する。

【解決手段】

本発明に係るスピン伝導素子(磁気センサー1)は、半導体で構成されるチャンネル層10と、チャンネル層10上に形成された強磁性層20A、20Bと、チャンネル層10と強磁性層20A、20Bとの間に介在するように形成されたトンネル層22A、22Bとを備え、トンネル層22A、22Bが、MgOのMgの一部がZnで置換された材料で構成されている。発明者らの研究によれば、MgOのMgの一部をZnで置換したトンネル材料において、面積抵抗の低下が観測された。そのため、トンネル層22A、22Bを、MgOのMgの一部がZnで置換された材料で構成することにより、トンネル層22A、22Bの面積抵抗の低減が図られる。

(もっと読む)

スピンMOSFETを用いたメモリ回路、メモリ機能付きパストランジスタ回路、スイッチングボックス回路、スイッチングブロック回路、およびフィールドプログラマブルゲートアレイ

【課題】高速、不揮発性、低消費電力のメモリ回路を提供する。

【解決手段】一方のソース/ドレインがノード40に接続された第1導電型スピンMOSFET10と、一方のソース/ドレインがノード40に接続された第1導電型スピンMOSFETもしくは第1導電型のMOSFET12と、ノード40にゲート電極が接続され一方のソース/ドレイン電極が出力端子37に接続されたpチャネルスピンMOSFETもしくはpチャネルのMOSFET14と、ノード40にゲート電極が接続され、一方のソース/ドレイン電極が出力端子37に接続されたnチャネルスピンMOSFETもしくはnチャネルのMOSFET16と、出力端子37と、を備え、第3トランジスタ14と第4トランジスタ16はインバータ回路を構成し、第3トランジスタ14および第4トランジスタ16の少なくとも一方がスピンMOSFETであり、出力端子37からインバータ回路が出力される。

(もっと読む)

半導体装置の製造方法

【課題】 信号量の低減を抑制できる磁気抵抗効果によるメモリ素子を具備する半導体装置の製造方法を提供すること。

【解決手段】 コバルト、鉄およびニッケルの少なくとも一つを含む磁性材料を用いた磁気抵抗効果素子を形成する工程を含む半導体装置の製造方法であって、前記磁気抵抗効果素子を形成する工程は、半導体基板1上に、前記磁性材料を含む複数の層4,5,8を具備する積層体3−10を形成する工程と、真空雰囲気中で、塩素を含むガスを用いたプラズマエッチングにより、前記積層体3−10を加工する工程と、前記積層体3−10を加工した後、前記積層体3−10を真空雰囲気中に保持したまま、前記積層体3−10に対してアミノ基を含むガスを用いガス処理を施す工程とを含む。

(もっと読む)

スピン伝導素子及び磁気ヘッド

【課題】 スピン注入効率の向上が図られたスピン伝導素子及び磁気ヘッドを提供する。

【解決手段】

発明者らは、Siで構成されるチャンネル層10と、チャンネル層10上に形成された強磁性層20A、20Bと、チャンネル層10と強磁性層20A、20Bとの間に介在するように形成されたトンネル層22A、22Bとを備え、トンネル層22A、22Bが、NaCl構造のアルカリ土類酸化物(たとえばBaO)で構成されており、かつ、該アルカリ土類酸化物のアルカリ土類イオン(たとえばBaイオン)の一部が、異なる種類のアルカリ土類イオン(たとえばMgイオン)に置換された磁気センサー1を新たに見いだした。

(もっと読む)

21 - 40 / 470

[ Back to top ]