Fターム[5F092AB06]の内容

Fターム[5F092AB06]の下位に属するFターム

マトリックス型 (149)

選択トランジスタを有するもの (815)

Fターム[5F092AB06]に分類される特許

41 - 60 / 470

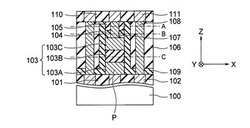

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

スピン伝導素子及び磁気ヘッド

【課題】高温域におけるスピン注入効率の低下が抑制されたスピン伝導素子及び磁気ヘッドを提供する。

【解決手段】Siで構成されるチャンネル層10と、チャンネル層10上に形成された強磁性層20A、20Bと、チャンネル層10と強磁性層20A、20Bとの間に介在するように形成され、BaOで構成されるトンネル層22A、22Bとを備える構造のスピン伝導素子。シリコンの格子定数は5.4309Åであり、BaOの格子定数は5.5263Åである。シリコンの格子定数に対して、BaOの格子定数は1.8%の差(不整合率)があり、この値は、シリコンとMgOの格子定数の差と比較して1/5程度である。トンネル材料としてBaOを採用し、シリコンとトンネル材料との間の格子定数の差を従来材料に比べて低減することで、高温域におけるスピン注入効率の低下が抑制される。

(もっと読む)

多層膜の製造方法

【課題】多層膜内の特定層だけに格子振動を与えてその多層膜の特性を向上させる。

【解決手段】実施形態に係わる多層膜の製造方法は、第1の層(CoFeB)を形成する工程と、第1の層(CoFeB)上に第2の層(MgO)を形成する工程と、第2の層(MgO)の表面に対してGCIB照射を行うことにより、第2の層(MgO)の結晶情報を第1の層(CoFeB)に転写する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、耐熱性に乏しいMTJ素子等の素子の劣化を避けつつ、良好な半導体装置を形成することができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に複数の素子を形成し、複数の素子の間を埋め込むようにシリコン化合物膜を形成し、マイクロ波を照射することにより、シリコン化合物膜を酸化シリコン膜に改質する。

(もっと読む)

連想メモリ

【課題】 低消費電力で、高速に動作可能な連想メモリを提供する。

【解決手段】 本発明の実施形態によれば、記憶データに応じて第1の磁化状態に設定される第1のスピンMOSFETと前記記憶データに応じて第2の磁化状態に設定される第2のスピンMOSFETとが並列に接続されたスピンMOSFET対と、検索データに応じて、前記第1のスピンMOSFETおよび第2のスピンMOSFETのいずれか一方が導通するようゲート電圧を印加する第1の配線と、前記スピンMOSFET対に対して電流を印加する第2の配線とを有する。

(もっと読む)

動力発生装置、音響再生装置、インジェクション装置、位置制御装置、光スイッチング装置

【課題】電磁力利用の動力発生装置に関し低消費電力化・部品点数の削減を図る。

【解決手段】例えばMTJ素子(磁気トンネル接合素子)などの磁気メモリ素子を利用した動力発生装置とする。磁気メモリ素子は磁化状態が平行状態のときに漏洩磁界が生じるため、当該漏洩磁界を永久磁石に作用させて動力を発生する。動力の発生は磁気メモリ素子に値を書き込むことで可能となるため、駆動信号としては符号”0””1”の組み合わせで成るデジタル信号を用いることができる。これによりD/Aコンバータを不要とでき部品点数の削減が図られる。また磁気メモリ素子は一度電流を流して値を書き込めば平行状態/反平行状態を維持するものであり、従って動力を継続して得るにあたり電力を与え続ける必要性はなく、この面で低消費電力化が図られる。

(もっと読む)

スピントランジスタおよび磁気デバイス

【課題】磁化の相対角度で出力電流が制御可能で、かつ、ゲート層に電圧を印加することでも出力電流が制御可能なスピントランジスタを提供する。また、このスピントランジスタを集積化した磁気メモリや不揮発性論理回路などの磁気デバイスを提供する。

【解決手段】ソース層14、ゲート層13およびドレイン層15が、ハーフメタルホイスラー合金から成る。ソース層14とゲート層13との間に介在する第1の絶縁層16、および、ゲート層13とドレイン層15との間に介在する第2の絶縁層17が、酸化マグネシウム(MgO)から成る。ゲート層13を含み、ゲート層13に静電容量を介してゲート電圧を印加可能なゲート構造が、クロム/酸化マグネシウム/ハーフメタルホイスラー合金から成る。

(もっと読む)

MTJ膜及びその製造方法

【課題】高い結晶配向性を有する強磁性層の上にトンネルバリア層を形成することによってMTJ膜を作成する場合に、読み出し特性の劣化を抑制すること。

【解決手段】MTJ膜の製造方法は、第1強磁性層を形成する工程と、第1強磁性層の上にトンネルバリア層を形成する工程と、トンネルバリア層の上に第2強磁性層を形成する工程と、を含む。第1強磁性層は、垂直磁気異方性を有するCo/Ni積層膜である。トンネルバリア層を形成する工程は、単位成膜処理をn回(nは2以上の整数)繰り返すことを含む。単位成膜処理は、Mg膜をスパッタ法により堆積する工程と、堆積されたMg膜を酸化する工程と、を含む。1回目の単位成膜処理において堆積されるMg膜の膜厚は、0.3nm以上0.5nm以下である。2回目以降の単位成膜処理において堆積されるMg膜の膜厚は、0.1nm以上0.45nm以下である。

(もっと読む)

スパッタリング装置、及び電子デバイスの製造方法

【課題】短時間で薄膜を積層させる場合であっても、スループットを損なうことなく効率的に上記積層を実現可能なスパッタリング装置、及び電子デバイスの製造方法を提供すること。

【解決手段】本発明の一実施形態に係るスパッタリング装置は、回転可能な基板ホルダー103と、基板ホルダー130に対して斜めに配置されたターゲットホルダー107a〜107dと、ターゲットホルダーと基板ホルダーの間に設けられ、回転軸Xに対して2回対称に配置された2個の孔を有する第1シャッター115および第2シャッター116とを備える。ターゲットホルダー107a、107cは、回転軸Xに対して2回対称な位置に配置される第1群のターゲットホルダーであり、ターゲットホルダー107b、107dは、第1群のターゲットホルダー同士の間に回転軸Xに対して2回対称に配置される第2群のターゲットホルダーである。

(もっと読む)

電流によって誘起されたスピンモーメント移行をベースとした高速かつ低電力の磁気デバイス

【課題】磁気メモリとして最適であるような構造を提供する。

【解決手段】本発明は、磁気デバイスに関するものであって、固定磁化方向を有した磁化ベクトルを備えたピン止めされた磁化層(FM1)と;変更可能な磁化方向を有した少なくとも1つの磁化ベクトルを備えた自由磁化層(FM2)と;ピン止めされた磁化層と自由磁化層とを空間的に分離する第1非磁性層であるとともに、この分離によって、ピン止めされた磁化層と自由磁化層との間の磁気的相互作用を最小化させるような、第1非磁性層(N1)と;を具備している。

(もっと読む)

磁気スタックおよびメモリセル、ならびにセルを製造する方法

【課題】データ記憶装置における増加された記憶容量をもたらし得るより小さい全体セル厚さを提供する。

【解決手段】STRAMセルのような、不揮発性メモリセルについての装置および関連する方法が開示される。さまざまな実施形態に従えば、磁気自由層は、非磁気スペーサ層によって反強磁性層(AFM)から横方向に分離されるとともに、磁気トンネル接合によって合成反強磁性層(SAF)から内側に分離される。AFMは、磁気トンネル接合を超えて横方向に伸延するSAFのピニング領域との接触を通じて、SAFの磁化を固定する。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

不揮発性ラッチ回路および半導体集積回路

【課題】 抵抗変化素子の磁化特性が劣化することを防止し、読み出しマージン等の電気的特性の低下を防止する。

【解決手段】 不揮発性ラッチ回路は、相補の記憶ノードである第1および第2ノードを含むラッチ回路と、電流を流すことにより抵抗値が変化する第1および第2抵抗変化素子と、第1および第2抵抗変化素子をラッチ回路に接続するスイッチ回路とを有している。スイッチ回路は、外部からラッチ回路に論理が書き込まれる通常動作時に、第1および第2抵抗変化素子とラッチ回路との接続を遮断する。これにより、外部からラッチ回路の論理が書き換えられるときに、第1および第2抵抗変化素子に電流が流れることを防止でき、抵抗変化素子の磁化特性が劣化することを防止できる。この結果、読み出しマージン等の電気的特性の低下を防止できる。

(もっと読む)

高垂直異方性及び面内平衡磁化を有する自由層を備えたスピン転移磁気素子

【課題】磁気メモリに用い得る磁気素子を作製するための方法及びシステムを提供する。

【解決手段】磁気素子には、固定層と、非磁性スペーサ層と、自由層とが含まれる。スペーサ層は固定層と自由層との間にある。自由層は、書き込み電流が磁気素子を通過する時にスピン転移を用いて切換え得る。磁気素子には更に、バリア層と第2固定層とを含み得る。他の選択肢として、第2固定層と第2スペーサ層と自由層に静磁気的に結合された第2自由層とが含まれる。少なくとも1つの自由層が高垂直異方性を有する。高垂直異方性は、面外減磁エネルギの少なくとも20%であり且つ100パーセント未満である垂直異方性エネルギを有する。

(もっと読む)

装置および磁気素子

【課題】データ変換ヘッドにおける読取センサとして、または固体不揮発性メモリ素子などとして使用するための、磁気状態の変化を検出可能な磁気素子を提供する。

【解決手段】さまざまな実施例によれば、磁気素子は、第1の面積範囲を有する磁気応答性スタックまたは積層を含む。スタックは、第1および第2の強磁性フリー層間に位置付けられたスペーサ層を含む。少なくとも1つの反強磁性(AFM)タブが、第1のフリー層に、スペーサ層とは反対側のその表面上で接続されており、AFMタブは、第1の面積範囲よりも小さい第2の面積範囲を有する。

(もっと読む)

トンネル磁気抵抗素子

【課題】マグネタイト(Fe3O4)膜を一方の電極とし、マグネタイト本来のスピン依存電気伝導特性をより反映した、室温で20%以上の負のMR比を示すTMR素子を提供すること。

【解決手段】マグネタイト電極と、該マグネタイト電極上に成膜された酸化マグネシウム層と該酸化マグネシウム層上に成膜された2nm以下の厚さの酸化アルミニウム非晶質層とからなる障壁層と、を備えるトンネル磁気抵抗素子である。サファイア基板(00.1)面上に、マグネタイトを[111]方向にエピタキシャル成膜してマグネタイト電極を形成し、該電極上に酸化マグネシウム層を[111]方向にエピタキシャル成膜し、その上に酸化アルミニウム非晶質層を成膜して障壁層を形成する。

(もっと読む)

トンネルバリアの形成方法および磁気トンネル接合(MTJ)の形成方法

【課題】高いMR比と低いRA値とを両立させるトンネルバリアの形成方法を提供する。

【解決手段】本発明のトンネルバリアの形成方法は、TMRセンサ40Aに用いられるトンネルバリア29を形成するものであり、ピンド層24に対してNOX処理を施す工程と、ピンド層24の上にM1層を形成する工程と、NOX処理を行い、M1層をMox1層25に変換する工程と、M1層よりも薄いM2層の蒸着とそのNOX処理とを繰り返すことで、Mox1層の上にMox2層26を含むスタックを形成する工程と、そのスタックの上に、Mox1層25およびMox2層26よりも薄い最上部金属層を形成する工程と、アニール処理により、内部の酸素を拡散させて最上部金属層を酸化することでMox3層27を得る工程とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体チップを磁気シールド層で被覆しても、バンプを狭いピッチで配置することができるようにする。

【解決手段】半導体チップ100は磁気記憶素子10を有しており、かつ第1面に電極パッドを有している。磁気シールド層400は、少なくとも電極パッドが露出した状態で半導体チップ100を被覆している。半導体チップ100は、バンプ310を介して配線基板200に実装されている。半導体チップ100と配線基板200は、少なくとも一方が凸部を有しており、当該凸部上にバンプ310が設けられている。

(もっと読む)

磁性積層体、方法、およびメモリセル

【課題】フォノンブロック絶縁層を有する不揮発性メモリセルのための装置および関連の方法を提供する。

【解決手段】さまざまな実施形態に従うと、磁性積層体は、トンネル接合と、強磁性フリー層と、ピンド層と、少なくとも1つの導電性構造を通る電気的伝導を許しつつフォノンをブロックする電気絶縁性および断熱性の材料から構築される絶縁層とを有する。

(もっと読む)

低飽和磁化自由層を有するスピン転移磁気素子

【課題】より低いスイッチング電流密度で磁気素子に書き込みを行うこと。

【解決手段】磁気素子100は、固定層110と、非磁性であるスペーサ層120と、自由層磁化を有する自由層130とを備える。スペーサ層120は、固定層110と自由層130との間に存在する。自由層130は、被ドープ強磁性材料を含む。被ドープ強磁性材料は、自由層130が室温で1430emu/cm3以下の低飽和磁化を有するように、少なくとも1つの非磁性材料で希釈された少なくとも1つの強磁性材料か、フェリ磁性的にドープされた少なくとも1つの強磁性材料か、又は、少なくとも1つの非磁性材料で希釈され且つフェリ磁性的にドープされた少なくとも1つの強磁性材料を含む。書き込み電流が磁気素子100を通過する時、自由層磁化がスピン転移を用いて切換えられる。

(もっと読む)

41 - 60 / 470

[ Back to top ]