Fターム[5F110AA18]の内容

Fターム[5F110AA18]に分類される特許

61 - 80 / 237

薄膜半導体装置及びその製造方法

【課題】イオン注入によりアモルファス化された領域に光照射による活性化を行った場合に、表面に凹凸が発生するのを防止した薄膜半導体素子及びその製造方法を提供する。

【解決手段】基板1上にそれぞれ形成されたnチャネル島状半導体層4a及びpチャネル島状半導体層4b、前記島状半導体層4a,4b上に形成されたゲート絶縁膜5、及び前記ゲート絶縁膜5上にそれぞれ形成されたゲート電極6a,6bを具備し、前記nチャネル島状半導体層4aへのn型不純物のイオン注入によりアモルファス化された領域の深さt1,t3と、前記pチャネル島状半導体層4bへのp型不純物のイオン注入によりアモルファス化された領域の深さt1,t2とは、それぞれほぼ同じであるようにイオン注入を行なう。

(もっと読む)

半導体素子の製造方法及び電気光学装置の製造方法

【課題】例えば、高い膜質を有する多結晶シリコン層を活性層とする薄膜トランジスタを製造する。

【解決手段】第1膜(211)の上面(211t)と、上面(211t)に交差する第1膜(211)の側面(211s)とによって構成された角部(212)をなくすように、第1膜(211)にスライスエッチング処理を施し、第1膜(211)から第2膜(220)を形成する。即ち、第2膜(220)の角部(222)の断面形状は、第1膜(211)の角部(212)に比べて、角が取れているように、或いは曲線で構成されるように形成されている。尚、スライスエッチング処理とは、第1膜(211)上から第1膜(211)にエッチング液を接触させることによって、通常のウェットエッチング法及びドライエッチング法に比べて、緩やかに、言い換えれば、マイルドに第1膜(211)をエッチング処理することをいう。

(もっと読む)

半導体基板の作製方法及び半導体装置

【課題】良好な結晶性を有し高性能な半導体素子を形成することを可能とする半導体基板を提供する。

【解決手段】脆化層を有する単結晶半導体基板と、ベース基板とを絶縁層を介して貼り合わせ、熱処理によって、脆化層を境として単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を固定し、単結晶半導体層にレーザ光を照射し、単結晶半導体層を部分溶融状態として再結晶化し、結晶欠陥を修復する。また、単結晶半導体層の結晶性を最良とするレーザ光のエネルギー密度をマイクロ波光導電減衰法によって検出する。

(もっと読む)

半導体基板の製造方法及びその方法により得られた半導体基板

【課題】基材上に設けられた半導体ナノ粒子を含む印刷層を、低温かつ短時間で焼成処理して、ち密かつ平滑で性能に優れ、さらに薄い半導体層を形成してなる半導体基板を効率よく製造する方法を提供する。

【解決手段】基材上に、半導体ナノ粒子を含む塗布液をパターン状に印刷して印刷層を形成した後、この印刷層を焼成処理してパターン状の半導体層を形成する半導体基板の製造方法であって、マイクロ波エネルギーの印加により発生する表面波プラズマに前記印刷層を晒すことにより、該印刷層の焼成処理を行うことを特徴とする半導体基板の製造方法、である。

(もっと読む)

SOI基板の作製方法

【課題】ガラス基板のような耐熱性の低い基板をベース基板として使用した場合にも、実用に耐えうるSOI基板の作製方法を提供する。

【解決手段】SOI基板の作製において、ボンド基板中に脆化層を形成する際の水素イオンドーズ量を、ボンド基板の分離下限となる水素イオンドーズ量より増加して脆化層を形成し、ベース基板に貼り合わせたボンド基板を分離して、ベース基板上に単結晶半導体膜が形成されたSOI基板を形成し、該単結晶半導体膜の表面にレーザ光を照射して作製する。

(もっと読む)

表示装置およびその製造方法

【課題】マスク工程の増大なく、薄膜トランジスタのゲート絶縁膜、および配線交差部における層間絶縁膜において、それぞれ適切な厚さを有して形成できる表示装置の提供。

【解決手段】絶縁基板上に、第1第2の薄膜トランジスタを形成する工程と、前記第1薄膜トランジスタのゲート電極、前記第2薄膜トランジスタのゲート電極、前記ゲート信号線をも被って絶縁膜を形成する工程と、前記絶縁膜上に脱水素化した第1非晶質シリコン半導体層を形成する工程と、前記第1薄膜トランジスタの形成領域における前記第1非晶質シリコン半導体層を多結晶シリコン半導体層に変質させる工程と、前記第2薄膜トランジスタの形成領域における前記非晶質シリコン半導体層、前記絶縁膜の表面からの一部を順次エッチングする工程と、前記多結晶シリコン半導体層および前記第1非晶質シリコン半導体層をも被って前記絶縁膜上に第2非晶質シリコン半導体層を形成する工程とを含む。

(もっと読む)

有機薄膜トランジスタおよびその製造方法

【課題】 有機薄膜トランジスタにおいて、ゲート絶縁膜上の電流チャネルにおけるスムーズなキャリアの移動を可能とし、高いキャリア移動度を実現する。

【解決手段】 絶縁性基板10と、絶縁性基板上に形成されたゲート電極11と、ゲート電極11上に形成されたゲート絶縁膜12と、ゲート絶縁膜12上に積層され、ゲート絶縁膜12に接する界面近傍に電流チャネル16を有する有機電子材料膜13と、有機電子材料膜の電流チャネル16に電流を流すためのソース電極15およびドレイン電極14と、を備え、電流チャネル16に流れる電流を制御するゲート電極12が、アモルファス金属よりなることを特徴とする有機薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】半導体装置Sは、各第2領域R2の少なくとも一部の平坦な領域に互いに同じ厚みで形成された第1平坦化膜13と、各第1平坦化膜13の間にゲート電極8a,8bを覆うように設けられて第1平坦化膜13よりも研磨選択比が小さい材料により構成され、第1平坦化膜13の表面と面一になるように研磨されることにより第1平坦化膜13の表面に連続する平坦な表面を有する第2平坦化膜14とを備えている。基体層1の一部は、第1平坦化膜13又は第2平坦化膜14を介して剥離用物質がイオン注入されることにより形成された剥離層に沿って分離されている。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】構造的に安定でありながらもチャネル部におけるキャリア移動度が確保された特性の良好なボトムコンタクト・トップゲート型の薄膜トランジスタを有する半導体装置を提供する。

【解決手段】基板11の表面側に埋め込まれたソース電極13sおよびドレイン電極13dと、ソース電極13sおよびドレイン電極13dとこれらの間の基板11とに接する状態で基板11上に設けられた半導体層15と、半導体層15上に設けられたゲート絶縁膜17と、ソース電極13s−ドレイン電極13d間における半導体層15上にゲート絶縁膜17を介して設けられたゲート電極19とを備えた半導体装置1である。

(もっと読む)

強誘電体ゲート電界効果トランジスタ、それを用いたメモリ素子及び強誘電体ゲート電界効果トランジスタの製造方法

【課題】ゲート構造にIFI構造が含まれるMFS型メモリの強誘電体ゲート電界効果トランジスタにおいて、強誘電体膜の強誘電体特性及びトランジスタの電気特性の劣化を防止する。

【解決手段】Si基板1と、Si基板1上に少なくともHfSiON膜2、強誘電体膜3及びHfSiON膜4が、この順で積層されたゲート構造を有しており、HfSiON膜2及びHfSiON膜4は、強誘電体膜3を加熱処理によって形成する焼成温度で非晶質である。

(もっと読む)

表示装置

【課題】表示装置に備えられる金属酸化物半導体からなる薄膜トランジスタにおいて、そのオフ電流をさらに低減させ、かつ動作の安定化を図るようにした表示装置の提供。

【解決手段】基板上に金属酸化物半導体層を半導体層とする薄膜トランジスタを備える表示装置であって、

前記基板と薄膜トランジスタの間にシリコン窒化膜がバリア層として形成され、

前記薄膜トランジスタのゲート絶縁膜はプラズマCVD法によって形成されたシリコン窒化膜からなる。

(もっと読む)

半導体装置の製造方法

【課題】活性領域表面に凹凸を生じることなく活性領域上端の角部を丸めることができる半導体装置の製造方法を提供する。

【解決手段】活性領域を画定する素子分離絶縁膜を形成する工程と、活性領域上に、0.1nm以上、0.7nm未満の膜厚の自然酸化膜を形成する工程と、水素を含む雰囲気中で、850℃よりも高く950℃未満の温度で熱処理を行い、活性領域の角部を丸めるとともに、自然酸化膜を還元除去する工程と、自然酸化膜を除去した活性領域上に、ゲート絶縁膜を形成する工程とを有する。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに導電性パターン及びその形成方法

【課題】有機トランジスタの電極として利用可能で、かつ、塗布法で形成可能な金属種を用いて電極を形成し、当該電極と下地層との間の段差を無くす。

【解決手段】薄膜トランジスタの製造方法であって、基板101上に有機金属化合物を塗布する第1塗布ステップと、基板101上に塗布された有機金属化合物の第1領域を第1雰囲気中で加熱することで、導電性の低い平坦化絶縁層103を形成する第1絶縁領域形成ステップと、有機金属化合物の第1領域とは異なる第2領域を、第1雰囲気とは異なる第2雰囲気中で加熱することで、平坦化絶縁層103より導電性の高いゲート電極102を形成する電極領域形成ステップとを含み、平坦化絶縁層103の厚さとゲート電極102の厚さとは等しく、平坦化絶縁層103とゲート電極102との表面が平坦である。

(もっと読む)

表示装置およびその製造方法

【課題】隔壁上からの成膜によって分断され、微細化パターニングされた半導体層を備えながら、半導体層に影響されずに画素電極を形成できることで画質の向上が図られた表示装置を提供する。

【解決手段】薄膜トランジスタTrとこれに接続された透明画素電極23とを基板3上に配列形成してなる表示装置において、薄膜トランジスタのソース/ドレイン13sdが形成された基板3上に、絶縁性の隔壁層15が設けられ、隔壁層には薄膜トランジスタのチャネル部に対応する位置に第1開口15aが設けられると共に、透明画素電極の形成領域に対応する位置に第2開口15bが設けられている。第1開口底部には薄膜トランジスタの活性層を構成するチャネル部半導体層17chを設け、第2開口底部の半導体層17は除去する。隔壁層および半導体層17が形成された基板上を覆う絶縁膜21上に、第2開口に重ねて透明画素電極23を設ける。

(もっと読む)

TFT平坦化膜形成用組成物及び表示装置

【課題】比較的低温の焼成温度でTFT素子上に低誘電率の平坦化膜を形成することが可能なTFT平坦化膜形成用組成物、及びそのような平坦化膜を有する表示装置を提供する。

【解決手段】本発明に係るTFT平坦化膜形成用組成物は、(A)シロキサン樹脂、(B)重合促進剤、及び(C)有機溶剤を含有する。(B)重合促進剤としてはオニウム塩が好ましく、その含有量は、(A)シロキサン樹脂のSiO2換算質量に対して120〜1000質量ppmであることが好ましい。

(もっと読む)

配線の作製方法及び表示装置の作製方法

【課題】配線の凹凸やコンタクト不良を大幅に低減した配線の作製方法を用いることによって半導体装置の信頼性を向上させること。

【解決手段】層間絶縁膜207に設けられた開口部に液滴吐出法を用いてノズル208から導電性組成物が分散された液滴209を滴下し配線210を形成する。さらに、加熱処理を行うことで配線210をリフローする。これにより、配線表面を平坦化し、且つ配線のコンタクト不良を改善することができる。

(もっと読む)

電気光学装置、電気光学装置の製造方法、および投射型表示装置

【課題】コンタクトホールを埋める工程を利用して、隣接する画素電極の間に発生する凹部を平坦化した電気光学装置、その製造方法、およびかかる電気光学装置を用いた投射型表示装置を提供する。

【解決手段】電気光学装置において、画素電極9aは、下層側に島状に形成された第1電極91aと、第1電極91a上に島状に形成された上層側の第2電極92aとによって構成されている。第1電極91aの上層には絶縁膜73が積層され、かかる絶縁膜73によって、コンタクトホール72b内の凹部は完全に埋められ、隣接する第1電極91aの間も埋められている。従って、絶縁膜73の表面と、第1電極91aにおいて絶縁膜73から露出している表面とは連続した平坦面を構成しており、かかる平坦面上に第2電極72aが形成されている。

(もっと読む)

半導体装置の製造方法および電気光学装置

【課題】非晶質シリコン層を改質して得られたポリシリコン層には突起部分が発生する。ゲート絶縁層中に突起があると、この突起部分に電界が集中し、絶縁破壊が生じる。電解還元水は、酸化シリコン層をエッチングせず、ポリシリコン層をエッチングする性質がある。そこで酸化シリコン層を除去した後、電解還元水をスラリーとして用いてCMP法を用いる技術があるが、この場合、ポリシリコン層全面がCMP法により薄層化されてしまうという課題がある。

【解決手段】自然酸化シリコン層304を残した状態で電解還元水をスラリー107として用いてCMP工程を行う。機械的効果によりポリシリコン層303の突起上にある自然酸化シリコン層304は除去され、突起領域のみ電解還元水でエッチングが進みポリシリコン層303は平坦化される。そして、平坦部は自然酸化シリコン層304により保護され、薄層化は抑制される。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体層の結晶欠陥が低減されたSOI基板の作製方法を提供する。

【解決手段】単結晶半導体基板と、単結晶半導体基板から分離した単結晶半導体層が設けられた半導体基板と、の表面に、ハロゲンを含有する酸化膜を形成することで、基板表面又は内部に存在する不純物を減少させる。また、半導体基板上に設けられた単結晶半導体層に、レーザ光を照射することで、単結晶半導体層の結晶性を向上させ、平坦性を回復する。

(もっと読む)

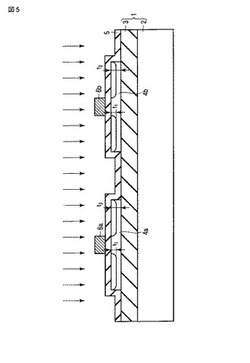

マルチゲート型電界効果トランジスタおよびその製造方法

【課題】平坦化工程を行っても、金属汚染を防止することのできるマルチゲート型電界効果トランジスタおよびその製造方法を提供することを可能にする。

【解決手段】基板2上に並列するように設けられた第1導電型の複数の半導体層6と、複数の半導体層のそれぞれに、離間して設けられた第2導電型のソース/ドレイン領域60a、60bと、複数の半導体層のそれぞれに、ソース領域とドレイン領域との間に設けられるチャネル領域と、チャネル領域のそれぞれの上面に設けられた保護膜8と、チャネル領域のそれぞれの両側面に設けられたゲート絶縁膜9と、チャネル領域のそれぞれの両側面にゲート絶縁膜を挟むように設けられるとともにチャネル領域のそれぞれの上面に保護膜を挟むように設けられた金属元素を含む複数のゲート電極10と、複数のゲート電極のそれぞれの側面を覆うように基板上に設けられた層間絶縁膜20と、複数のゲート電極のそれぞれの上面を共通に接続する接続部23と、接続部に接続されたゲート配線24と、を備えている。

(もっと読む)

61 - 80 / 237

[ Back to top ]