Fターム[5F140AA05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 相互コンダクタンスの向上 (502)

Fターム[5F140AA05]に分類される特許

21 - 40 / 502

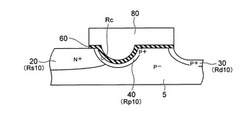

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【目的】水素終端よりも強い界面終端構造を有する半導体装置を提供することを目的の1つとする。

【構成】実施形態の半導体装置は、絶縁膜とSi半導体部とを備えている。絶縁膜は、酸化物と窒化物と酸窒化物とのいずれかを用いて形成される。Si半導体部202は、前記絶縁膜下に配置され、硫黄(S)とセレン(Se)とテルル(Te)とのうち少なくとも1種の元素が前記絶縁膜との界面に存在する、シリコン(Si)を用いて形成される。

(もっと読む)

半導体装置

【課題】十分な電流を流すことのできるトランジスタを備えた半導体装置を提供することを可能にする。

【解決手段】一実施形態の半導体装置は、半導体基板と、半導体基板上に設けられ、上面および側面が鞍形状を形成し、上面における鞍点を含む領域における第1方向の両端に凸部をそれぞれ有する半導体領域と、凸部の上面を除いた半導体領域の上面と、第1方向に沿った側面と、第1方向に直交する第2方向に沿った、上面における鞍点を含む領域側の前記凸部の側面との上に設けられたゲート絶縁膜と、ゲート絶縁膜の上に設けられたゲート電極であって、上面における鞍点を含む領域の直上に設けられた本体部と、本体部に接続され半導体領域の第1方向に沿った側面を覆う脚部と、を有し、脚部の第1方向における長さが上面における鞍点を含む領域の直上に設けられた本体部の第1方向における長さよりも長くなるように構成されたゲート電極と、ゲート電極の両側の半導体基板に設けられた第1および第2不純物領域と、を備えている。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜-半導体構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図り、界面準位密度の低い良好なゲート酸化膜/半導体界面が形成された半導体装置、およびそれを形成する重水素処理装置およびその作製方法を提供する。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化金属膜から放出される窒素がゲート絶縁膜に到達することを抑制する。

【解決手段】この半導体装置は、半導体基板100、第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び第1ゲート電極を備えている。第1ゲート絶縁膜110は半導体基板100上に形成されており、酸化シリコン又は酸窒化シリコンよりも比誘電率が高い材料から構成されている。シリコン含有第2ゲート絶縁膜122は、第1ゲート絶縁膜110上に形成されている。第1ゲート電極はシリコン含有第2ゲート絶縁膜122上に形成されており、窒化金属層124を有している。第1ゲート絶縁膜110、シリコン含有第2ゲート絶縁膜122、及び窒化金属層124は、pMOSFETの一部を構成している。

(もっと読む)

電界効果型トランジスター

【課題】ダイヤモンドFETにおいて、ドレイン電流特性を改善すること。

【解決手段】ダイヤモンド結晶層1の上に、高濃度ホウ素ドープダイヤモンド薄膜層102を成長する(図1(a))。次に、ソース電極およびドレイン電極として、Ti層131A、131B、Au層132A、132Bを順に蒸着する(図1(b))。次に、400℃でアニールを行いTiをダイヤモンドと反応させて、TiC層133A、133Bを形成する(図1(c))。最後に、ゲート部にAl2O3膜141を形成し、その上にAlゲート電極42を蒸着する(図1(d))。作製したダイヤモンドFETのドレイン電流特性は、ゲート電圧−3Vにおける最大ドレイン電流密度が600mA/mmとなり、従来技術による場合の約6倍に増加した。温度依存性に関しては、従来技術では室温から150℃付近でドレイン電流密度は急激に減少したが、本発明では900℃まで安定して動作した。

(もっと読む)

マイクロローディング効果を軽減するためのSiGe埋め込みダミーパターンを備えたSiGe装置

【課題】SiGe装置を取り囲んで、SiGeのエピタキシャル成長時にマイクロローディング効果を軽減できるように特別に設計されたSiGe埋め込みダミーパターンを備えた改良されたSiGe装置を提供する。

【解決手段】マイクロローディング効果を軽減するためのダミーパターンを備えた半導体装置は、内部領域200と外部領域400の間に中間環状領域300が設けられた半導体基板1と、基板上、内部領域200に設けられたSiGe装置100と、基板上、中間環状領域300に設けられた複数のダミーパターン20とを含む。複数のダミーパターン20のうち少なくとも1つがSiGeを含む。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極GE2の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極GE2側に位置する側壁部において、第1の斜面と、第1の斜面と交差する第2の斜面と、を有する。このように、溝g2の形状をΣ形状とすることで、pチャネル型電界効果トランジスタのチャネル領域に加わる圧縮歪みを大きくすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物電極の界面抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態によればn型半導体上に硫黄を含有する硫黄含有膜を堆積し、硫黄含有膜上に第1の金属を含有する第1の金属膜を堆積し、熱処理によりn型半導体と第1の金属膜を反応させて金属半導体化合物膜を形成するとともに、n型半導体と金属半導体化合物膜との界面に硫黄を導入することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体基板、絶縁ゲート型電界効果トランジスタおよび半導体基板の製造方法

【課題】絶縁ゲート型P−HEMT構造において、良好なトランジスタ性能を実現する。

【解決手段】ベース基板、第1結晶層、第2結晶層および絶縁層をこの順に有し、第1結晶層と第2結晶層との間、または、ベース基板と第1結晶層との間に位置する第3結晶層をさらに有し、第2結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層は、ドナーまたはアクセプタとなる第1原子を含み、第3結晶層がドナーとなる第1原子を含む場合、第2結晶層が、アクセプタとなる第2原子を含み、第3結晶層がアクセプタとなる第1原子を含む場合、第2結晶層が、ドナーとなる第2原子を含む半導体基板。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

歪チャネルを有するMOSトランジスタを製造する方法

【課題】歪チャネルを有するMOS トランジスタを製造するための比較的簡単な方法を提供する。

【解決手段】歪チャネルを有するMOS トランジスタ(M) を製造する方法は、(a) 半導体基板(10)の表面に、ソース領域及びドレイン領域とMOS トランジスタを囲む絶縁領域(22)に部分的に延びる絶縁された犠牲ゲートとを備えたMOS トランジスタを形成するステップと、(b) 犠牲ゲートの上面と略同一の高さの上面を有する絶縁層を形成するステップと、(c) 犠牲ゲートを除去するステップと、(d) 露出した絶縁領域(22)の少なくとも上部分をエッチングしてトレンチを形成するステップと、(e) 半導体基板(10)を歪ませることが可能な材料(24)をトレンチに充填するステップと、(f) 犠牲ゲートの除去によって空いた空間にMOS トランジスタの絶縁ゲート(12)を形成するステップとを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加するシリコン混晶層を活性領域に設けた半導体装置において、電流駆動能力の向上とリーク電流の低下と図れるようにする。

【解決手段】半導体装置は、シリコンからなる半導体基板10に形成され、周囲を素子分離領域11により囲まれてなる第2の活性領域10bと、該第2の活性領域10b及び素子分離領域11の上に、ゲート絶縁膜13を介在させて形成されたゲート電極14とを有している。第2の活性領域10bには、ゲート電極14の両側方の領域が掘り込まれてなるリセス領域19cにp型シリコン混晶層21が形成されており、該p型シリコン混晶層21における素子分離領域11と接触する接触位置の上端21bは、第2の活性領域10bの上面におけるゲート絶縁膜13の下側部分よりも低い。

(もっと読む)

21 - 40 / 502

[ Back to top ]