Fターム[5F140AA25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 高耐圧化 (661)

Fターム[5F140AA25]に分類される特許

21 - 40 / 661

化合物半導体装置及びその製造方法

【課題】GaとSiとの反応を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、Si基板1と、Si基板1の表面に形成されたSi酸化層3と、Si酸化層3上に形成され、Si酸化層3の一部を露出する核形成層2と、Si酸化層3及び核形成層2上に形成された化合物半導体積層構造9と、が設けられている。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】ノーマリオフ型のHEMT構造を有し、かつ優れたデバイス特性を有する窒化物半導体装置およびその製造方法を提供する。

【解決手段】窒化物半導体装置は、窒化物半導体からなる電子走行層3と、電子走行層3に積層され、電子走行層3とはAl組成が異なり、Alを含む窒化物半導体からなる電子供給層4と、電子供給層4と電子走行層3との界面に連続する界面を有し、電子走行層3上に形成された酸化膜11と、酸化膜11を挟んで電子走行層3に対向するゲート電極8とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

電界効果トランジスタ

【課題】高耐圧性をより確実に実現することができる電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、前記キャリア走行層上に形成され、前記キャリア走行層とは反対の導電型を有し、前記キャリア走行層内部に到る深さまで形成されたリセス部によって分離したキャリア供給層と、前記分離した各キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記分離した各キャリア供給層上にわたって前記リセス部内における前記キャリア走行層の表面を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備え、前記リセス部の前記キャリア供給層上面からの深さが、前記キャリア供給層の層厚より大きく200nm以下である。

(もっと読む)

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

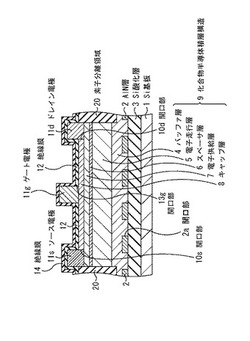

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

窒化物系半導体装置

【課題】ダイオード部とトランジスタ部の面積比率を自由に設定することが可能な窒化物系半導体装置を提供することを目的とする。

【解決手段】第1HEMT部30及び第2HEMT部31から成るトランジスタ部1と、第1電極24と電気的に短絡された第1ショットキー電極28及び第1ゲート電極26と電気的に第2ショットキー電極29から成るダイオード部2と、を備えて構成されている。また、第1電極24と第2電極25との間の領域に第1電極24に沿って、第1ゲート電極26及び第1ショットキー電極28が交互に形成され、かつ、第2電極25に沿って、第2ゲート電極27及び第2ショットキー電極29が交互に形成されている。さらに、第1ゲート電極26と第2ゲート電極27とは、対向して形成されており、第1ショットキー電極28と第2ショットキー電極29とは対向して形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】同一平面上に形成された2つの配線が互いにショートするのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置する縦型のゲート電極用ダミーピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央に位置するゲート電極用ダミーピラー(1a)へ給電するために第1の方向(X)へ延在して配置されたゲート給電配線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつゲート給電配線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置

【課題】素子面積を増加させることなく、高耐圧の半導体装置を実現させる。

【解決手段】第1方向に沿ったソース領域、ゲート電極を挟んでソース領域とは反対側に第1方向に沿ったドレイン領域、一部がゲート電極下面と対向しソース領域とドレイン領域との間に設けた絶縁体層、一部がゲート電極下面と対向し絶縁体層よりもソース領域側に設けたベース領域、一部が第2方向に第2長さを有してゲート電極下面と対向し、ベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子活性領域部、ゲート絶縁膜の上に設けたゲート電極、ソース領域、一部がゲート電極下面と対向して設けた絶縁体層、一部がゲート電極下面と対向して絶縁体層よりもソース領域側に設けたベース領域、一部が第1方向に第2長さよりも短い第1の長さを有してゲート電極下面と対向してベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子終端領域部と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧トランジスタの低濃度不純物拡散層がコンタミネーションから保護されて、半導体装置の特性を安定化できるようにする。

【解決手段】基板1の上に、ゲート絶縁膜3a及びゲート電極4aを順次形成し、ゲート電極4aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に低濃度不純物拡散層5aを形成する。続いて、ゲート電極4aの上から該ゲート電極4aの側方を通って低濃度不純物拡散層5aの上の一部までを連続して覆うように不純物拡散抑制膜7aを形成する。続いて、ゲート電極4a及び不純物拡散抑制膜7aをマスクとして基板1に不純物注入を行うことにより、基板1の上部におけるゲート電極4aの側方に、低濃度不純物拡散層5aよりも不純物濃度が高い高濃度不純物拡散層8aを形成する。その後に、不純物拡散抑制膜7aを残存させた状態で基板1に対して加熱処理を行う。

(もっと読む)

半導体装置及びその駆動方法

【課題】閾値電圧(Vth)の経時的に変動する現象を抑制することで、高信頼性を保つことが可能なMIS型半導体装置を提供する。

【解決手段】本発明は、半導体ボディ領域とゲート絶縁膜の間に半導体ボディ領域とは逆の半導体極性のチャネル層を有するMIS型半導体装置であり、当該半導体装置のフラットバンド電圧Vfbを−10ボルト以下とすることにより、半導体ボディ領域表面近傍に誘起されるキャリア電荷密度を当該半導体装置の動作保証範囲内において所定量以下に抑制する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

横型半導体装置

【課題】抵抗性フィールドプレート部のレイアウトの自由度を高める技術を提供すること。

【解決手段】コーナー範囲に設けられている中間抵抗性フィールドプレート部34は、カソード領域28とアノード領域23の間で往復を繰返して形成されている。直線範囲に設けられている中間抵抗性フィールドプレート部34も、カソード領域28とアノード領域23の間で往復を繰返して形成されている。コーナ範囲に設けられている中間抵抗性フィールドプレート部34と直線範囲に設けられている中間抵抗性フィールドプレート部34は接していない。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】ウルツ鉱型結晶構造の半導体を用いた電界効果トランジスタで、電極との接触抵抗を高くすることなく、バンドギャップエネルギーのより大きな半導体から障壁層が構成できるようにする。

【解決手段】ゲート電極104を挟んで各々離間して障壁層103の上に接して形成された2つの電流トンネル層105と、各々の電流トンネル層105の上に形成された2つのキャップ層106とを備える。電流トンネル層105の分極電荷は、障壁層103の分極電荷よりも大きい。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

電界効果型トランジスタ

【課題】ゲート電極のドレイン端の電界を緩和し、ゲート絶縁膜の破損を低減する。

【解決手段】窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップエネルギーが大きい窒化物半導体で形成された電子供給層112と、チャネル層108の上方に形成されたソース電極116およびドレイン電極118と、チャネル層108の上方に形成されたゲート電極120と、チャネル層108の上方に形成され、チャネル層108からホールを引き抜くホール引抜部126と、ゲート電極120およびホール引抜部126を、電気的に接続する接続部124と、を備える電界効果型トランジスタ100。

(もっと読む)

半導体装置

【課題】低オン抵抗特性を有するパワーMOSトランジスタのスイッチング特性を、従来以上に改善した高効率パワーMOSトランジスタを実現する。

【解決手段】Finger形状電極からなるソース電極8とドレイン電極9の間をFinger形状電極の一方の端部GE1から他方の端部GE2まで延在するゲート電極6と、層間絶縁膜7に形成されたコンタクトホールを介してゲート電極6の端部GE1、GE2とそれぞれ接続されるゲート引き出し電極と、前記層間絶縁膜7上を被覆するパッシベーション膜12と、該パッシベーション膜12の開口に露出する前記ゲート引き出し電極の一部となるゲート接続電極G1、G2と、該ゲート接続電極G1、G2に形成された突起電極25を備える半導体チップ100を、該突起電極25を介して、BGA基板200の表面201に形成された低抵抗のゲート電極シャント用基板配線23に接続する。

(もっと読む)

21 - 40 / 661

[ Back to top ]