Fターム[5F140AA25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 高耐圧化 (661)

Fターム[5F140AA25]に分類される特許

41 - 60 / 661

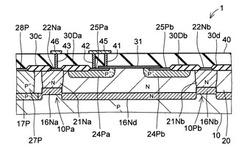

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

半導体装置とその製造方法

【課題】 半導体装置を高耐圧化する技術を提供することを目的とする。

【解決手段】 半導体装置100は、p型の埋込み層26と、p型埋込み層26上に設けられており、ヘテロ接合面3が構成されている窒化物半導体のヘテロ接合層32を備えている。p型埋込み層26は、ソース電極10側からドレイン電極2側に向けて厚みが減少する厚み減少部24を有している。厚み減少部24では、ソース電極10側の減少開始点14からドレイン電極2側の減少終了点16までの長さ24bが、減少開始点14における厚み24aよりも長い。

(もっと読む)

高耐圧半導体装置

【課題】容量素子の直列接続を形成するフィールドプレートにおいて、導電性薄膜の間の層間絶縁膜の厚さを増加させても、容量素子による電圧の分圧を均一にできる高耐圧半導体装置を提供する。

【解決手段】本発明の高圧半導体装置は、第1導電型の第1半導体領域と、第1半導体領域と隣接して形成された第2導電型の第2半導体領域と、第2の半導体領域とで第1導電型の第1半導体領域を挟んで形成された、第1導電型の第3半導体領域と、第1半導体領域上に形成された第1絶縁膜上に所定の周期で配列された第1導電膜と、第1導電膜上に形成された第2絶縁膜に、平面視で第1導電膜の離間領域と重なり、かつ当該離間領域の両側に配置されている第1導電膜と一部が重なる位置に周期的に配置されている第2導電膜とを備え、第2導電膜は、第1導電膜の離間領域と対向する領域に第1凸部が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低減し、かつ高耐圧で駆動することが可能な半導体装置を提供する。

【解決手段】当該高耐圧トランジスタは、第1の不純物層PEPと、第1の不純物層PEPの内部に形成される第2の不純物層HVNWと、第2の不純物層HVNWを挟むように、第1の不純物層PEPの内部に形成される1対の第3の不純物層OFBおよび第4の不純物層PWと、第3の不純物層OFBから、第2の不純物層HVNWの配置される方向へ、主表面に沿って突出するように、第1の不純物層PEPの最上面から第1の不純物層PEPの内部に形成される第5の不純物層OFB2と、第2の不純物層HVNWの最上面の上方に形成される導電層GEとを備える。第4の不純物層PWにおける不純物濃度は、第3および第5の不純物層OFB,OFB2における不純物濃度よりも高く、第5の不純物層OFB2における不純物濃度は、第3の不純物層OFBにおける不純物濃度よりも高い。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑制しつつ高耐圧の半導体装置を得る。

【解決手段】第1導電型の第1半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度を有し、MOSトランジスタのドレイン領域として機能する。また、第1導電型の第2半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度より小さい第2の不純物濃度を有し、第1半導体層と接続されるように配置されてMOSトランジスタのドリフト層として機能する。素子領域及び素子終端領域は、第1方向と直交する第2方向の幅が同一であり、第2方向に沿った断面に関し、素子終端領域における第2半導体層の幅は、素子領域における第2半導体層の幅よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ横型パワーMOSFETにおいて、装置の信頼性を高めること。

【解決手段】半導体基板1の表面層にトレンチ5を形成する。トレンチ5は、半導体基板1の表面層を第1メサ領域41と第2メサ領域42に分割し、かつ第1メサ領域41と第2メサ領域42を交互に配置させる。第1メサ領域41および第2メサ領域42は、それぞれソース電流およびドレイン電流の引き出しをおこなう。第2メサ領域42は、半導体基板1からの深さが、第1メサ領域41よりも深くなっている。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】3次元形の半導体素子において、オン抵抗をより効果的に低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、ドレイン層と、ドレイン層内に選択的に設けられたドリフト領域と、ドリフト領域内に選択的に設けられたベース領域と、ベース領域内に選択的に設けられたソース領域と、ソース領域又はドレイン層の少なくとも一方の内部に、ソース領域又はドレイン層の少なくとも一方に選択的に設けられた第1,第2の金属層と、ドレイン層の表面に対して略平行な方向に、ソース領域の一部から、ソース領域の少なくとも一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、第1の金属層に接続されたソース電極と、ドレイン層又は第2の金属層に接続されたドレイン電極と、を備える。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

高耐圧電界効果トランジスタ

【課題】高耐圧電界効果トランジスタの素子面積を増大させること無しに、十分に低いオン抵抗を得る。

【解決手段】半導体基板101のn型領域102内に、チャネル形成領域102aを挟んでドレイン低濃度領域103およびソース低濃度領域104を形成し、ドレイン高濃度領域105およびソース高濃度領域106を形成し、ゲート酸化膜109を形成し、該ゲート酸化膜109の端部および低濃度領域103,104を含む領域にフィールド酸化膜110を形成し、さらにゲート酸化膜109からフィールド酸化膜110の端部にかけてゲート電極111を形成した高耐圧pMOSトランジスタにおいて、ゲート電極111とドレイン高濃度領域105との間に、フィールド酸化膜110が形成されていない非酸化領域112を設ける。製造時に、ドレイン低濃度領域103の不純物がフィールド酸化膜110に取り込まれ難くなるので、オン抵抗の増加が抑制される。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜-半導体構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図り、界面準位密度の低い良好なゲート酸化膜/半導体界面が形成された半導体装置、およびそれを形成する重水素処理装置およびその作製方法を提供する。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、パワー半導体素子を提供する。

【解決手段】半導体基材内に第1の伝導型のドリフト領域2と、半導体基材内にドリフト領域2に隣接して配置され半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3の間に配置された蓄積誘電体4と、基材領域8と、基材領域8から分離され蓄積誘電体4に隣接するドレイン領域5と、基材領域8によりドリフト領域2から分離されるソース領域9と、ゲート誘電体16により半導体基材から絶縁されソース領域9からドリフト領域2に到るまで基材領域8に隣接して伸びたゲート電極15と、ドレイン領域5と接したドレイン電極11と、ドレイン領域5と相補的にドープされた半導体領域27とを含み、半導体領域27はドレイン電極11とドリフト領域2の間に配置されドレイン電極11に隣接する。

(もっと読む)

半導体装置

【課題】高耐圧MOS型トランジスタなどの高耐圧半導体装置における耐圧を向上させ、またドレインオフセット層などの内部電界強度が経時的に変化し、耐圧が変動することを防止する。

【解決手段】半導体装置、例えば高耐圧MOS型トランジスタは、半導体層2、それと反対導電型の低不純物濃度ソース層3および低不純物濃度ドレイン層4、高不純物濃度ソース層5および高不純物濃度ドレイン層6、ドレイン側オフセット絶縁膜8a、ソース側オフセット絶縁膜8b、ゲート絶縁膜9、ゲート電極10を有する。ゲート電極10の表面には表面絶縁膜20が形成されており、ドレイン側オフセット絶縁膜8a上の、ゲート電極10と隣接する領域には、少なくとも一部が表面絶縁膜20と接する状態で形成された第1導電性プレート11aが設けられている。

(もっと読む)

41 - 60 / 661

[ Back to top ]