Fターム[5F140AA25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 高耐圧化 (661)

Fターム[5F140AA25]に分類される特許

81 - 100 / 661

半導体製造方法および半導体装置

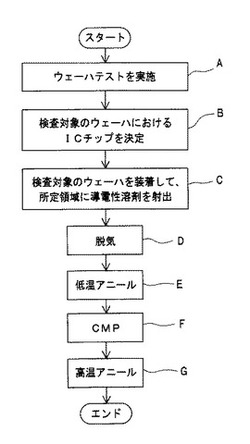

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置

【課題】半導体装置の耐圧を向上させる。

【解決手段】半導体装置10は、p型半導体基板1、p型半導体基板1内に設けられたn型ドリフト領域3、及びn型ドリフト領域3内に設けられたp型ボディ領域4を含む。p型ボディ領域4の側面とn型ドリフト領域3とのpn接合部22の上方に、そのpn接合部22に沿って、環状のゲート電極6が設けられる。このゲート電極6の一部を挟んでn型ドリフト領域3内及びp型ボディ領域4内にそれぞれ、n型ドレイン領域7及びn型ソース領域8が設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電圧の閾値電圧がばらつくことを抑制することができると共に、チャネル抵抗を低減させることができる半導体装置を提供する。

【解決手段】ベース領域4、ソース領域6、ドレイン領域7の不純物濃度を均一とし、第1、第2トレンチ8a、8bをベース領域4よりも浅く形成する。このような半導体装置では、ベース領域4、ソース領域6、ドレイン領域7の不純物濃度が均一とされているため、ゲート電圧の閾値電圧がばらつくことを抑制することができ、また、ソース領域6およびドレイン領域7を深くすることによりチャネル領域を有効に活用でき、チャネル抵抗を低減することができる。さらに、第1、第2トレンチ8a、8bをベース領域4より浅く形成しているため、ベース領域4のうち第1、第2トレンチ8a、8bより深く形成されている部分にはチャネル領域が形成されず、ソース領域6から深さ方向に電流が流れることを抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元構造のパワーMOSトランジスタやIBGTの破壊耐量を改善する。

【解決手段】一つの実施形態の半導体装置には、N+基板1に溝21が設けられ、溝21に積層形成されるN層2、N−層3、P層4、及びN+層5が溝21を覆うように設けられる。N+層5に、N+基板1に対して垂直方向では一部がN+層5を貫通してP層4表面が露呈され、N+基板1に対して水平方向では一部がN+層5を貫通してP層4側面が露呈するように溝22が設けられ、溝22にP+層6が溝22を覆うように設けられる。N+基板1に対して垂直方向では、N+層5を貫通してP層4表面が露呈され、N+基板1に対して水平方向では、P層4を貫通して一端でN−層3側面が露呈し、他端でN+層5側面が露呈し、P+層6の間及び側面と離間して配置形成される溝23が設けられる。溝23に、トレンチゲート11が溝23を覆うように設けられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーデバイスの高耐圧とオン抵抗の低減とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板101内のソース領域107A、ドレイン領域107B、及びドレイン領域107Bに接したドリフト領域105と、ソース領域107A及びドレイン領域107B間のドリフト領域105内のSTI絶縁層I−2と、STI絶縁層I−2上、ドリフト領域105上、並びに、ソース領域107A及びドレイン領域107B間のチャネル領域上のゲート電極110とを備える。STI絶縁層I−2は、第1及び第2のトレンチの内面上の第1の酸化膜102及び窒化膜103と、第1及び第2のトレンチを満たす窒化膜103上の第2の酸化膜104とを備える。第2のトレンチは、第1のトレンチ内に形成され、第1のトレンチの底面よりも低い底面を有し、第1のトレンチの幅よりも狭い幅を有する。

(もっと読む)

半導体装置

【課題】MOSFETの耐圧を向上させる。

【解決手段】半導体基板上に形成された平面形状が円形の給電部1pと給電部1pを中心としたリング状のガードリング領域1gとの間に、給電部1pを中心として放射状に延在するゲート電極G1を給電部1pを中心とする円周上に並べて複数配置し、前記円周上で隣り合うゲート電極G1同士の間にソース領域S1またはドレイン領域D1を形成する。これにより、ゲート電極G1の下部のウエルとソース領域S1とドレイン領域D1との間に寄生バイポーラトランジスタが形成されることを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明の実施形態は、電気抵抗を低減させることができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1導電型のチャネル形成領域と、第2導電型の第1オフセット領域と、前記第1オフセット領域の表面に埋め込まれている第1絶縁膜領域と、前記第1オフセット領域と前記第1絶縁膜領域との間に設けられた第1ライナ層と、前記第1絶縁膜領域を挟んで前記チャネル形成領域とは反対側に形成され、前記第1オフセット領域よりも不純物濃度の高い第2導電型の第1半導体領域と、前記チャネル形成領域を挟んで前記第1半導体領域とは反対側に形成され、前記第1オフセット領域よりも不純物濃度の高い第2導電型の第2半導体領域と、前記チャネル形成領域上及び前記第1オフセット領域上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、窒化物系半導体装置を提供することを目的とする。

【解決手段】ショットキー電極30が、ソース電極24とドレイン電極26とが対向する領域の、ソース電極24とドレイン電極26とが対向する方向と略直交する方向にゲート電極28と並んで形成されている。ショットキー電極30は、AlGaN層20とショットキー接合されており、ソース電極24に電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFET動作からIGBT動作に切り替わるときのコレクタ電圧を上昇させずに、アバランシェ耐量を向上させる半導体装置を提供する。

【解決手段】P-型基板の表面部に形成されたN型リサーフ領域と、P型ベース領域と、N+型エミッタ/ソース領域105と、ゲート絶縁膜と、N型リサーフ領域内に形成されたN+型ドレイン領域109及びP+型コレクタ領域108と、ゲート絶縁膜上に形成されたゲート電極107と、P+型コレクタ領域108及びN+型ドレイン領域109に電気接続されたコレクタ/ドレイン電極と、N+型エミッタ/ソース領域105に電気接続されたエミッタ/ソース電極と、N型リサーフ領域内であってP型ベース領域及びN+型ドレイン領域109とは離隔しP+型コレクタ領域108の側面と対向して形成された、N型リサーフ領域よりも高いキャリア濃度のバッファ領域114とを備える半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】ゲートリセスの深さの制御を安定的に行なえるようにして、ノーマリオフ動作のデバイスを安定的に作製できるようにする。

【解決手段】半導体装置を、基板1の上方に設けられたGaN電子走行層2と、GaN電子走行層2上に設けられた第1AlGaN電子供給層3と、第1AlGaN電子供給層3上に設けられたAlN電子供給層4と、AlN電子供給層4上に設けられた第2AlGaN電子供給層5と、第2AlGaN電子供給層5及びAlN電子供給層4に設けられたゲートリセス9と、ゲートリセス9に設けられたゲート電極12とを備えるものとする。

(もっと読む)

窒化物系化合物半導体および窒化物系化合物半導体素子

【課題】長期信頼性が高い窒化物系化合物半導体および窒化物系化合物半導体素子を提供すること。

【解決手段】アルミニウム原子、ガリウム原子、インジウム原子およびボロン原子から選択される1以上のIII族原子と、窒素原子とを含む窒化物系化合物半導体であって、添加物としてドープした金属原子とガリウム格子間原子とが複合体を形成している。好ましくは、前記添加物は鉄またはニッケルである。好ましくは、前記添加物のドープ濃度は、前記ガリウム格子間原子の濃度と同程度である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】小型化できると共に安定的に高耐圧化できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、P型の半導体基板1と、半導体基板1の表面のP−型の拡散領域2a,2bと、拡散領域2bに隣接した本体部、及び、拡散領域2bと拡散領域2bの下方の半導体基板1との間に挟まれた外縁部を有するN型の拡散領域3と、x方向に並んで拡散領域2a,2bに形成されたN+/N++型のソース領域7及びドレイン領域8,9と、第1ゲート電極11と、を有する第1のMOSトランジスタ100と、拡散領域3の外縁部の上方の拡散領域2bに形成され、一端がx方向に延びて拡散領域3の本体部と接続している、N+型の拡散領域5を有する半導体素子Sと、を備える。第1のMOSトランジスタ100と半導体素子Sの拡散領域5とは、y方向に並んで、拡散領域2bで電気的に分離されている。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧を向上した半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。第1導電形の第1半導体領域は、第1部分と第1方向に延出した第2部分とを有する。第1導電形の第2半導体領域は、第1部分上の第3部分と第2部分と隣接する第4部分とを有する。第2導電形の第3半導体領域は、第3部分上の第5部分と第4部分と隣接する第6部分とを有する。第1導電形の第4半導体領域は、第5部分上で第6部分と隣接する。ゲート領域は、第2半導体領域、第3半導体領域及び第4半導体領域を第2方向に貫通するトレンチ内に設けられる。ゲート絶縁膜は、トレンチ内壁とゲート領域との間に設けられる。第2導電形の電界緩和領域は、第3部分と第5部分との間に設けられ、第3半導体領域よりも不純物濃度が低い。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、素子面積を縮小可能で高耐圧なMOS型電界効果トランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】

本実施形態の半導体装置100は、半導体基板10と、半導体基板10に設けられた素子分離領域14a,14bと、隣接する素子分離領域で区画された素子領域上に半導体基板10上に設けられたゲート絶縁膜12と、ゲート絶縁膜12上に設けられたゲート電極13と、ゲート電極13の直下近傍の素子領域表面に設けられたソース・ドレイン拡散領域11a,11bと、前記ソース・ドレイン拡散領域11a,11b上に設けられたコンタクトプラグ15a,15bとを備え、ゲート絶縁膜12のドレイン側の膜厚は、ゲート絶縁膜12のソース側の膜厚より厚いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタに係る半導体装置の高速動作を可能とする。

【解決手段】P型ウエル層3の表面に形成された複数の素子分離膜4の中央部に開口溝5を形成する。開口溝5の側壁から開口溝5の内側に向かってゲート絶縁膜6を介して延在するゲート電極7を形成する。ゲート電極7をマスクにしてセルフアラインでボロンの斜めイオン注入により開口溝5内のP型ウエル層3にP型ボディ層8を形成する。

ゲート電極7をマスクに砒素のイオン注入によりP型ボディ層8にN+型ソース層9を、同時に2つの素子分離膜4間のP型ウエル層3にN+型ドレイン層10を形成する。素子分離膜4の下方のP型ウエル層3にP型ボディ層8の端部からN+型ドレイン層10に延在するN−型ドリフト層を形成する。この際、P型ボディ層8の端部から開口溝5の側壁下部までの領域AのN−型ドレイン層11の幅をできるだけ小さくなるよう制御する。

(もっと読む)

81 - 100 / 661

[ Back to top ]