Fターム[5F140AA25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 高耐圧化 (661)

Fターム[5F140AA25]に分類される特許

141 - 160 / 661

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

高耐圧MOSトランジスタおよび半導体集積回路装置、高耐圧半導体装置

【課題】半導体基板上に他のCMOS素子と集積して形成される高耐圧MOSトランジスタの、工程数を抑制しながら、ドレイン耐圧特性を向上させる。

【解決手段】半導体基板21と、ゲート電極23と、第2の導電型のソース領域21Sと、第2の導電型のドレイン領域21Dと、ソースエクステンション領域21aと、ドレインエクステンション領域21bと、を含み、ソースエクステンション領域21aとドレインエクステンション領域21bとの間にはチャネル領域が形成され、ソース領域21Sおよびソースエクステンション領域21aの下方には第1のウェル21PWが、第1の導電型で、素子分離領域21Iの下端部を超える深さで形成され、第1のウェル21PWの下方には第2のウェル21DNWが第2の導電型で形成され、第1のウェル21PWおよび第2のウェル21DNWは、ドレインエクステンション領域21b、ドレイン領域21Dの下には形成されない。

(もっと読む)

トレンチ型パワーMOSトランジスタおよびその製造方法

【課題】パワーMOSトランジスタにおいて、高い降伏電圧、高い出力電流および高速の動作速度を備えるのみならず、水平構造を備えるために、CMOSの製造工程で製作された一般的な集積回路と同一のチップ上に整合させる。

【解決手段】本発明のトレンチ型パワーMOSトランジスタはゲート導電体312と、絶縁層310とを備えたトレンチ型ゲート領域を具備する。絶縁層310は、ゲート導電体312と井戸領域308との間で薄い側壁領域を形成しており、ゲート導電体312と二重拡散のドーピング領域306との間で厚い側壁領域を形成するとともに、ゲート導電体312と深井戸領域304との間で厚い最下部領域を形成している。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの高耐圧特性を維持しながらオン抵抗を低減する。

【解決手段】第1高濃度拡散層109及び第2高濃度拡散層108はそれぞれ第1導電型であり、平面視においてゲート電極106を介して互いに対向している。第1低濃度拡散層103は第1導電型であり、第1高濃度拡散層109を内側に含むように形成されている。第1高濃度拡散層109は、平面視でゲート電極106から離間しており、第1低濃度拡散層103は、平面視において第1高濃度拡散層109よりもゲート電極の近くまで形成されている。第1埋込層114は第1導電型であり、第1高濃度拡散層109の下方からゲート電極106に向けて延在している。第2埋込層112は第1導電型であり、第1埋込層114とゲート電極106とを接続している。

(もっと読む)

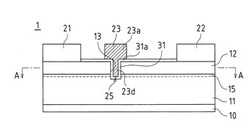

半導体装置

【課題】パワーデバイスとCMOSデバイスとを混載することができ、パワーデバイスのアバランシェ耐量及びESD耐量が高い半導体装置を提供する。

【解決手段】半導体基板11の上部にP型のウェル12を形成し、ウェル12にSTI13を選択的に設け、STI13の開口部14内にSTI13の側面13aに接するようにN+型のソース層17及びドレイン層18を相互に離隔して形成する。また、ソース層17とドレイン層18との間に、P+型のコンタクト層19を形成する。コンタクト層19はソース層17に接し、STI13からは離隔するように形成する。更に、ソース電極21をソース層17及びコンタクト層19に接続し、ドレイン電極22をドレイン層18に接続し、STI13上に側面13aに沿ってゲート電極23を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】 オン抵抗を増大させることなく、高耐圧化を実現させることが可能な半導体装置を実現する。

【解決手段】 P型の半導体基板1内には、P型ボディ領域3と、P型ボディ領域3に対して基板面に平行な方向に離間して形成されたN型ドリフト領域5と、N型ドリフト領域内のフィールド酸化膜11で分離された領域に形成された、N型ドリフト領域5より高濃度N型のドレイン領域8と、P型ボディ領域3内に形成された、N型ドリフト領域5より高濃度N型のソース領域6を備える。そして、P型ボディ領域3の一部底面に離散的に連結すると共に、それぞれが基板面に平行な方向に延伸し、各先端がドリフト領域5内に達するよう、N型ドリフト領域5より高濃度のP型埋め込み拡散領域4が形成される。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧で、特性の優れた半導体装置を提供する。

【解決手段】素子分離領域STIと、ウェルPWと、活性領域を横断するゲート電極Gと、ゲート電極の一方の側からゲート電極下方に入り込んで形成された低濃度ドレイン領域LDDと、ゲート電極の他方の側からゲート電極下方に入り込み、低濃度ドレイン領域とオーバーラップし、低濃度ドレイン領域より浅い、チャネル領域CHと、ゲート電極の他方の側に形成されたソース領域Snと、ゲート領域の一方の側に、ゲート電極から離間したドレイン領域Dnと、を有し、ゲート電極と高濃度ドレイン領域Dnとの間の中間領域の実効不純物濃度は、オーバーラップ領域の不純物濃度より高い。

(もっと読む)

半導体装置、半導体集積回路装置及び半導体装置の製造方法

【課題】高耐圧且つ低オン抵抗な半導体装置及びこれを含む半導体集積回路装置を歩留まり良く、安価に提供する。

【解決手段】第1導電型の半導体基板(1)と、前記第1導電型と反対の第2導電型であって前記半導体基板の表面側に形成されたソース領域(11)、低濃度ドレイン領域(12)及び高濃度ドレイン領域(13)と、前記半導体基板上に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極と、を備える半導体装置(10)であって、

前記ゲート電極は、前記低濃度ドレイン領域の少なくとも一部を覆うように形成され、且つ、前記低濃度ドレイン領域の上方において開孔(16)を有することを特徴とする半導体装置。前記低濃度ドレイン領域と高濃度ドレイン領域とは互いに隣接することが好ましい。

(もっと読む)

イオン注入及び側方拡散による炭化シリコンパワーデバイスの自己整列的な製造方法

【課題】自己整列した浅い注入領域及び深い注入領域を形成し、浅い注入領域の低い拡散率を有するn型ドーパントを比較的固定すると共に、深い注入領域の高い拡散率を有するp型ドーパントを十分に拡散させ、良く制御されたチャネルを形成するpベース領域をn型ソースの周りに形成して横型炭化シリコンパワーデバイスを製造する。

【解決手段】炭化シリコン基板内にマスクの開口部を通してp型ドーパントをイオン注入して深いp型注入領域を形成する。マスクの同じ開口部を通してn型ドーパントをイオン注入して前記p型注入領域と比較して浅いn型注入領域を形成する。その後、前記深いp型注入領域を前記浅いn型注入領域を囲む炭化シリコン表面まで、該埋め込まれた深いp型注入領域を該浅いn型注入領域を通って炭化シリコン基板表面まで縦方向に拡散させることなく、側方拡散させるのに十分な温度及び時間でアニールする。

(もっと読む)

半導体装置の製造方法

【課題】高耐圧な半導体装置の製造方法を提供する。

【解決手段】半導体層に対してマスクを用いて選択的にイオン注入を行い、半導体層に第1導電型の第1の半導体領域と、前記第1の半導体領域よりも第1導電型不純物濃度が低い第1導電型の第2の半導体領域とを同時に形成する工程と、第1の半導体領域上に第2導電型のソース領域を形成する工程と、第2の半導体領域上であってソース領域との間にゲート電極を挟む位置に第2導電型のドレイン領域を形成する工程と、半導体層におけるゲート電極とドレイン領域との間の表層部にドレイン領域に接しドレイン領域よりも不純物濃度が低い第2導電型のドリフト領域を形成する工程とを備えている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリセス構造を採用してノーマリーオフ動作を可能とするも、バラツキの小さい安定した閾値を有し、十分な高耐圧を実現する信頼性の高い化合物半導体装置を実現する。

【解決手段】電子走行層3と電子供給層4との間にi−AlNからなる中間層5を形成し、キャップ構造7上のゲート電極の形成予定部位に中間層5をエッチングストッパとして用いて開口11aを形成した後、中間層5の開口11aに位置整合する部位に熱リン酸を用いたウェットエッチングにより開口11bを形成して、開口11a,11bからなる開口11をゲート絶縁膜12を介して下部が埋め込み、上部がキャップ構造7上方に突出するゲート電極13を形成する。

(もっと読む)

半導体装置

【課題】バイポーラの高耐圧縦型PNPプロセスをベースにして、寄生PNPトランジスタに起因する漏洩電流の発生しない高耐圧IGBTを形成する。

【手段】P型半導体基板1に、IGBTのコレクタ電極15と電気的に接続するP+型コレクタ層8と、当該P+型コレクタ層8と連続するP+型埋め込み層4と、該P+型埋め込み層4の下層のN型埋め込み層2と、該P+型埋め込み層4と該N型埋め込み層2の間のN+型埋め込み層3とを形成する。また、N+型埋め込み層3の端部と一体となり、前記P型半導体基板1上に形成されたN型エピタキシャル層5の表面まで延在し、コレクタ電極15と電気的に接続されたN+型導電層7を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】形成する素子に要求される素子間耐圧や素子内部耐圧に応じたディープトレンチ膜を有する半導体装置を提供する。

【解決手段】P型のシリコン基板11上に、N+型埋め込み層12と、N型半導体層13と、が積層された基板10と、基板10にN+型埋め込み層12の形成位置よりも深く形成され、基板10内の素子形成領域内を区画するディープトレンチ20と、ディープトレンチ20の内壁に沿って形成される側壁酸化膜23,24と、ディープトレンチ20内を埋めるTEOS膜を含むディープトレンチ膜26と、ディープトレンチ膜26で区画される素子形成領域に形成されるLDMOSと、を備え、ディープトレンチ20は、N+型埋め込み層12の上面よりも浅い位置の境界深さまでの第1のディープトレンチ21と、境界深さから底部までの第1のディープトレンチ21よりも小さい開口径を有する第2のディープトレンチ22によって構成される。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有する第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタは、基板1、チャネル層3及びバリア層4と、バリア層4上にこの順で離間して設けられたソース電極6、ゲート電極7およびドレイン電極8とを備え、ソース電極6の直下に第1のn型不純物拡散領域12が設けられ、ドレイン電極8の直下に第2のn型不純物拡散領域13が設けられ、第2のn型不純物拡散領域の下側の前記チャネル層3および第2のn型不純物拡散領域の前記ゲート電極側の前記チャネル層3および前記バリア層4に第3のn型不純物拡散領域15が設けられる。第3のn型不純物拡散領域15は第2のn型不純物拡散領域13よりも低いn型不純物濃度を有し、ゲート電極とドレイン電極との間に電圧が印加されたときバリア層4およびチャネル層3においてその絶縁破壊強度を超える電界集中が生じることを抑制する。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの耐圧を高く保ちつつ、素子分離能力の低下を防ぐ。

【解決手段】基板102の一面のチャネル領域108において、ゲート幅方向に断続的に深さが変化するように形成されたトレンチ162内部を埋め込むように形成されたゲート電極122を含むトランジスタにおいて、ソース領域112およびドレイン領域113の下方には、それぞれ第1のオフセット領域106および第2のオフセット領域107が形成される。ここで、第1のオフセット領域106および第2のオフセット領域107は、それぞれ、素子分離絶縁膜110と接する領域における下端が素子分離絶縁膜110の下端よりも上方に位置するように形成されるとともに、トレンチ162端部の下方にも形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】

高温、長時間のアニールを必要とすることなく、低いオン抵抗を実現可能な高耐圧MOSトランジスタを含む半導体装置を提供する。

【解決手段】

半導体基板の高耐圧トランジスタ用第1導電型領域上にゲート電極を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第1のマスクをイオン注入マスクとして、ゲート電極を貫通する加速エネルギで第1導電型の不純物イオンを注入して、ソース領域で深く、ゲート電極下方で浅いチャネルドーズ領域を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第2のマスク及びゲート電極をイオン注入マスクとして第2導電型の不純物をイオン注入してソースエクステンション領域を形成し、半導体装置を製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置

【課題】高耐圧で大きな電流駆動能力をもつLOCOSオフセット型MOS型電界効果トランジスタを提供する。

【解決手段】LOCOSオフセット型MOS型電界効果トランジスタのドレイン側のオフセット領域に、LOCOS酸化膜を伴うN型第1低濃度ドレインオフセット領域5と、LOCOS酸化膜を伴わないN型第2低濃度ドレインオフセット領域6を設け、共にゲート電極で覆うように設けたので、N型第1低濃度ドレインオフセット領域5でオフセット領域にかかる電界を緩和し高耐圧を得て、N型第2低濃度ドレインオフセット領域6でオフセット領域のキャリアを増加させ大きな電流駆動能力を得ることができる。

(もっと読む)

141 - 160 / 661

[ Back to top ]