Fターム[5F140AA34]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 熱からの保護 (68)

Fターム[5F140AA34]に分類される特許

1 - 20 / 68

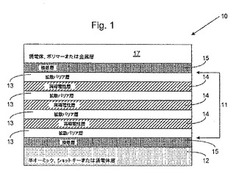

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

半導体装置

【課題】放熱効率が高く低コストでの実装が可能な半導体装置を提供する。

【解決手段】第1の方向に延在するゲート電極を有する複数のトランジスタを有し、複数のトランジスタが第1の方向と交差する第2の方向に配置されたトランジスタアレイ54と、トランジスタアレイの第1の方向に配置され、複数のトランジスタのソース領域に電気的に接続されたパッド電極50とを有する。

(もっと読む)

可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置

【課題】可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置を提供する。

【解決手段】熱によるFETのソース及びドレイン間の電流減少の問題を効果的に解決し、またFETの温度を低めることができる可変ゲートFET及びこのFETを備える電気電子装置を提供し、可変ゲートFETは、FETと、FETの表面または発熱部分に取り付けられ、回路的には、FETのゲート端子に連結されておりゲート端子の電圧を変化させるゲート制御素子と、を備え、FETの温度が所定温度以上に上昇しているときに、ゲート制御素子が、ゲート端子の電圧を変化させて、FETのソース及びドレイン間のチャンネル電流を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

保護トランジスタおよび半導体集積回路

【課題】占有面積が小さく、所望の耐圧と熱破壊の防止を両立した保護トランジスタを提供する。

【解決手段】ゲート長方向の一方の側でゲート直下の領域に隣接しているゲート・ドレイン間領域REgdが、ゲート幅方向に互いに隣接する領域として、第1領域REgd1と第2領域REgd2とを有する。第1領域は、ドレイン耐圧が相対的に大きく、第2領域は、ドレイン電極(ドレインコンタクト部に設けられているシリサイド層10D)からの距離が平面視で第1領域より遠く、ドレイン耐圧が相対的に小さい。このため、耐圧が低いゲート・ドレイン間領域REgd2の加熱部分Aからドレインコンタクト部が遠いが、面積は小さく(または拡大しない)構造となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量且つ高温特性が良好な素子分離領域を有する高速なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1にウエル領域2が設けられ、ウエル領域2内には上部、下部及び側面にシリコン酸化膜3を有し、内部が空孔4に形成されたトレンチ素子分離領域が選択的に設けられ、トレンチ素子分離領域により画定されたウエル領域2が設けられた半導体基板1上にゲート酸化膜9を介してゲート電極10が設けられ、ゲート電極10の側壁にサイドウォール11が設けられ、ウエル領域2が設けられた半導体基板1には、ゲート電極10に自己整合して低濃度のソースドレイン領域(6、7)及びサイドウォール11に自己整合して高濃度のソースドレイン領域(5、8)が設けられ、高濃度のソースドレイン領域にはそれぞれバリアメタル14を有する導電プラグ15を介してバリアメタル17を有する配線18が接続されている構造からなるMIS電界効果トランジスタ。

(もっと読む)

状態密度が設計された電界効果トランジスタ

【課題】nチャネルおよびp型チャネルトランジスタに用いられる層構造を提供する。

【解決手段】nチャネルトランジスタを製作するのに用いる層構造を含む。層構造は、伝導帯底EC1を有する第1の半導体層、離散正孔準位H0を有する第2の半導体層、第1と第2の半導体層との間に配置された広バンドギャップ半導体バリア層、第1の半導体層の上方に配置されたゲート誘電体層、およびゲート誘電体層の上方に配置されたゲート金属層を含み、離散正孔準位H0は、伝導帯底EC1の下方に位置され、ゲート金属層にゼロバイアスが供給される。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】拡散層とゲート電極との少なくとも1つの上に耐熱性が向上したNiSi膜が形成された半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Si基板200と、Si基板200内に形成された拡散層10と、Si基板200上にSiを用いて形成されたゲート電極20との少なくとも1つと、前記拡散層10と前記ゲート電極20との少なくとも1つ上に接触して形成されたP元素を含有したNiSi膜40,42と、を備えたことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バイポーラトランジスタが動作する際に、ベース領域のうちコレクタ側の端部が破壊されることを抑制する。

【解決手段】ベース領域150は、ウェル110内に形成されている。エミッタ領域170はベース領域150の中に形成され、ベース領域150より浅い。コレクタ領域140はウェル110内に形成され、ベース領域150の外側に位置している。第1埋込領域180は、少なくとも一部がベース領域150の中に位置しており、ベース領域150よりも不純物濃度が高い。そして第1埋込領域180は、平面視において、エミッタ領域170とコレクタ領域140の間に少なくとも一部が位置している。また第1埋込領域180は、エミッタ領域170の縁のうち少なくとも一辺と重なっており、かつエミッタ領域170の全面には重なっていない。

(もっと読む)

半導体装置

【課題】 従来、外付け抵抗の電圧降下から検出していたパワーN型MOSFETに流れる電流を、高感度のホール素子に発生するホール電圧VHにより検出する。

【解決手段】 アースラインに向かって配線されたソース配線層8の一部をN型層1に形成したトレンチ20内に配設する。これによりトレンチ20内に配設されたソース配線層8a近傍のN型層1に発生する磁束密度Bを高める。この高い磁束密度Bが発生しているトレンチ20内のソース配線層8a近傍のN型層1を横切るホール電流IH成分を増やし、ホール素子Hに発生するホール電圧VHを高くする。このように、高い磁束密度Bの発生領域にホール素子Hを配置することにより、パワーN型MOSFETのソース電流Iが数A程度でも大きなホール電圧VHを発生する。

(もっと読む)

半導体装置およびその製造方法

【課題】特性の劣化を効果的に抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaNを含む半導体層1と、電極とを備えている。電極は、電極本体6と、半導体層1から見て電極本体6よりも離れた位置に形成され、かつAlを含む接続用電極8と、電極本体6と接続用電極8との間に形成されたW、TiW、WN、TiN、Ta、およびTaNよりなる群から選ばれる少なくとも1種を含むバリア層7とを含んでいる。バリア層7の表面粗さRMSが3.0nm以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

MOSトランジスタ

【課題】MOSトランジスタを作成する。

【解決手段】MOSトランジスタであって、ゲート電極と、ゲート電極下地の頂部表面を有するチャンネル領域と、ゲート電極とチャンネル領域の頂部表面の間に挿入された誘電体スタックとを含み、前記誘電体スタックが、少なくとも高―k材料を含む高―k誘電体層と、少なくともケイ素および窒素を含む誘電体層と、前記高―k誘電体層と前記誘電体層の間に配設された中間層とを含み、該中間層が、少なくとも前記高―k材料、ケイ素および窒素を含み、前記ゲート電極がポリシリコンまたはポリシリコンゲルマニウムから作製される。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、寄生Trのオン電流が半導体層表面を流れることで、素子が熱破壊するという問題があった。

【解決手段】本発明の半導体装置では、ドレイン領域としてのN型の拡散層9にP型の拡散層14及びドレイン導出領域としてのN型の拡散層10が形成される。そして、P型の拡散層14は、MOSトランジスタ1のソース−ドレイン領域間に配置される。この構造により、ドレイン電極28に正のESDサージが印加され、寄生Tr1のオン電流I1が流れた場合にも、寄生Tr1のオン電流I1の電流経路がエピタキシャル層深部側となることで、MOSトランジスタ1の熱破壊が防止される。

(もっと読む)

静電気放電保護装置及び方法

【課題】静電気放電保護装置及び方法を提供する。

【解決手段】本発明の実施例は、静電気放電(ESD)保護装置、及び、ESD保護装置を形成する方法に関する。一実施例は、ESD保護装置で、基板に配置されたpウェルと、基板に配置されたnウェルと、基板中のpウェルとnウェルの間に配置された高電圧nウェル(HVNW)と、pウェルに配置されたソースn+領域と、nウェルに配置された複数のドレインn+領域と、からなる。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置におけるトランジスタの熱破壊を防止し得るとともに、安全動作領域(SOA)を拡大しトランジスタ設計の自由度を高め得る半導体装置及びその製造方法を提供すること。

【解決手段】 トランジスタセルを並列にチップ内に均一に配置した半導体装置において、チップの面中央部にトランジスタセルの不動作領域を形成する。不動作領域を形成手段として、1)ソースとドレインのn型拡散層を設けない方法 2)ソースとドレインのコンタクト窓を開けない方法 3)ゲート電極を分岐してソースに接続する方法を採る。また、不動作領域の形成に代えて当該領域のトランジスタセルの閾値電圧を高くして動作電流を低くする手段を採ることもできる。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

半導体装置

【課題】 複数チャネル出力回路を構成する複数のトランジスタを持つ半導体装置においてセルサイズ縮小および信頼性向上を図る。

【解決手段】 複数のチャネル回路構成において、共通の機能を有する複数のチャネルのトランジスタ群を共通のトレンチ溝で囲い、機能の異なるトランジスタ郡に対して絶縁素子分離されていて、ハイサイド側の隣接するトランジスタのコレクタ部を共有化してVH電源に接続すると共に、ローサイド側の隣接するチャネルのトランジスタ群のエミッタ部を共有化してGND電源に接続する。

(もっと読む)

1 - 20 / 68

[ Back to top ]