Fターム[5F140BE07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成するための処理 (4,399) | 直接変換 (2,415) | 酸化 (1,900)

Fターム[5F140BE07]に分類される特許

141 - 160 / 1,900

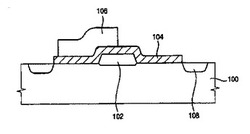

高耐圧トランジスタ及びその製造方法

【課題】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法を提供する。

【解決手段】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法において、半導体基板の所定部位が酸化された第1絶縁膜パターン、及び第1絶縁膜パターンを少なくとも部分的に取り囲む第2絶縁膜パターンを形成する。基板上に導電性物質を蒸着して、第1端部は第1絶縁膜パターン上に位置し、第2端部は第2絶縁膜パターン上に位置するゲート電極を形成した後、基板表面の所定部位に不純物を注入してソース/ドレイン領域を形成する。ゲート電極のエッジ部分に集中される電界を緩和して高い降伏電圧を有するトランジスタを製造することができ、熱酸化膜パターンとCVD酸化膜パターンをゲート酸化膜として使用することで、MOSトランジスタにおいて電流特性及びON抵抗特性を改善することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置の製造方法

【課題】基板に対して斜め方向からイオン注入を行う工程を含む半導体装置の製造方法においてゲート電極サイズの縮小化とリーク電流特性の改善を両立することができる製造方法を提供する。

【解決手段】

半導体基板の表面にゲート電極を形成する。ゲート電極のゲート長方向と交差するゲート幅方向における両端面を被覆するレジストマスクを形成する。半導体基板にゲート長方向成分およびゲート幅方向成分を有する注入方向で不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極とオーバーラップした低濃度不純物層を形成する。ゲート電極の側面を覆うサイドウォールを形成する。ゲート電極およびサイドウォールをマスクとして不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極から離間した高濃度不純物層を形成する。

(もっと読む)

電界効果トランジスタ、その使用、およびその製造方法

【課題】好適な電界効果トランジスタ、その使用、およびその製造方法を提供すること。

【解決手段】窪み(72)に沿ってドープチャネル領域が配置された半導体基板(10)を有する、縦型電界効果トランジスタが説明される。「埋め込まれた」接続領域(18、54)は、半導体基板(10)の表面に達する。第2の接続領域(16)が、同一の表面の窪みの開口部の近傍内に配置される。好ましくは、分離窪み(70、74、76)が、チャネル領域と導電性配線(54)との間、および電界効果トランジスタと隣接する電気部品との間に製造される。電界効果トランジスタは優れた電気特性を有し、容易に製造される。

(もっと読む)

半導体装置およびその製造方法

【課題】縦型トランジスタとしての機能が低下することなく、安定性の高い半導体装置を提供する。

【解決手段】活性領域T及び活性領域Tを区画する素子分離領域3が形成されて成る半導体基板1と、活性領域Tに設けられた凹部9内に形成され、上面が半導体基板1の主面からなる第1ピラー1Aと、活性領域T及び素子分離領域3に渡って形成され、第1ピラー1Aに隣接する第2ピラー2と、第1ピラー1A及び第2ピラー2の各側面を覆うように形成されたゲート電極層10と、第1ピラー1A上に形成されたエピタキシャル半導体層6と、を具備してなり、第2ピラー2が、活性領域T内において第1ピラー1Aから離間して形成された半導体凸部1Bと、素子分離領域3に埋設された埋め込み絶縁膜からなる絶縁体凸部3Aとから構成され、半導体凸部1Bの上面が埋め込み絶縁膜の一部によって被覆されていることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】新規なDTMOSトランジスタの製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1領域と、第1領域に接続しこれより幅狭の第2領域と、第2領域に接続しこれより幅狭の第3領域とを含む半導体領域の画定工程、半導体領域に第1導電型不純物でウェル領域を形成する工程、ウェル領域上へのゲート絶縁膜形成工程、第3領域を幅方向に横断する第1部と、第1部から第1領域上に延びた第2部とを含むゲート電極を形成する工程、ゲート電極側面に、第2領域の一部を覆い他の一部を露出させるサイドウォールを形成する工程、第1領域及び第2領域の他の一部にゲート電極及びサイドウォールをマスクとし第2導電型不純物を注入する工程、熱処理による第2導電型不純物拡散工程、サイドウォールの一部を薬液で除去する工程、第1領域及び第2領域の他の一部へのシリサイド層形成工程を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の耐圧を向上させる。

【解決手段】半導体装置10は、p型半導体基板1、p型半導体基板1内に設けられたn型ドリフト領域3、及びn型ドリフト領域3内に設けられたp型ボディ領域4を含む。p型ボディ領域4の側面とn型ドリフト領域3とのpn接合部22の上方に、そのpn接合部22に沿って、環状のゲート電極6が設けられる。このゲート電極6の一部を挟んでn型ドリフト領域3内及びp型ボディ領域4内にそれぞれ、n型ドレイン領域7及びn型ソース領域8が設けられる。

(もっと読む)

半導体装置、半導体装置の製造方法およびデータ処理システム

【課題】本発明はコンタクト開口をエッチングにより形成した場合にその下に位置する埋込絶縁膜がエッチングされないようにした構造の提供を目的とする。

【解決手段】本発明は、半導体基板と、半導体基板の主面に形成され活性領域を横断して素子分離領域まで延在するトレンチと、トレンチの下部側に形成された埋込型ゲート電極と、活性領域において埋込型ゲート電極の上方のトレンチ内を充填し、かつ、素子分離領域において埋込型ゲート電極の上方のトレンチ内を完全には充填せずにトレンチの内側面に接して配置されるサイドウォールを構成するキャップ絶縁膜と、素子分離領域においてサイドウォールの内側のトレンチを埋めて埋込型ゲート電極に接続形成されたパッドコンタクトプラグと、パッドコンタクトプラグおよびキャップ絶縁膜上を覆う層間膜と、パッドコンタクトプラグに接続するゲートコンタクトプラグとを具備してなる。

(もっと読む)

半導体装置及びその製造方法

【課題】NBTIを改善することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたn型ウェル領域102と、n型ウェル領域102上に形成され、ゲート絶縁膜104と、下部ゲート電極105、及び下部ゲート電極105上に形成された上部ゲート電極106を含むゲート電極120とを有するpチャネル型MISトランジスタとを備える。下部ゲート電極105は、結晶粒界を有する多結晶の金属窒化物で構成されており、当該結晶粒界には金属窒化物を構成する元素とは異なる元素が偏析されている。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

半導体装置の製造方法

【課題】複雑な工程を回避すると共に、高い有効仕事関数値を得ることにより、高歩留まり及び高性能の半導体装置を実現できるようにする。

【解決手段】ダミー電極22をマスクとして、n型活性領域13にp型の不純物イオンを導入することにより、n型活性領域13におけるダミー電極22の両側方にp型のソースドレイン領域25pを形成し、形成されたソースドレイン領域25pに熱処理を施す。熱処理を施した後に、n型活性領域13の上に、ダミー電極22を覆うように層間絶縁膜26を形成し、形成された層間絶縁膜26からダミー電極22を露出し、露出したダミー電極22を除去する。続いて、層間絶縁膜26におけるダミー電極22が除去された凹部26aに、第2の金属電極27を選択的に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電圧の閾値電圧がばらつくことを抑制することができると共に、チャネル抵抗を低減させることができる半導体装置を提供する。

【解決手段】ベース領域4、ソース領域6、ドレイン領域7の不純物濃度を均一とし、第1、第2トレンチ8a、8bをベース領域4よりも浅く形成する。このような半導体装置では、ベース領域4、ソース領域6、ドレイン領域7の不純物濃度が均一とされているため、ゲート電圧の閾値電圧がばらつくことを抑制することができ、また、ソース領域6およびドレイン領域7を深くすることによりチャネル領域を有効に活用でき、チャネル抵抗を低減することができる。さらに、第1、第2トレンチ8a、8bをベース領域4より浅く形成しているため、ベース領域4のうち第1、第2トレンチ8a、8bより深く形成されている部分にはチャネル領域が形成されず、ソース領域6から深さ方向に電流が流れることを抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置及び半導体基板の重水素処理装置

【課題】界面準位密度のゲート酸化膜/半導体界面が形成された半導体装置、および作製方法の提供。

【解決手段】半導体基板とゲート絶縁膜、層間絶縁膜、配線層、保護絶縁膜等の半導体装置に形成される膜又は層の界面近傍での重水素元素濃度が1x1019cm-3以上であることを特徴とする金属−絶縁膜−半導体(MIS)構造を有する半導体装置とする。シリコンカーバイド領域を含む半導体基板上に形成された金属-絶縁膜(あるいは酸化膜)-半導体(MISあるいはMOS)構造を有する半導体装置(電界効果型トランジスタ(MISあるいはMOSFET))に対して、高温に加熱された熱触媒体表面での重水素を含んだガスの熱触媒作用によって生成された活性化した重水素を用いることにより、600°C以下の低温においてゲート絶縁膜/シリコンカーバイド半導体界面近傍に存在するダングリングボンドの重水素終端を図る。

(もっと読む)

半導体装置及びその製造方法

【課題】CMOSトランジスタにおいて、ボロンの染み出しを抑制して閾値電圧を安定させると共に、ノイズを低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】CMOSトランジスタをシリコン基板1上に備える半導体装置であって、

シリコン基板1上に設けられ、窒素とフッ素とを含有するシリコン酸化膜からなるゲート酸化膜5と、ゲート酸化膜5上に設けられ、ポリシリコンからなるゲート電極7、8と、を有し、ゲート酸化膜5中のゲート電極7、8近傍の位置に窒素濃度のピークがあり、ゲート酸化膜5とシリコン基板1との界面付近の窒素濃度は0.5atom%以下であり、ゲート酸化膜5中におけるフッ素濃度は1atom%以上であり、当該フッ素によりゲート酸化膜5とシリコン基板1との界面のダングリングボンドが終端化されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留りを向上させる。

【解決手段】ウエハ(半導体ウエハ)WHの主面1a側に、周縁領域1dからデバイス領域1cを経由して前記周縁領域に至る走査軌道15に沿ってレーザ光LZを照射し、ウエハWHの主面1a側を加熱するレーザアニール処理工程を以下のように行う。ウエハWHの周縁領域1dには、第1出力PW1でレーザ光LZを照射し、ウエハWHのデバイス領域1cには、第1出力PW1よりも高い第2出力PW2でレーザ光LZを照射する。そして、半導体基板1の線膨張係数をα1、絶縁膜の残存膜2の線膨張係数をα2、レーザ光LZが照射された時の半導体基板1の温度をT1、レーザ光LZが照射された時の残存膜2の温度をT2とした時、α1×T1≧α2×T2とする。

(もっと読む)

141 - 160 / 1,900

[ Back to top ]