Fターム[5F140BH14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054)

Fターム[5F140BH14]の下位に属するFターム

LDD(Lightly doped dorain−source) (1,105)

GDD(Graded doped dorain) (11)

DDD(Doble doped dorain) (528)

Fターム[5F140BH14]に分類される特許

201 - 220 / 1,410

半導体装置およびその製造方法

【課題】ソース・ドレイン領域の寄生抵抗の上昇を抑えつつ短チャネル効果の発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2中のゲート電極12の両側に形成され、ゲート電極12側にエクステンション領域161を有し、導電型不純物を含むソース・ドレイン領域16と、ソース・ドレイン領域16のエクステンション領域161のゲート電極12側の側面のみに接し、導電型不純物の半導体基板2中での拡散を抑制する性質を有する拡散抑制不純物を含む拡散抑制層15と、を有する。

(もっと読む)

半導体ウェーハ、及びその製造方法

【課題】シリコン基板にダメージを与えずに、ゲート下の不純物分布の正確な評価を安定して行うことのできる半導体ウェーハとその製造方法を提供する。

【解決手段】 半導体ウェーハは、半導体基板上の所定の箇所に設定されたモニター領域に、他と電気的接続を有しない断面形状がW字型のダミー充填部を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】ゲート電極構造の垂直方向の抵抗を低減する。

【解決手段】半導体基板1と、半導体基板1の上に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成された仕事関数制御層3と、仕事関数制御層3の上に形成された第1のシリサイド層4と、第1のシリサイド層4の上に形成されたポリシリコンゲート電極5と、ポリシリコンゲート電極5の下の半導体基板1中の領域を挟んで半導体基板1中に形成されるソース領域6およびドレイン領域7と、を有する半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とシリコンの界面抵抗を低く保ちつつ、シリサイド層からの金属元素の拡散を抑制し、リーク電流および寄生抵抗を小さくする。

【解決手段】半導体装置100は、基板1(半導体層)と、基板1に接して形成され、基板1とは逆導電型の半導体電極10と、半導体電極10上に半導体電極10に接して形成されたシリサイド層14と、ゲッタリング層12内部において、基板1と半導体電極10との接合およびシリサイド層14からそれぞれ離れて形成され、シリサイド層14に含まれる金属元素をゲッタリングするゲッタリング層12と、を含む。

(もっと読む)

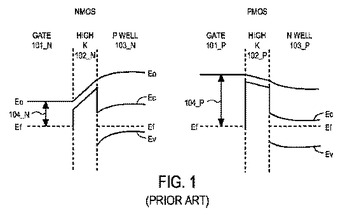

半導体装置およびその製造方法、pチャネルMOSトランジスタ

【課題】nチャネルMOSトランジスタにおいてhigh−Kゲート絶縁膜をhigh−K誘電体膜と酸化ランタン膜の積層により構成した半導体装置において、酸化ランタン膜のパターニングプロセスを不要とする半導体装置の製造方法を提供する。

【解決手段】界面酸化膜22上に形成されたhigh−K誘電体膜23上に酸化膜24を形成する工程と、前記high−K誘電体膜に窒化物層25を形成する工程と、前記窒化物層および前記酸化膜を第1の素子領域21Aから選択的に除去し、第1および第2の素子領域21Bにわたり酸化ランタン膜26を形成し、前記第1の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化ランタン膜を積層した第1の積層構造を、また前記第2の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化膜と前記窒化物層と前記酸化ランタン膜を積層した第2の積層構造を形成する工程と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造コストが低減し、電界効果トランジスタの短チャネル効果が抑制された半導体装置を提供する。

【解決手段】第1導電型のソース領域と、第1導電型のドレイン領域と、が表面に選択的に形成された第2導電型のウェル領域と、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備え、前記ソース領域の最も曲率が高い部分または前記ドレイン領域の最も曲率が高い部分と同じ深さの前記ウェル領域の位置を基準した場合、前記ウェル領域の深さ方向の前記第2導電型の不純物濃度分布のプロファイルは、前記基準からプラスマイナス0.15ミクロンの範囲に不純物濃度分布のピークを有することを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

デュアル仕事関数ゲート構造

トランジスタを有する半導体チップが記載されている。前記トランジスタは、ゲート誘電体にわたって設けられたゲート電極を有する。前記ゲート電極は、前記ゲート誘電体上に設けられた第1ゲート材料、及び前記ゲート誘電体上に設けられた第2ゲート材料を有する。前記第1ゲート材料は前記第2ゲート材料とは異なる。前記第2ゲート材料はまた、前記ゲート電極のソース領域又はドレイン領域にも設けられている。  (もっと読む)

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】応力絶縁膜により、MISトランジスタの駆動能力が劣化することを防止する。

【解決手段】第1のMISトランジスタpTr1は、第1の活性領域10aにおける第1のサイドウォール19Aの外側方下に設けられたトレンチ22内に形成され、第1の活性領域10aにおけるチャネル領域のゲート長方向に第1の応力を生じさせるシリコン混晶層23を含む第1導電型の第1のソースドレイン領域27aと、第1の活性領域10a上に第1のゲート電極14a、第1のサイドウォール19A及び第1のソースドレイン領域27aを覆うように形成され、第1の応力とは反対の第2の応力を生じさせる応力絶縁膜31とを備えている。シリコン混晶層23の最上面は、第1のゲート電極14a直下に位置する半導体基板10の表面よりも高く形成されている。シリコン混晶層23と第1のサイドウォール19Aとの隙間24には、第1の応力緩和膜28aが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動電流が大きくリーク電流の少ない低消費電力のMISトランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】チャネル領域を有する半導体基板と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、半導体基板内にチャネル領域を挟むように配置されたソース拡散層及びドレイン拡散層と、ソース拡散層側の半導体基板内に形成された第1のポケット不純物層と、ドレイン拡散層側の半導体基板内に形成された第2のポケット不純物層とを有し、第1のポケット不純物層は、ソース拡散層のエクステンション不純物層の濃度ピーク位置よりも深い位置に濃度ピークを有しており、第2のポケット不純物層は、ドレイン拡散層のエクステンション不純物層の濃度ピーク位置よりも浅い位置に濃度ピークを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを集積する場合に製造工程数の削減を実現できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、アクティブ領域11を横断しゲート電極10Aよりも長さが短いゲート電極10Bを形成する工程と、ゲート電極10A,10Bをマスクとして、アクティブ領域11に不純物を斜めイオン注入することにより、ゲート電極10Aのゲート長方向両側の領域に互いに連続しない不純物拡散領域20a,20bを形成するとともに、ゲート電極10Bのゲート長方向両側の一方の領域から他方の領域に亘って連続する不純物拡散領域20g,20hを形成する斜めイオン注入工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】塗布法や堆積法を用いて高品質な絶縁部材を半導体素子周辺に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上に、Si系絶縁材料からなる絶縁膜10を付加的に形成する工程と、絶縁膜10上に触媒金属膜11を形成する工程と、触媒金属膜11を触媒として用いて絶縁膜10に酸化処理を施す工程と、酸化処理を施した絶縁膜10を加工してゲート絶縁膜4を形成する工程と、ゲート絶縁膜4を含むMOSFET1を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 これまでのイオン注入処理に比べて、高い時間効率で高濃度のキャリア不純物原子を、通常のイオン注入の処理時間で低エネルギードーピングできる方法を提供する。

【解決手段】 半導体基板としてのシリコン基板11の表面上に加工により突出部を形成した該シリコン基板の内部においてドナーもしくはアクセプターとなる不純物原子を含む不純物薄膜を、堆積膜13としてシリコン基板の表面上に堆積する工程と、前記突出部における前記堆積膜の斜め上方からイオン注入を行なうとともに、該イオン注入によって、前記不純物原子を堆積膜内部からシリコン基板の前記突出部の表面内部にリコイルさせる工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体製造装置

【課題】内部応力を有する膜を基板の裏面にのみ形成することにより、基板の反り量を抑制し、その際に基板の表面にダメージを与えず、裏面に対する成膜と表面に対するパターン形成とを一貫して行う半導体製造装置を得られるようにする。

【解決手段】基板に薬液を塗布する薬液塗布部102と、基板を加熱する加熱処理部104と、基板の表面にレジストを塗布するレジスト塗布部107と、そのレジストに所定のパターンを露光する露光部105と、そのレジストを現像することにより所定のパターンを得る現像部108とを備えている。薬液塗布部102は、基板を浮遊した状態で、基板を回転させながら基板の裏面にのみ薬液を塗布する薬液塗布手段を有し、加熱処理部104は、基板に熱処理を行うことにより、内部応力を有する応力印加膜を成膜する熱処理手段を有し、裏面に応力印加膜の成膜を行うことと、表面に所定のパターンを形成する処理とを一貫して行う。

(もっと読む)

201 - 220 / 1,410

[ Back to top ]