Fターム[5F140CC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 多層 (680)

Fターム[5F140CC01]に分類される特許

101 - 120 / 680

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

半導体装置の製造方法

【課題】希土類金属を含有するHigh-k膜のエッチング残渣を抑制するための半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に絶縁膜4を形成する工程と、絶縁膜4の上に希土類元素含有酸化膜7、12を形成する工程と、フッ酸、塩酸、硫酸を含む薬液により希土類元素含有酸化膜7、12をエッチングする工程とを有し、これにより希土類元素含有酸化膜7、12のエッチングを良好に行う。

(もっと読む)

半導体装置及びその製造方法

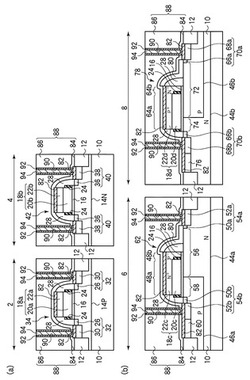

【課題】LDMOSトランジスタに係る半導体装置の高速動作を可能とする。

【解決手段】P型ウエル層3の表面に形成された複数の素子分離膜4の中央部に開口溝5を形成する。開口溝5の側壁から開口溝5の内側に向かってゲート絶縁膜6を介して延在するゲート電極7を形成する。ゲート電極7をマスクにしてセルフアラインでボロンの斜めイオン注入により開口溝5内のP型ウエル層3にP型ボディ層8を形成する。

ゲート電極7をマスクに砒素のイオン注入によりP型ボディ層8にN+型ソース層9を、同時に2つの素子分離膜4間のP型ウエル層3にN+型ドレイン層10を形成する。素子分離膜4の下方のP型ウエル層3にP型ボディ層8の端部からN+型ドレイン層10に延在するN−型ドリフト層を形成する。この際、P型ボディ層8の端部から開口溝5の側壁下部までの領域AのN−型ドレイン層11の幅をできるだけ小さくなるよう制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置の製造方法

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

エッチング方法及び装置

【課題】基板に形成された絶縁膜をエッチングするとき、絶縁膜の下地に酸素プラズマの悪影響が生ずるのを防止できるエッチング方法を提供する

【解決手段】本発明のエッチング方法は、絶縁膜222をプラズマ化させた処理ガスに晒し、絶縁膜222を厚さ方向に途中までエッチングする第一のエッチング工程と、第一のエッチング工程の終了後に残存する絶縁膜222を酸素プラズマに晒し、残存する絶縁膜222の表面に堆積した堆積物を除去する堆積物除去工程と、残存する絶縁膜222をプラズマ化させた処理ガスに晒し、残存する絶縁膜222をエッチングする第二のエッチング工程と、を備える。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、かつ、コンタクト抵抗の増加およびオン電流の減少を防止できる半導体装置の提供。

【解決手段】ピラートランジスタTr1と、前記ピラートランジスタTr1の下部拡散層7aへ信号または電源を供給するとともに、ポリシリコン層10aからの固相拡散し、下部拡散層7aを形成することにより、前記ピラートランジスタTr1のチャネル長d1を厚みにより制御する前記ポリシリコン層10aと、を具備してなることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール形成時の重ね合わせずれに起因したリークの増大やコンタクト抵抗の上昇が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100と、半導体基板100上にゲート絶縁膜101を介して形成されたゲート電極102と、ゲート電極102の側壁上に形成されたサイドウォールスペーサ150と、半導体基板100のうち、ゲート電極102及びサイドウォールスペーサ150を間に挟んで両側に形成されたソースドレイン領域106と、ゲート電極102、サイドウォールスペーサ150、及び半導体基板100の上面を覆う応力絶縁膜110とを備えている。サイドウォールスペーサ150は、少なくとも中央部のゲート長方向膜厚よりも上部のゲート長方向膜厚の方が大きくなっている。

(もっと読む)

101 - 120 / 680

[ Back to top ]