Fターム[5H007CA02]の内容

Fターム[5H007CA02]に分類される特許

41 - 60 / 1,588

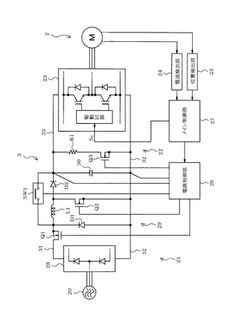

ロボットシステム

【課題】モータの駆動を制御する駆動制御手段の制御内容を変更することなく、高トルク運転時にモータに対して十分な電力を供給することができるとともに、減速動作時にモータから生じる回生エネルギーを有効利用することを可能とする。

【解決手段】昇降圧回路29は、入力電圧を昇圧して出力する昇圧動作、入力電圧を降圧して出力する降圧動作、入力電圧の供給が遮断する電源遮断動作などを実行する。電源制御部26は、バス電圧の検出値に基づいて、モータMが加速動作状態であると判断される期間には昇圧動作を実行し、減速動作状態であると判断される期間には電源遮断動作を実行し、それらの期間を除く期間には降圧動作を実行するように昇降圧回路29の動作を制御する。

(もっと読む)

ゲート駆動回路、電力変換回路、3相インバータ、及びゲート駆動方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】ハイサイドトランジスタ21とローサイドトランジスタ22の少なくとも一方は、ノーマリオン型トランジスタである。2つのゲート駆動回路11、12の少なくとも一方は、正電源から供給される第1電源電圧VDDと、負電圧源30から供給され接地電圧GNDよりも低い第2電源電圧VNEGとに応じた駆動電圧GH、GLを、ノーマリオン型のトランジスタのゲートに出力する。制御回路40は、第2電源電圧VNEGが参照電圧Vrefよりも高い場合、ハイサイドトランジスタ21に流れるドレイン電流を遮断する。

(もっと読む)

電流検出回路、およびモータ制御装置

【課題】プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のオン抵抗Ronと配線パターン抵抗Rpによる電圧降下VDGを基に検出する際に、配線パターンの抵抗Rpにより発生する電圧降下分(オフセット分)をキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出する。

【解決手段】本発明の電流検出回路1は、FET(Qo)のドレイン端子Dと回路グランドGとの間に、第1の抵抗Rdと第2の抵抗Roの抵抗直列回路を接続する。そして、第2の抵抗Ronと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターンRpの抵抗値の比(Ron/Rp)に一致するように設定する。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

(もっと読む)

電子回路

【課題】MOSFETのターンオフ時のスイッチング損失を低減できるとともにサージ電圧を低減できる電子回路を提供する。

【解決手段】バスバー61aにおけるU相用モジュール3の第1電源端子31寄りの部分と、バスバー64aにおけるU相用モジュール3の第2電源端子32寄りの部分との間に、コンデンサ91が接続されている。バスバー62におけるV相用モジュール4の第1電源端子41寄りの部分と、バスバー65におけるV相用モジュール4の第2電源端子42寄りの部分との間に、コンデンサ92が接続されている。バスバー63におけるW相用モジュール5の第1電源端子51寄りの部分と、バスバー66におけるW相用モジュール5の第2電源端子52寄りの部分との間に、コンデンサ93が接続されている。

(もっと読む)

電力制御装置

【課題】インバータ回路の過電流保護、過電圧保護、過電力保護を行う。

【解決手段】電力制御装置10は、直流電源11に接続されて入力電圧Vccが印加され、モータ13に電力を供給するインバータ回路12と、このインバータ回路12に流れる入力電流Iinを、この入力電流Iinに相当する電圧Vin2に変換して検出する入力電流検出回路21と、インバータ回路12を制御する電流電圧制御部20を備えている。電流電圧制御部20は、入力電圧Vccが印加されたときのインバータ回路12に流れる電流の制限値に相当する基準電圧Vrefを生成し、基準電圧Vrefと電圧Vin2とを比較することにより、入力電圧Vccに応じた所望の入力電流制限値Imax以内で動作するようにインバータ回路12を制御する。

(もっと読む)

スイッチング回路、電子回路及びスイッチング方法

【課題】スイッチング電源における電力損失を最小にするデッドタイムの設定に関して、信頼性をより高める。

【解決手段】DC−DCコンバータのスイッチング部18は、スイッチング駆動部5、温度検出部19、デッドタイム設定部21を有する。温度検出部19は、スイッチング駆動部5の温度Θを示す温度検出信号20をデッドタイム設定部21へ出力する。デッドタイム設定部21は、温度検出部19により出力された温度Θが示す温度検出信号に基づき、スイッチング駆動部5の温度Θがより低いデッドタイムdtを探索する。

(もっと読む)

電子制御装置およびモータ制御装置

【課題】アナログ変換処理の実行周期はアナログ変換処理を行う制御装置内で定められる所定周期ではなく、インバータ等の制御対象に入力される信号と共通のタイミングでアナログ変換処理を行わなければ、電流制御の精度やモータ制御の効率低下を招いてしまう。

【解決手段】電子制御装置内において一定周期で発生する動作開始トリガにより、予め登録されているアナログ信号のアナログ変換処理をシーケンシャルに実行する、第一のアナログ変換機能と、前記電子制御装置外部と共通のタイミングで発生する動作開始トリガにより、予め登録されているアナログ信号のアナログ変換処理をシーケンシャルに実行する、第二のアナログ変換機能と、を備え、前記第一のアナログ変換機能よりも前記第二のアナログ変換機能の処理機能の優先度を高くする。

(もっと読む)

回生型モータ端サージ電圧抑制装置、モータ駆動システム、および、回生型モータ端サージ電圧抑制方法

【課題】サージ電圧に基づくエネルギーを回生することでサージ電圧を抑制しながら電力使用効率を向上し、電流の誤検出を抑制できるようにした回生型モータ端サージ電圧抑制装置、モータ駆動システム、および、サージ電圧回生方法を提供する。

【解決手段】回生型モータ端サージ電圧抑制装置は、インバータ装置が直流入力ノードに入力した直流電圧を交流変換してケーブルを通じて高周波を含む電圧を出力するモータの入力端子に入力側を接続した整流器と、整流器の整流出力にコンデンサを介して入力側を接続すると共に出力側をインバータ装置の直流入力ノードに接続した入出力絶縁型のDCDCコンバータと、を備える。

(もっと読む)

スイッチング電源装置及びサージ吸収回路

【課題】少ない部品点数で構成することができ、電源効率を有効に改善することができるスイッチング電源装置を提供する。

【解決手段】本発明によるスイッチング電源装置(10)は、直流入力を交流に変換するスイッチング回路をなすトランジスタ(Q1)と、前記交流が入力された非絶縁型トランス(T)と、非絶縁型トランスから出力された交流を整流するダイオード(D2)と、ダイオード(D2)の出力部から非絶縁型トランス(T)の入力部に向かう電流方向を順方向として、ダイオード(D2)の出力部と非絶縁型トランス(T)の入力部との間に接続されたダイオード(D3)とを備える。スイッチング動作の過程でダイオード(D2)のカソード側に発生したサージが、ダイオード(D3)を介して非絶縁型トランス(T)の1次側に吸収される。

(もっと読む)

マルチレベルインバータ回路

【課題】4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供する。

【解決手段】本発明に係るマルチレベルインバータ回路は、共振形スイッチトキャパシターコンバータを用い手いることを特徴のひとつとする。また、マルチレベルインバータ回路は、マルチレベルインバータ部と、マルチレベルインバータ部とDCリンクコンデンサ部を介して接続されるRSCC部と、を有することを特徴とする。

(もっと読む)

電力変換装置

【課題】昇圧回路と単相インバータを備えて直流を交流に変換するパワーコンディショナなどの電力変換装置において、パワーデバイスのスイッチング損失を低減する。

【解決手段】直流電源1の電圧を昇圧回路2で昇圧してコンデンサに充電した後、単相インバータ4で交流電力に変換して出力する際、昇圧回路2と単相インバータ4の各パワーデバイスをPWM制御するが、このとき各パワーデバイスのスイッチング周波数を決める2種類の三角波キャリア周波数をその発生手段17、18で発生し、制御手段8は交流出力電流の絶対値が閾値を超えた場合には、三角波キャリア周波数の低い方を使用してPWM制御を行い、交流出力電流の零付近を除く範囲でスイッチング回数を低下させて損失の低減を図り、かつ交流出力電流の零付近で電流リプルの最大振幅が増加するのを防ぐ。

(もっと読む)

電力変換装置

【課題】出力電流から直流成分を効果的に取り除くことができる電力変換装置を提供すること。

【解決手段】電力変換装置は、電力変換部と、電圧検出部と、電流検出部と、検出電圧調整部と、制御部とを備える。電力変換部は、電源装置の電力を交流電力へ変換して電力系統へ出力する。電圧検出部は、電力系統の電圧を検出する。電流検出部は、電力変換部と電力系統との間に流れる電流の直流成分を検出する。検出電圧調整部は、電流検出部によって検出された直流成分に応じたバイアスを加えて生成した信号を電圧検出信号として出力する。制御部は、電圧検出信号に応じた交流電圧を電力変換部から出力させる。

(もっと読む)

電力変換装置および電源システム

【課題】トランスの偏磁を未然に抑止できる電力変換装置や電源システムを提供する。

【解決手段】スイッチング素子Q1〜Q4とトランスTr1とを少なくとも含む電力変換装置20において、トランスTr1の二次端子から出力される交流電力を整流する二以上のダイオードD21,D22(整流部)と、整流された直流電力を個別に積分して得られる波形を出力する積分波形出力部22,23と、積分波形出力部22,23から出力される二以上の波形のうちで一の波形にかかるピーク値Wpを保持するピークホールド部24と、上記二以上の波形のうちで他の波形にかかる波形値W2とピークホールド部24によって保持されるピーク値Wpとの差分値Δdを検出する差分値検出部25と、検出された差分値Δdに基づいてスイッチング素子Q1〜Q4を操作する操作信号を制御する操作信号制御部21とを有する。

(もっと読む)

インバータ装置

【課題】筐体の一部の板厚を薄くしたとしても、所望の規格の要求を満たす。

【解決手段】本実施形態のインバータ装置は、筐体の一部に所定の規格により定められた板厚よりも薄い板厚である薄肉部を有するインバータ装置であって、その薄肉部を金属製の板部材によって覆ったことを特徴とする。

(もっと読む)

モータ駆動装置

【課題】モータを適正に動作させることができ、かつ、電流検出用抵抗による電力損失を小さくできるモータ駆動装置を提供する。

【解決手段】モータ駆動装置1は、直流電源Vccに接続されている制御回路部10と、電流検出経路50を構成する電流検出用抵抗R1及びインダクタL0と、比較器20とを備え、制御回路部10からモータ2に駆動電力を供給する。電流検出用抵抗R1は制御回路部10に接続されており、インダクタL0は電流検出用抵抗R1と直流電源Vccの負電極との間に接続されている。電流検出経路50は、モータ2の駆動電力に応じた検出電圧を検出する。検出電圧と基準電圧との比較結果が比較器20から制御回路部10に出力され、それに応じてモータ2が制御される。電流検出経路50として電流検出用抵抗R1のみが設けられている場合と比較して、インダクタL0の直流分の抵抗値だけ電流検出用抵抗R1の抵抗値を小さくできる。

(もっと読む)

インバータ制御装置

【課題】コアレス電流センサを用いた際の検出精度の悪化の影響を無くしてモータを正常に駆動させることが可能なインバータ制御装置を提供する。

【解決手段】コアレス電流センサ40が備えるシールド板により生じる残留磁束の影響により出力電圧Vuv、Vvwに含まれる位相遅れ及びゲイン誤差が無くなるように、出力電圧Vuv、Vvwを補正し、その補正された補正出力電圧Vuv、Vvwと、外部から入力される指令値とに基づいて、モータインバータ41を制御する。

(もっと読む)

ハーフブリッジ回路

【課題】低出力におけるターンオフ時のスイッチング速度を速められるようにしたハーフブリッジ回路を提供する。

【解決手段】モード1〜3において誘導性負荷Lの通電方向が第1方向(図示左方向)であるとき、MOSトランジスタS1にオフ制御信号を印加するときには、MOSトランジスタS2にオン制御信号を印加するまでの間に、第1方向と同一方向に通電するようにMOSトランジスタS3、S4に制御信号(S3=オン制御信号:S4=オフ制御信号)を一方向通電制御信号として印加する。モード4〜6において誘導性負荷Lの通電方向が第2方向(図示右方向)であるとき、MOSトランジスタS2にオフ制御信号を印加するときには、MOSトランジスタS1にオン制御信号を印加するまでの間に、第2方向と同一方向に通電するようにMOSトランジスタS3、S4に制御信号(S3=オフ制御信号:S4=オン制御信号)を一方向通電制御信号として印加する。

(もっと読む)

インバータ電源装置

【課題】出力電流のオーバーシュートを効果的に抑制する。

【解決手段】本発明に係るインバータ電源装置は、デジタル制御部、アナログ制御部、デジタル制御部によって制御されるIGBT、アナログ制御部によって制御されるFET等を含む。デジタル制御部は、下記式(1)に基づいて演算を行う演算部と、IGBTおよびFETに対する駆動信号を出力する出力部とを含む。出力部は、出力電流値が電流閾値Isに達した場合、IGBTをオフにし、かつ、その後、出力電流値Iが電流閾値Isを超えた範囲において、IGBTがオフに維持されつつFETのみが駆動するように、第1および第2駆動信号を出力する。

Is=i−To*(ΔI/Δt) ・・・式(1)

(Isは電流閾値、iは電流設定値、ToはIGBTがオンになった時点から出力電流値Iが上昇し始めるまでの時間(遅延時間)、ΔI/Δtは電流変化率)

(もっと読む)

駆動回路および電流制御回路

【課題】ペルチェ素子を加熱および冷却を切替えて使用する。

【解決手段】一端が負荷と接続され、他端が負荷を駆動する駆動用電源と接続され、少なくとも、入力端子に入力される第1の制御信号に応じてオン状態およびオフ状態を切り替える第1のスイッチング素子と、一端が負荷および第1のスイッチング素子の一端と接続され、他端が基準電位と接続され、第2の制御信号に応じてオン状態およびオフ状態を切り替える第2のスイッチング素子と、第2のスイッチング素子がオフ状態である場合に、第1のスイッチング素子の入力端子に電圧を供給する電圧供給部と、第1の制御信号および第2の制御信号のそれぞれを、第1のスイッチング素子および第2のスイッチング素子のそれぞれに供給し、第1のスイッチング素子と第2のスイッチング素子とを交互にオン・オフ動作させる制御部とを備える。

(もっと読む)

電力変換装置

【課題】出力波形歪を低減する電力変換装置。

【解決手段】共通端子間の第1電圧を所望値にする指令値Vrcを交流入力電圧に同期し発生する指令値発生手段44、共通端子間の第2電圧を所望値にする指令値Vriを交流入力電圧に同期し発生する指令値発生手段45、最大及び最小バイアス電圧値が交互に配置された方形波バイアス電圧Vsを発生するバイアス電圧発生器46、Vrc-Vri+Vsを最大及び最小リミッタ値間に制限した第1値とVri-Vrc+Vsを示す第2値Vr3とVr3-Vri又はVs-Vrc又はVs-Vriを最大及び最小リミッタ値間に制限した第3値を出力する演算手段47〜49、交流入力電圧に同期し出力波形歪を低減する補償電圧を発生する補償波形発生器30、第1乃至第3値の夫々の値から補償電圧を減算し第4乃至第6値を得る演算手段31〜33を有し、第4乃至第6値に基づき第1乃至第6スイッチをオンオフさせる。

(もっと読む)

41 - 60 / 1,588

[ Back to top ]