Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

661 - 680 / 722

インターフェース回路及び電力変換装置並びに車載用電機システム

【課題】 信号伝送が行われる回路間の基準電位の電位差が変動しても確実に信号を伝達できるインターフェース回路を提供することを課題とする。

【解決手段】 上記課題を解決するために、インターフェース回路4を、レベルシフト回路20と、このレベルシフト回路20の動作用電源電圧の電位を選択するための電位選択回路10から構成した。電位選択回路10は複数の入力電位のうちの一つを選択し、レベルシフト回路20は第1の電位を基準電位とする電圧パルスを入力し、第2の電位を基準電位とする電圧パルスを出力し、前記電位選択回路の出力電位と第1の電位との電位差及び前記選択電位と第2の電位との電位差で動作する。

(もっと読む)

スイッチング装置

【課題】高圧側と低圧側の間に一対以上のノーマリ・オンの半導体スイッチング素子が直列に接続されている場合、ゲート駆動回路の異常動作時に各半導体スイッチング素子に流れる過電流を抑制する。

【解決手段】ノーマリ・オン(ディプレッション型)のハイアーム側半導体スイッチング素子15a〜15cと、同じくノーマリ・オンのローアーム側半導体スイッチング素子17a〜17cとを直列に接続している場合に、各半導体スイッチング素子15a〜15c,17a〜17cの各ゲートを、抵抗19a〜19c,21a〜21cを介してそれぞれ電源Bのマイナス(−)側に接続する。

(もっと読む)

異常検出装置

【課題】簡素な構成で確実に異常を検出することができ、装置の小型化、低コスト化を図った異常検出装置を提供する。

【解決手段】電圧電流変換回路11がMOSFETQ2のドレイン−ソース間電圧に応じた、つまり、負荷電流ILに応じた電流ISを出力する。コンデンサC1が、電圧電流変換回路11からの電流ISによって充電される。カレントミラー回路12が、コンデンサC1に蓄積された電荷を放電する。コンパレータCP1が、コンデンサC1の両端電圧が基準電圧Vref1を超えたとき、異常を検出する。また、互いに寄生ダイオードの向きが対向するように直列接続されたMOSFETQ1及びQ2がバッテリ−負荷10間に設けられて、バッテリの逆接保護が図られている。

(もっと読む)

半導体装置

【課題】 オン抵抗を小さくさせつつ、耐圧を向上させることが可能な半導体装置を提供することを目的とする。

【解決手段】 ドレイン領域41と、チャネル領域42と、ソース領域43と、トレンチ44内に第1の絶縁膜2を介して設けられる第1のゲート電極3と、トレンチ44内に第1の絶縁膜2を介して設けられると共に第1のゲート電極3の下方に第2の絶縁膜4を介して設けられる第2のゲート電極5とを備えて構成し、第1のゲート電極3に、ドレイン領域41とソース領域43との間に流れる電流を制御する第1のゲート信号を入力し、第2のゲート電極5に、少なくとも第1のゲート信号がローレベルのとき正の電圧である第2のゲート信号を入力する。

(もっと読む)

通信リンクを通じて電力を与えるためのシステムにおける電源装置の出力電圧に基づく電流制限しきい値の調整

通信リンクを通して電力を与えるための電源装置は、電流制限しきい値に基づいてシステムの出力電流を限定するための電流制限回路と、システムの出力パラメータに従って電流制限しきい値を設定するためのしきい値回路とを有する。しきい値回路は、特にシステムの実質的に一定の出力電力を達成するために、システムの出力電圧に従って電流制限しきい値を制御することができる。  (もっと読む)

(もっと読む)

直流電源装置

【課題】待機時電力を削減し、アクロスザラインコンデンサの放電の時定数を所定の値にする直流電源装置を提供する。

【解決手段】交流電源の双極に接続されローパスフィルタを構成するアクロスザラインコンデンサを備えた直流電源装置であって、

第1のトランジスタQ3は、交流電源が接続される状態においては、オンし、第1のトランジスタQ3に従属接続される第2のトランジスタQ4はオフし、第2のトランジスタQ4のドレイン側抵抗とソース側抵抗に電流を流さず、交流電源が非接続状態となると第1のトランジスタQ3は、ほぼ瞬時にオフするとともに第2のトランジスタQ4はオンし第2のトランジスタQ4のドレイン側抵抗とソース側抵抗を通じて所定の時間内で、アクロスザラインコンデンサC5の充電電圧を放電する。

(もっと読む)

電源装置

【課題】 容量性負荷の起動時における過電流保護機能の不本意な作動を防止して電源装置自体を、更には負荷を正常に起動することのできる電源装置を提供する。

【解決手段】 例えば電池から負荷への電源供給ライン(大電流パス)に介挿されたスイッチ素子(例えばFET)2と、大電流パスに並列な小電流パスを形成する補助スイッチ素子(例えばFET)12および小電流パスに電流が流れたときにスイッチ素子をオフ動作させる制御素子11を備えた過電流検出回路と、前記負荷の起動時に補助スイッチ素子をオン動作させて小電流パスを形成する制御手段とを備える。そして負荷の起動時には小電流パスを介して負荷に電力供給し、この電力供給が正常に行われた後に大電流パスを介して負荷に電力供給する。

(もっと読む)

スイッチング回路

【課題】貫通電流防止のために、スイッチング制御信号の立ち上がりを遅らせていることによるスイッチング回路の効率を向上させる。

【解決手段】電源の間に直列に接続された第1及び第2のトランジスタTR1a,TR1bを有するスイッチング回路であって、トランジスタの制御端子及びソースまたはドレイン間に接続される第1、第2の制御回路1a,1bと、制御回路内に形成され第1、第2、第3,第4の電圧クランプ素子とを有している。これによりスイッチング素子であるトランジスタの閾値電圧をスイッチング制御信号の中心レベル付近にし、2つのトランジスタが共にオフ状態となるタイミングを作る。この結果、スイッチ動作のときに発生していた貫通電流を防止し、スイッチング速度の高速化とスイッチング回路の高効率化が可能となる。

(もっと読む)

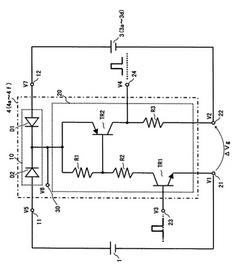

ハイサイド駆動回路

【課題】比較的簡易な構成で、ハイサイドスイッチを高速かつ効率的に駆動するためのハイサイド駆動回路を提供する。

【解決手段】トランジスタQ7,Q8、ダイオードD1,D2、キャパシタC1,C2、変圧器T1によりトリガ信号生成部を構成し、PWM信号をトリガ信号に変換する。ダイオードD3とキャパシタC3によりブートストラップ部を構成し、ハイサイド用電源としてNチャネルトランジスタQ5を高速にオン・オフさせる。抵抗R1,R2、ダイオードD4〜D8、トランジスタQ1,Q2、NチャネルトランジスタQ3,Q4は、ハイサイド用の駆動信号生成部を構成し、トリガ信号V3を、NチャネルトランジスタQ5をドライブするための駆動信号に変換する。

(もっと読む)

電源装置および電気回路

【課題】 負荷に対する電池からの電力供給を制御するFETの短絡障害を、その定常運転時に速やかに検出し得る診断機能を備えた電源装置を提供する。

【解決手段】 負荷に対する電力源としての電池(10)の電源出力ラインに直列に介挿された電源出力制御用のFET(11)に対して、そのゲート・ソース間に故障診断用のFET(14)を並列接続し、故障判定回路(17)においては故障診断用FETの出力電圧をモニタして電源出力制御用FETの健全性を定する。

(もっと読む)

電力供給制御装置

【課題】 パルス列状の制御信号に基づく半導体素子のオンオフ動作により電力供給の制御を行うことができ、かつ半導体スイッチ素子の破壊を効果的に防ぐことが可能な電力供給制御装置を提供する。

【解決手段】 電力供給制御装置10には、PWM制御信号に基づくゲート端子Gのレベル変化によりオンオフ動作するFET20を備えたサーマルFET11が設けられており、このサーマルFET11には、更に、温度センサ21による検出結果に基づいて強制的にゲート端子Gの電圧レベルを変化させてFET20の遮断動作を行う過熱保護回路42が設けられている。そして、入力レベル検出手段50によってゲート端子Gの電圧レベルに対応した信号がマイコン12に入力されるようになっており、このマイコン12は、検出されたゲート端子Gの電圧レベルが、FET20の遮断レベルに所定回数達した場合に制御信号を停止するように構成されている。

(もっと読む)

パワー半導体装置

【課題】 インダクタンスが小さくでき、サージ電圧が小さくかつ小型化が可能なパワー半導体装置を提供する。

【解決手段】 パワー半導体装置が、冷却面を備えた水冷ブロックと、冷却面上に配置され、パワー半導体素子を含む封止樹脂と、封止樹脂の第1側面から突出した主端子と、第1側面に対して略平行な第2側面から突出した制御端子とを備えたパワーモジュールと、パワーモジュールを挟んで配置された1対の主回路基板と制御端子であって、主端子に接続された主回路基板と制御端子に接続された制御基板とを含む。主端子は、冷却面に略平行な第1領域と、主回路基板と略同一平面となるように該第1領域から角度θだけ屈曲した第2領域からなり、主回路基板と第2領域とが、これらを貫通するボルトとナットにより固定される。

(もっと読む)

駆動回路

【課題】本発明は、ターンオン時及びターンオフ時の過渡時、消費電力のロスを低減でき、且つ出力電流の高周波成分によるEMIノイズの発生を低減することができる駆動回路を提供する。

【解決手段】一方の端子に負荷が接続されたドライバ素子2のオン/オフを制御する駆動回路であって、ドライバ素子2の制御端子に電流を流し込むスイッチ素子4と、ドライバ素子2の制御端子から電流を引き出すスイッチ素子3とを有するスイッチング回路1と、ドライバ素子2の制御端子と他方の端子との間に設けられた容量素子8とを備える。

(もっと読む)

電源回路

【課題】大容量のコンデンサを設けることなく、しかも電力源から供給される電力の使用効率を低下させることなく、安定した出力電圧を得ることが可能となる電源回路を提供する。

【解決手段】商用交流電源により動作する電子装置の電源回路において、ブリッジ整流後の脈流を入力コンデンサ104で平滑したリップルを含む直流電圧をスイッチング電源回路114により所定の電圧に降圧する構成である。電子装置内に設けられ、ゼーベック効果によって熱を電気エネルギーに変換する熱電変換素子9の熱起電力を、電圧安定化回路11及び電圧変換回路12を介し電圧加算回路13からスイッチング電源回路114の一次側へ補充電力として付加する。補充電力の電圧を、誤差検出・制御回路14によりスイッチング電源回路114の二次側の出力電圧の変動量に応じて増減し、負帰還制御によって出力電圧を安定させる。

(もっと読む)

電力供給制御装置及び半導体装置

【課題】電力供給制御装置において、異常を精度高く検出しうる構成を提供する。

【解決手段】 電力供給制御装置10は、パワーMOSFET15と、パワーMOSFET15の電流量に応じたセンス電流が流れるセンスMOSFET16と、センス電流と閾値電流とに基づいて、パワーMOSFET15に流れる電流の異常検出を行う異常検出回路13とがワンチップ化されて半導体スイッチ素子11が構成されている。半導体スイッチ素子11の外部には、パワーMOSFET15のソース端子に接続され、他端が、半導体スイッチ素子11の外部端子P4と接続され、一端の接続点の電圧レベルVsに応じた電流を、外部端子P4を通して流す外付け抵抗12が設けられている。異常検出回路13は、外部端子P4に接続されると共に、外部端子P4を通して流れる電流に応じた閾値電流Ia、Ibと、センス電流とを比較することに基づき異常信号SC,OCを出力する。

(もっと読む)

電流検出回路

【課題】 センス抵抗の両端電圧が負の値に振れた場合でも増幅回路への入力電圧をその負の値に対応する正の値に変換する分圧抵抗に求められる分圧比の精度を下げることができ、集積化の実現を可能とした電流検出回路を提供する。

【解決手段】 センス抵抗11のノードN1に抵抗R3を介して演算増幅器20の反転入力端子が接続され、ノードN2には抵抗12を介して演算増幅器20の非反転入力端子が接続される。非反転入力端子には、抵抗13と、直流電源B1とが接続される。抵抗12と13の抵抗値を調整することにより、増幅器20の非反転入力端子の電圧が常に正に維持される。

(もっと読む)

電力用半導体装置

【課題】逆回復電流に起因するスイッチング損失を減少することができ、発熱損失を減少することができ、小型化を実現することができる電力用半導体装置を提供する。

【解決手段】電力用半導体装置1において、カスコード素子20の電力用半導体スイッチング素子21のソース領域と負極端子11との間に複数直列接続された第1の金属絶縁膜半導体型電界効果トランジスタ22及び第2の金属絶縁膜半導体型電界効果トランジスタ23を備え、カスコード素子20に対して電気的に並列に高速ダイオード30を備える。電力用半導体スイッチング素子21はノーマリーオン型であり、第1の金属絶縁膜半導体型電界効果トランジスタ22及び第2の金属絶縁膜半導体型電界効果トランジスタ23はノーマリーオフ型である。

(もっと読む)

電力供給制御装置

【課題】異常を迅速に検出し、パワーMOSFETでの電力損失を効果的に低減しうる構成を提供する。

【解決手段】電力供給制御装置10はパワーMOSFET15と、センスMOSFET16と、異常検出回路13とがワンチップ化されて半導体スイッチ素子11が構成される。半導体スイッチ素子11の外部にはパワーMOSFET15のソース端子に接続され、他端が外部端子P4と接続され、ソース端子の電圧レベルVsに応じた電流を外部端子P4を通して流す外付け抵抗12を設ける。異常検出回路13は外部端子P4に接続されると共に、外部端子P4を通して流れる電流に応じた閾値電流Ia、Ibと、センス電流とを比較することに基づき異常信号SC,OCを出力する。閾値電流Ia、Ibは、短絡が生じた場合に、センス電流が即座に閾値に達することなるため、迅速な検出が可能となり、かつパワーMOSFETでの電力損失を低減できる。

(もっと読む)

信号伝達回路

【課題】 コストダウンの障害となるLDMOS(Laterally Diffused Metal Oxide Semiconductor)の使用数を削減しコストダウンを図れる信号伝達回路を提供する。

【解決手段】 低電位の回路において、パルス発生器11aは信号入力端HINから入力した信号の正負のエッジを検出し、それぞれのエッジを表すパルス信号をスイッチング素子Q1〜2に出力する。スイッチング素子Q1〜2は電流源Ires1〜2をオン/オフし、LDMOSQ3を介して高電位の回路において、抵抗R3に電流を供給する。抵抗R3は電流地に応じた電圧を両端に発生し、異なる閾値を有するインバータInv1〜2によって、低電位の回路にて入力された信号の正負のエッジが復元され、パルス検出回路12a、RS(Reset-Set)フリップフロップ13、スイッチング素子Q5〜6、抵抗R13〜14によって、入力された信号が復元される。

(もっと読む)

パワートランジスタの保護

【課題】 少なくとも部分的に誘導性の負荷の電源を制御するトランジスタを保護するための方法を提供する。

【解決手段】 第1の導電端子及び制御端子の間に、一方向導電素子と直列逆接続で挿入される少なくとも1つのブレイクオーバコンポーネントを有するトランジスタを保護するための回路であって、前記ブレイクオーバコンポーネントと直列の抵抗素子と、前記一方向導電素子の前記トランジスタと対向する端子及び該トランジスタの第2の導電端子の間の、制御可能な電流源とを有する。そして前記電流源は、前記トランジスタにおける電流によって制御されるようにしている。

(もっと読む)

661 - 680 / 722

[ Back to top ]