Fターム[5H740BA12]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | トランジスタ (1,563) | 電界効果トランジスタ(FET) (722)

Fターム[5H740BA12]に分類される特許

701 - 720 / 722

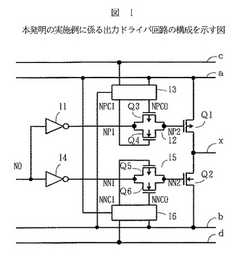

出力ドライバ回路及び半導体IC

【課題】出力ドライバ回路における出力レベルの変動に伴って生じる電源線の電位の変動を抑える。

【解決手段】実装配線により外部電源に接続された電源線aと、外部へ信号を出力する出力線xと、該電源線aと該出力線xにそれぞれドレインとソースが接続され、ゲートにはスイッチ12を介して信号が入力される出力トランジスタQ1と、該電源線aの電位の変動を検出する検出器13を備え、該検出器13の出力により該スイッチ12の開閉を制御する。

(もっと読む)

パワースイッチとこれを用いたスイッチング電源

【課題】電力損失が大きかった。

【解決手段】 高周波信号が誘導されるコイル24と、このコイル24の一方に接続された抵抗25と、この抵抗25に接続されたトランジスタ26と、このトランジスタ26のゲート端子とソース端子との間に接続されたダイオード27と、このダイオード27に接続されたトランジスタ28と、このトランジスタ28のドレイン端子に接続された入力端子29と、コイル24の他方とトランジスタ26のドレイン端子とトランジスタ28のソース端子とに接続された出力端子30とを備え、トランジスタ28のゲートとソース間の浮遊容量32は、トランジスタ26のゲートとソース間の浮遊容量33より大きなトランジスタを用いたものである。

(もっと読む)

PWMモータ駆動回路

【課題】高速で小型、低損失で信頼性の高いPWMモータ駆動回路を実現する。

【解決手段】ソースを電源+VDDと接続したPチャンネルMOSFETトランジスタTru+ とソースをGNDと接続したNチャンネルMOSFETトランジスタTru- のドレインを接続し、モータコイルの出力とする。また、前記PチャンネルMOSトランジスタTru+ のソースとゲート間にバイアス抵抗R4を接続し、その抵抗R4と並列にソースとゲートを前記PチャンネルMOSトランジスタTru+ のオフ時に短絡するトランジスタQ2を設けるとともに、前記ゲートとコレクタを接続し、ベースを電源+VDDに接続した入力用のNPNトランジスタQ1のエミッタをマイコン2のポートP1に接続する。一方、前記NチャンネルMOSトランジスタTru- のゲートをマイコン2のポートP2と接続して両ポートP1、P2から駆動信号を入力する。この回路を用いることで簡便で高速動作ができて小型化が図れ、低損失で信頼性の高いPWMモータ駆動回路を実現する。

(もっと読む)

スナバ装置

【課題】 比較的安価な回路構成で、第1および第2端子間に過電圧がかからないようにすることが可能なスナバ装置を提供する。

【解決手段】 スナバ装置は、IGBT1のコレクタ−エミッタ間に並列接続されるIGBT2と、IGBT2のコレクタ−エミッタ間電圧に相関する電圧を検知する電圧検知回路3と、電圧検知回路3の検知結果に基づいてIGBT2のゲート電圧を制御して、IGBT1のコレクタ−エミッタ間電圧を制御する電圧制御回路4とを備えている。IGBT1のターンオフ時に、IGBT1のコレクタ−エミッタ間電圧が所定電圧を超えたか否かを電圧検知回路3で検知し、所定電圧を超えた場合には、IGBT1に並列接続されたIGBT2に主電流の一部を迂回させるようにしたため、ターンオフ時にIGBT1のコレクタ−エミッタ間電圧が所定電圧以上にならなくなる。

(もっと読む)

ゲートドライブ回路、ハイサイド側ドライブモジュールおよびドライブ装置

【課題】外乱ノイズや寄生容量の影響を受けにくく、貫通電流によるスイッチングデバイスの破壊を抑制するゲートドライブ回路を得る。

【解決手段】パルス信号からデッドタイム期間が削除されたデッドタイム信号を入力し、エッジトリガ回路13は、パルス信号からデッドタイム期間を削除したデッドタイム信号を入力しデッドタイム信号の立上りエッジ信号と立下りエッジ信号とを生成し、レベルシフト回路15は、デッドタイム信号とその反転信号と立上りエッジ信号と立下りエッジ信号とを入力し、これらの4つの信号に基づいてスイッチングデバイス71の駆動信号を生成する。

(もっと読む)

電力半導体モジュールのゲートドライブ回路

【課題】 単に1つの電力半導体素子のゲート破壊をも検出できる異常検出回路を備えた電力半導体モジュールのゲートドライブ回路を提案する。

【解決手段】 スイッチングレギュレータからの駆動パルスを平均化した検出電圧を発生するデユーティ比検出回路を用い、検出電圧が基準電圧よりも低下し、しかも電力半導体モジュールの応用回路が動作を停止し、ゲートブロック信号が発生したときに異常検出信号を発生する異常検出回路を設ける。また、負側整流ダイオードと負側直流出力点との間に抵抗素子を接続し、正側直流出力点と負側直流出力点との間の直流電圧に応じた検出電圧を発生し、この検出電圧に基づき異常検出信号を発生する異常検出回路を設ける。また、負側平滑コンデンサと並列に接続された発光ダイオードを有するホトカプラにより、異常検出信号を発生する異常検出回路を設ける。

(もっと読む)

交差伝導防止ドライバ制御回路および方法

交差伝導防止ドライバ回路および方法は、競合状態の発生を防止し、本発明に従って制御される、典型的にはMOSFETの、直列接続電力デバイス間の交差伝導を回避する。個々の状態機械が、各電力デバイスドライバの入力と出力の間に接続され、ドライバが要求されたタスクを完了した時点を正確に決定するように構成される。各状態機械は、ドライバステータスに基づいて「ロックアウト」信号を生成し、この信号は、指定条件下において反対側ドライバの動作を禁止し、それによって、直列接続電力デバイス間の交差伝導を防止するために使用される。  (もっと読む)

(もっと読む)

電源制御回路

電源順序付けシステムおよび方法が開示される。一実施例において、プログラマブルチャージポンプは、プログラマブル電流源を供給し、この電流源は、電力が装置または回路の一部に供給されるかどうかを制御する外部NFETを駆動する。NFETに供給される最大電圧およびターンオンランプ率はプログラム可能であるため、NFETは外部の保護装置を必要とせずにその定格制限内で安全に動作することができる。高圧出力端子が外部NFETを駆動するのに必要とされない場合、別の実施例に従った出力端子は、開放ドレインロジック出力端子として機能するように構成され得る。  (もっと読む)

(もっと読む)

双方向スイッチの駆動電源回路

【課題】絶縁電源の個数を減少させて装置全体の小型軽量化、低コスト化を可能にした双方向スイッチの駆動電源回路を提供する。

【解決手段】逆阻止IGBT1,2が逆並列接続された双方向スイッチを駆動するために、各IGBT1,2の駆動回路に電源を供給する双方向スイッチの駆動電源回路に関する。逆阻止IGBT1の駆動回路23に電源を供給する直流電源19と、逆阻止IGBT2の駆動回路24に電源を供給するコンデンサ22と、直流電源19とコンデンサ22との間に直列に接続され、かつ、そのオン時に逆阻止IGBT1を介して直流電源19によりコンデンサ22を充電する駆動電源用半導体スイッチとしてのPチャンネルMOSFET20と、を備える。

(もっと読む)

貫通防止機能検査方法

【課題】同期整流機能を有する半導体集積回路の同期整流開始時及び終了時の貫通防止機能の測定結果を選択可能にし、貫通防止機能の検査を誤りなく実施する。

【解決手段】同期整流機能を有する出力回路の出力部に電源Vcc1よりも高い電圧で駆動する電流源9と、測定器8と、測定電圧と予め設定の電圧VRとを比較するコンパレータ10を接続する。コンパレータ10の出力は遅延時間を設定できる遅延回路11と演算器12の入力に接続され、演算器12は測定器8へトリガセット信号を出力する。遅延回路11の遅延時間を制御することにより、任意区間における貫通防止機能を選択して検査を実施する。

(もっと読む)

ハーフブリッジ回路またはフルブリッジ回路内の電圧をモニタすることによる、双方向の電流検出

【課題】パワー回路内に検出素子を挿入することなく、ドライバーICと集積化でき、双方向の電流を特定できるようにする。

【解決手段】 一般にMOSFETである高電圧側トランジスタスイッチおよび低電圧側トランジスタスイッチを含む、ブリッジ接続され、スイッチングされるトランジスタ出力回路における出力電流を測定するための装置および方法である。高電圧側スイッチと低電圧側スイッチの間の共通ノードにおける電圧を検出し、電圧が当該すべての正の出力電流または負の出力電流に対して電圧が正となるように、所定の値だけ、第1回路においてオフセットする。この出力電流は、低電圧側スイッチがオンとなっている時間に対する所定の時間に限り、オフセット電圧信号を受信する第2回路において測定する。第1回路は、電流基準ソース/レベルシフターと、特定の回路構造の複数のトランジスタから形成された電流ミラー回路とを含む。第2回路は、所望する時間にゲートNMOSトランジスタにより、第1回路の出力に結合され、電流測定信号を発生する。この第2回路は、第1電流基準ソースと実質的に同じ電気特性を有する第2電流基準ソースと、入力側回路のトランジスタにそれぞれマッチングされ、同じ回路構造に接続された複数の第2トランジスタとを含む。第2回路では、オフセット信号と高基準信号および低基準信号とを比較し、出力電流がそれぞれ正方向または負方向に過電流の限界を超えているかどうかの表示を発生する。検出回路は、単一IC内の出力回路のゲートドライバーと一体的にすることが望ましい。

(もっと読む)

ブートストラップ・キャパシタのリフレッシュ回路

ブートストラップ・キャパシタ充電回路は、ハーフブリッジ型に配置され、高圧側電位と低圧側電位との間に導かれた第1および第2のパワー・スイッチング・トランジスタと、前記第1および第2のトランジスタを駆動する駆動回路と、電位発生源から充電されるように配置され、電圧源を提供して電子回路に電力供給するブートストラップ・キャパシタと、前記高圧側電位および低圧側電位の一つから前記ブートストラップ・キャパシタへの充電経路を提供する充電回路と、前記第1および第2のトランジスタの共通端子と前記高圧側電位および低圧側電位の一つとの間に配置された第1および第2の直列に接続されたスイッチと、前記ブートストラップ・キャパシタは、前記充電回路により充電されるように結合された第1端子、および前記第1および第2の直列に接続されたスイッチの間の共通ノードに結合された第2端子を有し、第1および第2モードで動作する制御回路であって、前記第1および第2のパワー・スイッチング・トランジスタが所与の周期でスイッチする第1モードにおいて、前記第1および第2のパワー・スイッチング・トランジスタの前記共通端子に接続された前記第1のスイッチをONにし、前記第2のスイッチをOFFに制御する制御回路とを備え、プリセット期間を超える時間の間、前記第1のパワー・スイッチング・トランジスタがONの場合に、前記制御回路は第2モードで動作し、前記第1および第2のスイッチが、第1および第2の所与の時間期間で交互にON/OFFすることにより、前記ブートストラップ・キャパシタが、前記第2スイッチおよび前記充電回路を介して、前記第2の所与の時間期間の間充電する。  (もっと読む)

(もっと読む)

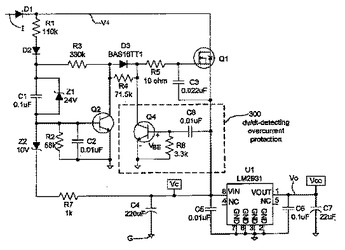

電源のためのDV/DT検出過電流保護回路

制御電極および2つの主電極を備えている電力切換トランジスタ用の過電流保護回路において、電力切換トランジスタの主電極の1つにおいて時間に対する電圧の変化率を検出し、変化率が所定値を上回った場合に、保護スイッチを制御して、電力切換トランジスタの制御電極に対する制御信号を取り除き、電力切換トランジスタをオフにする、保護スイッチを含む回路を備えている。  (もっと読む)

(もっと読む)

ダイナミックバックゲートバイアスを伴うブートストラップダイオードエミュレータ

【解決手段】ハーフブリッジスイッチング回路で使用するためのブートストラップダイオードエミュレータ回路が提供される。スイッチング回路は、負荷ノードにおいてトーテムポール構造の形で互いに繋がれているトランジスタと、これらのトランジスタを駆動するための駆動回路と、高圧側駆動回路に電力を供給するためのブートストラップコンデンサとを含む。ブートストラップダイオードエミュレータ回路は、ゲート、バックゲート、ソース、およびドレインを有し、そのドレインを高圧側供給ノードに結合され、そのソースを低圧側供給ノードに結合されているLDMOSトランジスタと、LDMOSトランジスタのゲートに電気的に結合されているゲート制御回路と、LDMOSトランジスタのバックゲートに電気的に結合されているダイナミックバックゲートバイアス回路とを備える。ダイナミックバックゲートバイアス回路は、LDMOSがオンにされたときに、LDMOSトランジスタのドレインの電圧に近いけれども同電圧よりも僅かに低い電圧をLDMOSトランジスタのバックゲートに印加することによって、LDMOSトランジスタのバックゲートを動的にバイアスするように動作可能である。 (もっと読む)

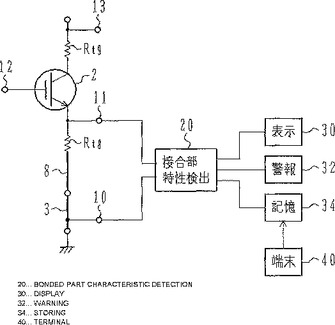

パワー半導体モジュール及びそれを用いた電力変換装置並びに移動体

本発明の目的は、小型で、しかも、金属接合部の劣化を精度良く検知できる半導体素子を用いたパワー半導体モジュール及びそれを用いた電力変換装置並びに移動体を提供することにある。パワー半導体素子(2)の表面電極と電極用の金属板(3)は、金属ワイヤ(8)により金属接合される。接合部特性検出回路(20)は、金属接合の接合部の特性を検出し、接合部の劣化による抵抗RT8の上昇と寿命の関係から決定したしきい値VLを用いて、接合部の劣化を予測する。  (もっと読む)

(もっと読む)

電源回路におけるRFI、EMIおよびノイズ過渡現象を分離する方法および装置

【構成】電源回路におけるRFI、EMI、およびノイズ過渡現象を分離および/または排除する方法、装置である。交互にゲート制御される複数の平行な電流路(A、B)を利用することによって、DC/DC結合およびAC/DC結合を分離する。スイッチ(12、14、16、18)のゲート制御を制御モジュールで行うと、任意の時点で本発明回路の入力および出力を確実に電磁的に遮断できると同時に、回路の出力負荷に電流を適正かつ連続的に供給することを確実に担保できる。 (もっと読む)

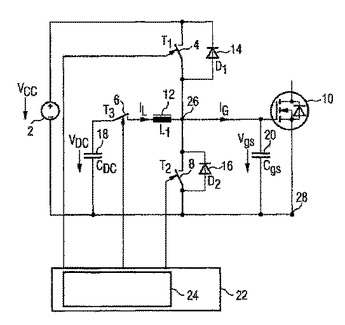

半導体スイッチの高周波制御

共振ゲート・ドライバ回路は、例えばMOSFETの効率的なスイッチングを実現する。しかし、共振ゲート・ドライバ回路の動作は、しばしば、高いスイッチング周波数が必要とされる応用分野を可能としない。本発明によれば、共振ゲート・ドライバ回路のインダクタのプリチャージが実行される。これは、MOSFETの非常に効率的かつ高速な動作を可能にする。  (もっと読む)

(もっと読む)

コモンモード制御を備えた差動チャージポンプ

入力信号によってフィルタを充電及び放電するための出力電流を供給するチャージポンプであって、前記チャージポンプは、第1の電流源であって、該電流源を駆動するための前記入力信号と接続可能であり、定電流I0に可変電流Δxを加えたものに等しい第1の電流を供給するように構成された第1の電流源を有し、前記可変電流Δxは前記入力信号に正比例し、前記チャージポンプは更に、第2の電流源であって、該電流源を駆動するための前記入力信号に接続可能であり、定電流I0から可変電流Δxを減じたものに等しい第2の電流を供給するように構成された第2の電流源と、前記出力電流を供給する出力部と、を有し、前記出力部は、前記出力電流が前記第1の電流と前記第2の電流との差に等しくなるように、前記第1及び第2の電流源の両方に接続されたチャージポンプ。  (もっと読む)

(もっと読む)

並列なMOSFETに対する障害予測

電源変換回路は、しばしば並列に動作するいくつかのMOSFETからなる。温度サイクリングと機械動作とが原因で、MOSFET又はMOSFETにおける各電子接続は故障する場合がある。本発明によれば、複数の並列なMOSFETに対する診断回路が与えられ、それが、MOSFETの温度又はMOSFETのゲート電圧の少なくとも一方に基づき、起こりうる障害を予測又は決定する。有利には、MOSFETの連続的な監視が与えられることができ、MOSFETの障害の早期決定が与えられることができる。  (もっと読む)

(もっと読む)

半導体スイッチの高周波制御

共振ゲートドライバ回路は、例えば、MOSFETの効率的なスイッチングを提供する。しかし、共振ゲートドライバ回路は、高いスイッチング周波数が必要とされる用途を可能にさせないことがしばしばある。本発明によれば、共振ゲートドライバ回路のインダクタのプリチャージングが実行される。これは、MOSFETの極めてエネルギー効率が良い高速な動作を可能にさせる。  (もっと読む)

(もっと読む)

701 - 720 / 722

[ Back to top ]