Fターム[5J039FF03]の内容

パルスの操作 (9,993) | パルス特性(個々のパルス) (109) | ピーク値 (32)

Fターム[5J039FF03]に分類される特許

1 - 20 / 32

ホールド回路

【課題】広い動作電圧範囲で精度よく動作するホールド回路の提供。

【解決手段】入力信号端子と、出力電圧出力端子と、非反転入力端子に入力信号端子が接続された増幅器と、入力端子に増幅器出力端子が接続された反転増幅器と、一端に増幅器反転入力端子が接続され他端に基準電位が接続されたキャパシタと、入力端子にキャパシタの一端が接続されたバッファ回路と、ゲートに増幅器出力端子が接続されソースにバッファ回路出力端子が接続されバルクに電圧源が接続された第1トランジスタと、ゲートに反転増幅器出力端子が接続されソースおよびバルクに電圧源が接続されドレインに第1トランジスタドレイン端子が接続された第2トランジスタと、ゲートに反転増幅器出力端子が接続されソースおよびバルクに第1トランジスタドレイン端子と第2トランジスタドレインとが接続されドレインにキャパシタの一端が接続された第3トランジスタと、を有するホールド回路。

(もっと読む)

ピークホールド回路及びボトムホールド回路

【課題】ピークホールド回路及びボトムホールド回路の検出精度を高め、高温動作における当該回路の検出精度の劣化を抑制すること。

【解決手段】各ゲートに入力端子1と出力端子2が接続される第1の差動入力回路7と、第1のカレントミラー回路10を備える第1の差動増幅回路12と、第1のカレントミラー回路10に流れる電流I1に比例する充電電流I2を生成する第5のトランジスタ13と、ゲートが第1の差動増幅回路12の出力ノード16に接続され、ソースとドレインがそれぞれ第5のトランジスタ13のドレインとキャパシタ17に接続される第6のトランジスタ14と、充電電流I2を充電するキャパシタ17を備え、出力電圧VOUTが入力信号VINのピーク値に近づくに従って充電電流I2を減少させることで、ピークホールド回路の過剰の行き過ぎを抑制し、検出精度を高めた。

(もっと読む)

ピークホールド回路

【課題】一定期間内のピーク振幅を安定して保持することができるピークホールド回路を提供する。

【解決手段】変調された入力信号と該入力信号のDC電位とを入力して比較する第1の比較器2と、入力信号と所定の参照電圧とを入力して比較する第2の比較器2と、第1の比較器1からの出力と第2の比較器2からの出力とを入力し、AND出力結果に基づいて第2のスイッチ素子7をオン・オフ制御して、保持用コンデンサ5に入力信号のピーク振幅のDC電位を保持させる第2の論理回路(AND回路)4とを有している。

(もっと読む)

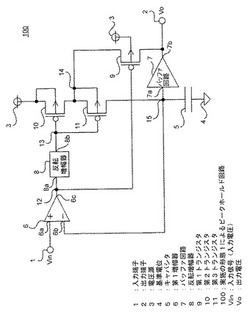

最大・最小電圧検出回路

【課題】複数の被測定電圧の中の最大値又は最小値を検出する為の最大・最小検出回路に関し、最大値検出時と最小値検出時との主要回路部分を共通として切替える。

【解決手段】被測定電圧V1〜Vnをそれぞれ一方の入力端子に印加し、最大電圧又は最小電圧を検出処理する制御処理部CONTに入力される電圧を他方の入力端子に印加して比較出力する複数の演算増幅器OPA1〜OPAnと、これらの演算増幅器OPA1〜OPAnの出力端子と制御処理部CONTとの間に順方向極性のダイオードD12〜Dn2と逆極性のダイオードD11〜Dn1又は寄生ダイオードが順方向と逆方向となるように接続した電界効果トランジスタとについて、何れか一方を選択接続するように切替制御を行う構成を備えている。

(もっと読む)

ピークホールド回路

【課題】ピークホールド回路の構成を簡素化する。

【解決手段】ピークホールド回路10は、複数の入力信号(IN1,IN2,Vref)のうち最大レベルの入力信号に応じた大きさの出力信号Voutを出力する最大レベル検出手段20と、第1電極d1と、固定電位が供給される第2電極d2とを有する容量素子C1と、を備え、最大レベル検出手段20は、複数の入力信号(IN1,IN2,Vref)のうち最大レベルの入力信号のレベルに応じた電位を生成する電位生成部50と、オープンドレイン形式のトランジスタであって、電位生成部50で生成された電位がゲートに供給され、電源電位VDDがソースに供給され、容量素子C1の第1電極d1にドレインが接続される出力トランジスタToと、を具備する。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22と判定クロック端子23とリセット端子24と温度補償クロック端子25と2値化出力端子26と遅れ出力端子28とピークホールド回路30とボトムホールド回路40と2値化判定回路120と入力信号検出回路130と停止判定回路140を備えている。2値化回路10では、停止判定信号が入力信号の停止期間を検出し、この停止期間にピークホールド回路30とボトムホールド回路40が、各々の記憶値を入力信号に追従して変化させる。これによって、停止期間に、入力信号がピークホールド回路30とボトムホールド回路40の記憶値から算出される閾値を越えて変化することが抑制され、停止期間に2値化出力が反転することが抑制される。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22とリセット端子24と第1出力端子26と第2出力端子28と判定クロック端子27とピークホールド回路30とボトムホールド回路40と出力信号生成回路120と補償信号生成回路130を備えている。出力信号生成回路120は、入力端子20に入力される入力信号が短周期で変化する稼動期間に、ピークホールド値減少信号をピークホールド回路30に出力し、ボトムホールド値増加信号をボトムホールド回路40に出力する。補償信号生成回路130は、入力信号が短周期で変化しない停止期間に、補償信号をピークホールド回路30とボトムホールド回路40に出力する。これによって、入力信号の状態に関わらず入力信号を適切に2値化することができる。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】受信した差動信号RX+,RX−の電位振幅が所定値を超えているときその検出信号Vpをパルスとして出力するピーク検出回路11と、ピーク検出回路11から出力する検出信号Vpのパルス幅を差動信号RX+,RX−の少なくとも1周期分延長するパルス幅延長回路12とを備える。ピーク検出回路11は、差動信号RX+,RX−に同一のDCバイアスを与えた後にその差分に対応する電圧信号Vdataを出力する入力差動増幅回路11Aと、入力差動増幅回路11Aのほぼレプリカ回路として構成され、参照電圧Vref’をレベルシフトしたシフト参照電圧Vrefを出力するレプリカ参照電圧生成回路11Bと、電圧信号Vdataとシフト参照電圧Vrefとを比較して検出信号Vpを出力する電圧比較回路11Cと、を備える。

(もっと読む)

ホールド回路

【課題】 低消費電力化が可能なホールド回路を提供する。

【解決方法】 ピークホールド回路2では、信号保持用のコンデンサ10の一方の電極と入力端子20の間に、スイッチ回路4が形成されている。スイッチ回路4は絶縁ゲート型トランジスタ5を備えており、ゲート電極5cが切換回路15に接続されている。絶縁ゲート型トランジスタ5は切換回路15によって制御され、出力電圧Voutのピーク電圧を保持する際に絶縁ゲート型トランジスタ5を遮断する。コンデンサ10に蓄えられた電荷が変動することなく、出力電圧Voutのピーク電圧が保持される。また、切換回路15はリセット端子19に接続されており、出力電圧Voutをリセットする際に、絶縁ゲート型トランジスタ5を遮断する。入力端子20からGNDへと貫通電流が流れることがない。消費電力が抑制される。

(もっと読む)

ピークホールド回路

【課題】高速動作に適し、且つピーク検出の精度を向上できるピークホールド回路を提供する。

【解決手段】第1ピークホールド回路20aは、入力信号Vinが供給される入力トランジスタQ1と、入力信号Vinのピーク値をホールドするコンデンサC1と、コンデンサC1の保持電圧が供給されるオペアンプ26と、補正用トランジスタQ2とを備える。また、入力トランジスタQ1に流れる電流を検出する電流検出回路30と、電流検出回路30において検出された電流のピーク値をホールドし、電流Ipとして補正用トランジスタQ2に供給するピーク電流ホールド回路35とを備える。

(もっと読む)

ピークレベル検出装置

【課題】1ビットオーディオ信号のピーク値を求めることを、低演算量かつ高精度で実現可能な装置を提供すること。

【解決手段】1ビットストリームが供給されるとディレイバッファ30に順次データが書き込み記憶される。そして、ピーク位置検出部10が、ディレイバッファ30に記憶されたピーク値のアドレスである最大ピークアドレスを検出しこれをデータ読み出し部20に送る。データ読み出し部20は、送られてきた検出された最大ピークアドレスに応じてディレイバッファ30の対応するデータを読み出す。そして、LPF40は、この読み出されたデータの低域を通過させ、最後にABS部50が信号を絶対値化してマルチビットピーク値を出力する。

(もっと読む)

充放電回路および2値化回路

【課題】RSSIを使用したASK信号の復調時においても、2値化の閾値と比較される入力信号の振幅を一定に保つ。

【解決手段】RSSI検波器17にて復調されたASK信号はピークホールド回路23に入力され、ピークホールド回路23は、充放電部24に入力される入力信号のピーク値を検出し、クリップ回路22は、充放電部24に入力される入力信号のピーク値から一定値以下のレベルをクリップし、充放電部24は、クリップ回路22にてクリップされた信号を用いてコンデンサC2を急速充放電することで、コンパレータ27の閾値として用いられる基準電圧Vrefを発生させる。

(もっと読む)

ヒステリシスコンパレータ

【課題】入力信号の振幅が当初の想定よりも小さい場合や入力信号の振幅変動が生じた場合でも、適正な出力信号を得ることができるヒステリシスコンパレータを提供する。

【解決手段】電圧レベルが連続的に変化する入力信号を互いに異なる電圧レベルを有する2つの閾値電圧に基づいて2値化判定し、この判定結果に応じた出力信号を生成するヒステリシスコンパレータであり、入力信号のトップピークを検出し、トップピークに応じたトップピーク検出電圧を生成するトップピーク検出部と、入力信号のボトムピークを検出し、ボトムピークに応じたボトムピーク検出電圧を生成するボトムピーク検出部と、トップピーク検出電圧の電圧レベルとボトムピーク検出電圧の電圧レベルの範囲内で第1および第2の閾値電圧を生成する閾値電圧生成部と、第1および第2の閾値電圧と入力信号の電圧レベルを比較して入力信号を2値化判定し、この判定結果に応じた出力信号を生成する電圧比較部と、を含む。

(もっと読む)

パワーデバイスドライブ装置

【課題】ソフトシャットダウン機能を有するパワーデバイスドライブ装置の出力端子とパワーデバイスを接続する信号線を短縮化する。

【解決手段】パワーデバイスドライブ装置50には、光結合部1とパワーデバイスドライブ回路部2が設けられる。パワーデバイスドライブ回路部2には、ドライバ部21、ディセイブル回路22、I/V変換回路23、サンプルホールド回路24、ソフトシャットダウン回路25、制御端子PDisb、Vcc端子PVcc、Vo端子PVo、及びVss端子PVssが設けられる。IGBT4の短絡等の異常事態が発生したとき、制御信号Ssetがディセイブル状態となる。ディセイブル状態の制御信号Ssetがディセイブル回路22に入力され、出力部から出力される信号がHz状態となり、ソフトシャットダウン回路25のNch MOSトランジスタNMT3が“ON”しIGBT4をソフトシャットダウン状態にする。

(もっと読む)

ピークホールド回路、オペアンプ

【課題】ピークホールド回路を提供する。

【解決手段】入力端子102は、CMOSインバータ103の入力端子に接続されている。CMOSインバータ103の出力端子は、NMOS107のゲートに接続されている。NMOS107のソースは接地され、ドレインは抵抗106の一端、コンデンサ108の一端、CMOSインバータ105の入力端子、および出力端子109に接続されている。抵抗106の他端は、図示されていない駆動電源に接続されている。コンデンサ108の他端は、接地されている。NMOS107は、電圧Vinと電圧Voutに依存してオン、オフが制御される。本発明はピークホールド回路に適用できる。

(もっと読む)

メータ駆動回路

【課題】 ゲインリダクションメータとゲインメータに同じ構成のメータ駆動回路を使用しても、ゲインリダクションメータにおいて圧縮率の極小値を明確に認識できること。

【解決手段】 メータ駆動回路40は、入力されたエンベロープ信号を反転してエンベロープフォロワ部40bに入力することのできる第1の選択部SWaと、エンベロープフォロワ部40bの出力を反転してゲインリダクションメータに供給することのできる第2の選択部SWbを備えている。

(もっと読む)

パルス検出回路、包絡線検出回路、および、電子装置、ならびに、パルス検出方法

【課題】IRのような素子性能の限界に及ぶ超高周波域で良好に動作し消費電力が少なく安価で信頼性が高く且つ通常のCMOS半導体プロセスで製造可能な新たなルス検出回路、包絡線検出回路および電子装置ならびにパルス検出方法を提供することを目的とする。

【解決手段】ゲートおよびドレインを短絡したMOSトランジスタ103(108)が介挿された負帰還路を有する増幅回路20a(20b)と、増幅回路の入力端に一端側が接続され他端側が被検出信号が供給される信号入力端として設定されたコンデンサ105(110)とを含み、信号入力端に供給される被検出信号(Vs)の波形をその変動における一方の極性側のピークレベルが略一定に揃い且つ他方の極性側に向けて当該変動に相応する振幅変化を呈する波形に変換する信号波形変換部と、信号波形変換部10a(10b)の出力信号から被検出信号が担うパルスを検出するパルス検出部とを備える。

(もっと読む)

光センサ回路および光センサアレイ

【課題】光センサ回路のレイアウト面積を増大させることなく、光センサ回路の消費電流を一定に保ち、熱平衡状態を維持することのできる光センサ回路および光センサアレイを提供する。

【解決手段】光センサ回路は受光した光量に応じた値の光電流を生成する光電変換手段,増幅回路,増幅回路の入出力端子間に接続されて前記光電流を積分するコンデンサおよびコンデンサの両端に接続されたリセットトランジスタを有し、リセットトランジスタを待機モードでオンさせる。また、この光センサ回路を複数有する光センサアレイについても適用できる。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】スケルチ検出回路は、差動信号の電位振幅が、スケルチレベルを超えているかどうかを検出し、その検出信号を出力するピーク検出回路と、検出信号のパルス幅を、そのパルス幅の時間を含めて、差動信号のデータの1周期分の時間以上の時間だけ延長するパルス幅延長回路とを備える。ここで、ピーク検出回路は、差動信号の電位振幅に応じた電位を持つ第1および第2の信号を出力する入力アンプ回路と、入力アンプ回路と同一構成であり、スケルチレベルに相当するリファレンス電圧に応じた電位を持つ第3および第4の信号を出力するレプリカアンプ回路と、第1および第2の信号に応じて流れる合成電流と第3および第4の信号に応じて流れる固定電流とを比較し、その電流差に応じて、差動信号の電位振幅がリファレンス電圧を超えているかどうかを表す検出信号を出力する電流比較回路とを備える。

(もっと読む)

2値化回路

【課題】 アナログ信号を2値化する際に、高周波成分が重畳していてもチャッタリングせず、アナログ信号が閾値Vrefを超えるタイミングで反転する2値化信号を出力する回路を提供する。

【解決手段】 アナログ信号Viが閾値Vrefを下回った時とそれよりも高く設定されている高側オフセット閾値Vref1を上回った時に反転する第1比較回路10と、アナログ信号Viが閾値Vrefを上回った時と閾値Vrefよりも低く設定されている低側オフセット閾値Vref2を下回った時に反転する第2比較回路20と、第1比較回路10と第2比較回路20の出力信号を入力し、アナログ信号値Viが閾値Vrefを下回った時に生じた第1比較回路10の反転現象と、アナログ信号値Viが閾値Vrefを上回った時に生じた第2比較回路20の反転現象を選択して出力を反転させる選択回路30を備えている。

(もっと読む)

1 - 20 / 32

[ Back to top ]