Fターム[5J039JJ20]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 比較結果の出力(アナログ) (180) | デジタル出力 (138)

Fターム[5J039JJ20]に分類される特許

61 - 80 / 138

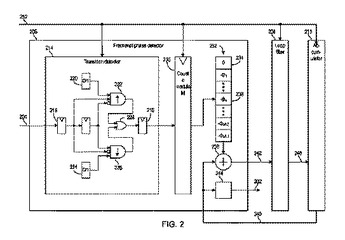

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

周波数異常検出回路

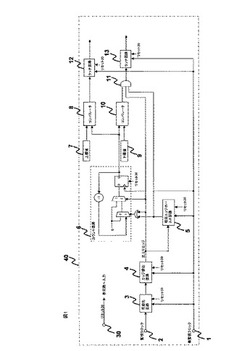

【課題】従来の、監視クロックが被監視クロックよりも高い周波数を使用する周波数異常検出回路は、高コストかつノイズ対策が必要で実装が困難であり、また、監視クロックが被監視クロックよりも低い周波数を使用する周波数異常検出回路は、クロック固着のタイミングによっては異常を検出できないだけでなく、リセット時にシフトレジスタを構成するすべてのレジスタ出力が“0”となるので、警報が発出されないようにする構成を別途設けなければならない問題があった。

【解決手段】クロック周波数の上限異常は被監視クロック数のカウント数と上限値との大小比較にて検出し、下限異常は、同期化した監視クロックの立ち上がりエッジにて出力する正極性パルスと、当該パルス出力で”High”を出力する初回エッジホールド回路出力と、下限値と被監視クロック数のカウント値の大小を比較するコンパレータ出力との論理積の出力にて検出すること。

(もっと読む)

位相制御回路

【課題】 データ信号とクロック信号がどのような位相差であっても位相差に応じたパルス幅の位相差信号を出力する。

【解決手段】 データ信号および反転した信号Yを入力し、反転した信号Yをデータ信号の遷移タイミングで保持して信号Xを出力する第1の保持手段と、クロック信号および信号Xを入力し、信号Xをクロック信号の遷移タイミングで保持して信号Yを出力する第2の保持手段と、信号Xおよび信号Yを入力し、その位相差に応じたパルス幅を有する位相差信号を生成し、データ信号とクロック信号の位相差に応じたパルス幅を有する位相差信号として出力する比較手段とを備える。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

位相調整回路

【課題】大きな位相ずれにも対応可能な位相調整回路を提供する。

【解決手段】基準となるクロック信号CLKeに同期して与えられる画像データDATAeとデータイネーブル信号DEeは、このクロック信号CLKeで動作するFF31,33,38,40で2クロック分遅延され、画像データDTeと共通のデータイネーブル信号DEとして出力される。位相調整の対象となるクロック信号CLKoに同期して与えられる連続する2つの画像データDATAoは、それぞれFF34,35によって2クロック周期の間保持される。FF34,35の保持データは、セレクタ37によっていずれか一方が選択出力され、基準となるクロック信号CLKeのタイミングでFF39に保持されて画像データDToとして出力される。これにより、位相のずれがクロック周期よりも小さければ、2系統の画像データは同位相になるように位相調整ができる。

(もっと読む)

フリップフロップ回路

【課題】不感帯が少なく高速安定動作が可能なフリップフロップ回路を提供すること。

【解決手段】本発明は、データ信号Dと、立ち上がり遅延クロック信号CKdとを入力し、データ信号Dの立ち下がりと立ち上がり遅延クロック信号CKdの立ち下がりとによって内部ノードNCの信号を立ち上げる第1のラッチ回路L1と、内部ノードNCの信号とクロック信号CKとを入力し、内部ノードNCの信号が立ち上がっている状態でクロック信号CKが立ち下がるタイミングにより内部ノードXの信号を立ち下げる第2のラッチ回路L2と、内部ノードXの信号とクロック信号CKとを入力し、クロック信号CKが立ち上がっている状態でのデータ信号Dを保持する出力信号を生成するための第3のラッチ回路L3と、内部ノードNCの信号を立ち上がり遅延クロック信号CKdによってプルダウンさせるプルダウン回路PDとを備えるフリップフロップ回路である。

(もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

物体検出回路及びそれを備えた物体検出装置

【課題】受光素子にて検知されたパルス光の波長が判別可能であり、外乱光による影響をさらに低減し、検出精度の高い物体検出回路を実現する。

【解決手段】物体検出回路1は、パルス変調された光を照射する発光素子12と、被検出物体の有無に応じて発光素子12からの出力パルス光を受光する受光素子13と、受光素子13にて検知されたパルス光の波長を判別する信号検出回路19とを備える。

(もっと読む)

イコライザのテスト回路および集積回路の評価システム

【課題】量産テストでの使用に適したイコライザのテスト回路および集積回路の評価システムを提供する。

【解決手段】テスト回路1は、擬似乱数データ生成部11が、擬似乱数データを生成し、重み付け係数生成部12が、符号間干渉の干渉強度設定用の重み付け係数を生成し、擬似符号間干渉データ生成部13が、擬似乱数データのビット系列に応じて擬似乱数データに擬似的な符号間干渉を発生させ、重み付け係数により振幅を変化させた擬似符号間干渉データを生成し、ドライバ14が、生成された擬似符号間干渉データを差動信号として出力する。比較部15は、イコライザ100の出力をサンプリング回路200によりサンプリングしたデータを、符号間干渉発生前の元の擬似乱数データと比較し、カウント部16が、比較部15により検出された不一致の数をカウントする。

(もっと読む)

位相比較器及び測定装置

【課題】2つの信号の位相比較結果を確実に保持できる位相比較器を提供する。

【解決手段】2つの信号CMP、REFの位相を比較して、その位相関係を出力する比較部10と、比較部より出力される位相比較結果を入力信号として受信し信号OUTとして出力するホールド回路30と、比較部の出力に基づいて位相比較結果が確定したか否かを判定し、位相比較結果が確定したと判定した場合にホールド信号Cを出力するホールド信号生成部20とを備え、ホールド回路は、ホールド信号が出力されている期間は前記入力信号を保持するようにして、比較部による位相比較結果が確定する前に状態が保持されることを防止し、位相比較結果を確実に保持できるようにする。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

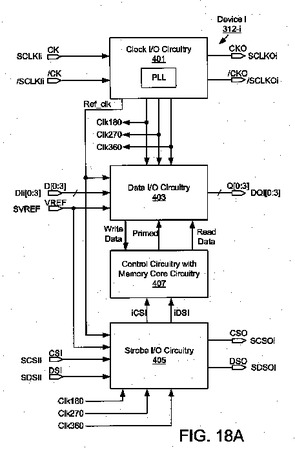

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。  (もっと読む)

(もっと読む)

短絡検出回路

【課題】本発明は、コストアップや電力損失を招くことなく、プッシュプル回路の出力短絡を検出することが可能な短絡検出回路を提供することを目的とする。

【解決手段】本発明に係る短絡検出回路は、パルス信号Vxと同期したダミーパルス信号Vyを生成し、両信号間に所定の位相差が生じているか否かに応じて、OUT1P端子の短絡検出を行う構成とされている。

(もっと読む)

半導体記憶装置

【課題】入力データとデータストローブクロックのタイミングにより自動的にデータ入力ストローブ信号の発生タイミングをチューニングする半導体記憶装置を提供する。

【解決手段】入力データとデータストローブクロックの入力タイミングによりデータ入力ストローブ信号の発生タイミングをチューニングする内部チューニング手段と、前記データ入力ストローブ信号に応答して、複数のデータをグローバルラインに伝送するデータ入力センスアンプとを含む。

(もっと読む)

アナログ信号比較器

【課題】アナログ信号の値を、比較的簡易な回路でかつ短時間で、所定の値と比較する。

【解決手段】所定時間経過後にしきい値を超える基準信号を生成する波形生成回路51Aと、アナログ信号を入力し当該アナログ信号を積分してアナログ積分信号を出力する積分回路52と、前記波形生成回路51Aからの基準信号と、前記積分回路52からのアナログ積分信号とを入力し、前記波形生成回路51Aからの基準信号が所定値に達するまでの時間と積分回路52からのアナログ積分信号が所定値に達するまでの時間とを比較する比較回路と、を備えたことを特徴とするアナログ信号比較器。

(もっと読む)

アナログ信号比較器

【課題】

アナログ信号の値を、比較的簡易な回路でかつ短時間で、所定の値と比較する。

【解決手段】

第1のパルス信号を生成する発振器21Aと、アナログ信号を入力し当該アナログ入力信号を第2のパルス信号に変換して出力するVCO22と、発振器21からの第1のパルス信号を入力する第1のシフトレジスタ241と、VCO22からの第2のパルス信号を入力する第2のシフトレジスタ242と、第1および第2のシフトレジスタ241,242の全ビットまたは一部ビットの値を検出し、これらの検出値に基づき、発振器21Aが生成する第1のパルス信号の個数と、VCO22が生成する第2のパルス信号の個数とを比較するパルス個数比較回路とを備えたことを特徴とするアナログ信号比較器。

(もっと読む)

61 - 80 / 138

[ Back to top ]