Fターム[5J039JJ20]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 比較結果の出力(アナログ) (180) | デジタル出力 (138)

Fターム[5J039JJ20]に分類される特許

81 - 100 / 138

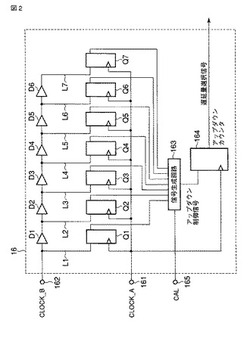

位相検出回路及びデータ処理装置

【課題】回路構成が簡素化され、低消費電力化され集積回路化する上で有利な構成の回路を得る。

【解決手段】第1クロックが各クロック入力端に与えられる複数段のフリップフロップ回路(Q1−Q7)と、第2クロックが入力される直列接続された複数段の遅延素子(D1−D6)と、前記複数段の遅延素子の出力をそれぞれ、前記複数段のフリップフロップ回路の各データ入力端に与える接続部(L1−L7)と、前記複数段のフリップフロップ回路の出力データが入力され、この出力データ内容に応じて変化する制御信号を得る信号生成回路(163)と、前記信号生成回路からの制御信号に応じて、前記第1若しくは第2クロックを相調整する位相調整信号を出力する位相調整信号出力部(164)を有する。

(もっと読む)

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

パルス幅測定方法および回路

【課題】入力パルスのデューティが測定可能となり、回路構成が簡素化できるようにする。

【解決手段】HレベルとLレベルとを繰り返す入力パルスを同一遅延時間でn+1段に亘って遅延させてn+1相の遅延パルスを生成し、該n+1相の各遅延パルスのそれぞれがHレベルであるかLレベルであるかに応じて変化し、且つ所定のタイミングにおいて、前記入力パルスのHレベル側又はLレベル側のパルス幅を示すエンコード信号を生成し、前記所定のタイミングにおける前記エンコード信号を、前記Hレベル側又はLレベル側のパルス幅信号として保持する。

(もっと読む)

オーバーサンプリング型CDR

【課題】キャリブレーション中であってもデータ受信を可能とする。

【解決手段】本発明は、位相のずれた第1クロック及び第2クロックを含む多相クロックが入力されるオーバーサンプリング型CDRであって、入力信号及びクロックが入力され、クロックのタイミングに合わせて入力信号を取り込んで出力信号を出力する第1差動対及び第2差動対と、第1差動対がキャリブレーション時に第1クロックを第2差動対に出力するクロックセレクタと、を備え、第1差動対は、クロックとして第1クロックが入力されると、第1クロックのタイミングに合わせて入力信号を取り込んで前記出力信号として第1データ出力信号を出力し、第2差動対は、クロックとして第1クロックが入力されると、第1クロックのタイミングに合わせて入力信号を取り込んで出力信号として第1データ出力信号を出力するものである。

(もっと読む)

位相差計測回路

【課題】2つの信号の進み遅れに関係なく、遷移タイミングの差を測定することができる位相差計測回路を提供する。

【解決手段】EXOR11により、デジタル信号S1,S2の位相差に対応したパルス幅の信号S3が出力される。信号S3は、インバータ12で反転された信号S4と共にセレクタ13に与えられ、選択信号SELに従っていずれか一方が選択され、ゲート制御用の信号S5としてADN14に与えられる。AND14には連続したクロック信号CLKが与えられており、信号S5でゲート制御されたクロック信号CLKが、信号S6としてカウンタ15に与えられる。カウンタ15は、信号S6のパルス数をカウントし、カウント値CNTを出力する。選択信号で信号S3,S4を選択することにより、デジタル信号S1,S2の進み遅れに関係なく、遷移タイミングの差を測定できる。

(もっと読む)

電圧制御発振器を内蔵したPLL(PhaseLockedLoop)回路の位相差検出回路

【課題】低電圧動作時においても、VCO信号と基準信号との位相差を検知し、その位相差に対応したデジタル信号を生成する位相比較器を提供する。

【解決手段】基準信号と対象信号との位相差をデジタル信号として出力する位相比較器において、前記位相差に対応したパルス幅の信号により第1容量素子を充電することによって前記位相差を電荷として検出する第1検出手段と、前記基準信号の周期に対応したパルス幅の信号により第2容量素子を充電することによって基準となる時間差を基準電荷として検出する第2検出手段と、前記第1検出手段により検出された電荷と前記第2検出手段により検出された電荷とを比較する電荷比較手段と、前記電荷比較手段による比較結果により、前記第2容量素子に充電された電荷に対する前記第1容量素子に充電された電荷の比をデジタル信号として出力する出力手段と、を備える。

(もっと読む)

半導体集積回路およびイコライザの制御方法

【課題】回路規模の増大を抑制しつつ、受信したデータ信号の等化量を調整することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、イコライザと、イコライザにより等化されたデータ信号の位相を検出しこのデータ信号の位相と復元クロック信号の位相とを比較し、等化されたデータ信号のビット幅が復元クロック信号の周期よりも小さいときは第1の比較信号を出力し、一方、大きいときは第2の比較信号を出力し、復元クロック信号の位相がデータ信号の位相よりも進んでいる場合には第3の比較信号を出力し、遅れている場合には第4の比較信号を出力する位相比較回路と、第3、第4の比較信号および基準クロック信号に基づいて、復元クロック信号を生成する復元クロック生成回路と、少なくとも第1、第2の比較信号に基づいて、イコライザのピーキング量を制御する制御回路と、を備える。

(もっと読む)

ディジタル信号の位相差検出方法

【課題】比較的低速かつ小規模のディジタル回路により精度の高い位相差検出を行う。

【解決手段】トラッキングサーボ回路10において、入力部のローパスフィルタ(LPF)12〜18および利得制御増幅器(GCA)20〜26はアナログ回路であり、A/D変換器28〜34より後段のオフセット・キャンセル回路36〜42、イコライザ(EQ)44〜50、位相差検出器52,54、加算器56、LPF58、利得制御増幅器(GCA)60およびサーボDSP154はすべてディジタル回路で構成される。両位相差検出器52,54は本発明の位相差検出方法にしたがって両入力信号の位相差を検出する。

(もっと読む)

クロック信号生成回路、及び半導体装置

【課題】製造プロセスにおけるばらつきが原因による同期期間や同期期間終了後の自走期間において、周波数が変動することがなく、安定した動作を実現し、また安価な半導体装置を提供する。

【解決手段】第1の基準クロック信号を生成する基準クロック信号生成回路と、第1基準クロックの信号及び同期信号を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第1のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号の立ち上がりのエッジ数を計数する第2のカウンタ回路と、第1のカウンタ回路の計数値を用いて第1の基準クロック信号を分周し、第2の基準クロック信号を生成する第1の分周回路と、第2の基準クロック信号を分周し、クロック信号を生成する第2の分周回路と、を有するクロック生成回路を半導体装置に搭載する。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

多相クロック生成回路

【課題】従来の多相クロック生成回路では、出力クロック信号に任意の周波数プロファイルを設定することができなかった。

【解決手段】本発明にかかる多相クロック生成回路1は、基準クロック信号に基づき多相クロック信号を生成する位相ロックループ回路10と、多相クロック信号の周波数プロファイルを保持し、開始信号に基づき周波数プロファイルの出力を開始し、基準クロック信号に基づき任意の周期で周波数プロファイルを更新する周波数プロファイル保持回路20と、周波数プロファイルに基づいて多相クロック信号のうち任意の位相のクロック信号を選択し、選択したクロック信号を位相ロックループ回路10に帰還させるクロック選択回路30とを有することを特徴とするものである。

(もっと読む)

遅延信号生成装置、および遅延量制御方法

【課題】短い時間で精度良くデータを記録する。

【解決手段】図1の遅延信号生成装置は、光ディスク記録装置に設けられる。検出部105は、第2遅延信号と第1遅延信号の遅延量の差が検出用パルス信号のパルス幅となるときの第2遅延セレクト信号を求め、その第2遅延セレクト信号に対応する出力位置と第1遅延セレクト信号に対応する出力位置との間にあるバッファの数を、検出結果として出力する。遅延量制御部106は、上記検出結果に基づいて、制御入力信号を求める。記録用ディレイライン101は、上記制御入力信号に応じた遅延量だけ記録用クロックを遅延させる。制御入力信号を求める遅延キャリブレーション動作は、記録中に行われる。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】入力されるシステムクロック信号と反転されたシステムクロック信号との交差点と、基準信号とが一致するように調整可能な回路を備えた半導体メモリ装置を提供すること。

【解決手段】このため本発明は、システムクロック信号と反転されたシステムクロック信号との交差点を基準とする第1クロック信号を生成する第1クロック入力部と、システムクロック信号と基準信号との交差点を基準とする第2クロック信号を生成する第2クロック入力部と、反転されたシステムクロック信号と基準信号との交差点を基準とする第3クロック信号を生成する第3クロック入力部と、遅延制御信号に対応して第1クロック信号を遅延させ遅延クロック信号として出力する遅延部と、遅延クロック信号と第2クロック信号との位相差又は遅延クロック信号と第3クロック信号との位相差に対応して遅延制御信号を出力するクロック遅延調整部とを備える半導体メモリ装置を提供する。

(もっと読む)

周波数比較器、周波数合成器及び関連方法

【課題】電圧に基づいて内部周波数を設定し、これを外部周波数と比較するアナログ周波数比較器と、アナログ周波数比較器の同じ原理でクロック信号を合成するアナログ周波数合成器、及び関連の方法を提供する。

【解決手段】周波数比較器は、第一信号と入力電圧に基づいて基準信号を生成する周波数検出回路と、該入力電圧に基づいて第二信号を生成する周波数発生器と、周波数検出回路と周波数発生器に結合され、基準信号と第二信号の一方に基づいて充電電流をイネーブルして電圧レベルを上げ、更に基準信号と第二信号のもう一方に基づいて放電電流をイネーブルして電圧レベルを下げる電荷ポンプ回路と、電荷ポンプ回路に結合され、該電圧レベルに基づいて第一信号と第二信号間の周波数関係を示す決定論理とを含む。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置の遅延固定クロックの出力において、デューティ比を容易に補正して出力可能な遅延固定回路を備える半導体メモリ装置を提供すること。

【解決手段】このため、本発明は、システムクロックを所定の時間遅延させ、遅延固定クロックを出力する遅延固定回路と、該遅延固定クロックのデューティ比を補正して第1クロックを出力するにあたり、前記第1クロックの第2エッジと、前記第1クロックによって生成された第2クロックの第2エッジとのタイミング差に対応して、前記遅延固定クロックのハイレベル区間とローレベル区間との比を調整するデューティ補正回路と、前記第1クロックの第1エッジと前記第2クロックの第1エッジとの位相を合わせるクロック同期回路とを備える半導体メモリ装置を提供する。

(もっと読む)

半導体集積回路

【課題】PLL(Phase Locked Loop)回路を搭載した半導体集積回路において、当該PLL回路の発振安定待ちの時間を有効利用する。

【解決手段】実動作準備期間中に、PLL回路50の帰還ループを遮断した状態で位相比較器51の参照クロック入力部Fpと帰還クロック入力部Frとの双方に基準クロック100を供給して、位相比較器51における位相差の検出不感帯が小さくなるように当該位相比較器51内のリセット信号の遅延を調整する。

(もっと読む)

位相比較信号処理回路

【課題】PLLのデジタル位相比較器の出力矩形波信号を処理し、PLLの引き込み可能な周波数幅を拡げ、同期時間を短縮する位相比較信号処理回路を提供する。

【解決手段】矩形波信号を両極性信号に変換する電圧シフタ7と出力端子22間に並列接続され、整流回路8と積分保持回路9と微分回路10とゲート回路12と電圧ホールド回路13と共通の加算回路14とからなる第1信号路、及び、整流回路15と積分保持回路16と微分回路17とゲート回路19と電圧ホールド回路20と前記加算回路14とからなる第2信号路、第1信号路及び第2信号路の積分保持回路9、16とゲート回路12、19を個別制御する制御信号発生器21を備え、第1及び第2信号路で、両極性信号の整流、整流電圧の積分保持、積分保持値の微分、微分出力の保持、保持電圧の加算を行うことにより処理信号を出力する。

(もっと読む)

信号発生器、信号発生方法、試験装置および半導体チップ

【課題】信号の位相を調整する精度を高める。

【解決手段】出力信号の位相を、指定された位相シフト量に応じて制御する信号発生器を提供する。信号発生器は、与えられる制御電圧の電圧値に応じた周波数の信号を生成し、出力信号として出力する電圧制御発振器と、出力信号を所定の分周比で分周した分周信号を生成する分周器と、分周信号と、与えられる基準信号との位相差に応じた電圧値の電圧を、制御電圧として出力する位相比較回路と、位相シフト量に応じて位相をシフトした基準信号を位相比較回路に入力する基準信号生成部と、出力信号に対して生成すべき位相シフト量から、基準信号生成部が基準信号に対して生成する位相シフト量を減じた位相シフト量に応じた電圧を、位相比較回路が出力する制御電圧に加算して、電圧制御発振器に入力させる加算電圧生成部とを備える。

(もっと読む)

CDR回路

【課題】入力データに含まれているジッタを削除した再生データを得る。

【解決手段】入力データのデータレート周波数と同じ周波数の参照クロックを入力データにより位相合わせして再生クロックを作成し、該再生クロックにより前記入力データをFIFO101に書き込む。該FIFO101からの読み出しには、前記再生クロックと同期関係にない前記参照クロック又は別のクロックを使用し、前記FIFO101から再生データを出力させる。

(もっと読む)

時間計測回路

【課題】短い時間幅の高分解能な計測と長い時間幅の低分解能な計測とを、回路規模を大幅に増大させることなく、いずれも実現させることが可能な時間計測回路を提供する。

【解決手段】駆動電圧VDDLに応じた遅延時間で信号を遅延させる遅延ユニットDUをM(Mは正整数)段直列接続してなり、起動用パルスPAの入力により起動され、各遅延ユニットDUにてパルス信号を順次遅延させながら伝送するパルス遅延回路10と、計測用パルスPBが入力されると、パルス遅延回路10内でのパルス信号の位置を検出(ラッチ)し、その検出結果を、起動用パルスPAの入力から計測用パルスPBの入力までの時間Tm内にパルス信号が通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ12と、電圧設定データDVに従った大きさの駆動電圧VDDLを発生させる駆動電圧設定回路14とを備える。

(もっと読む)

81 - 100 / 138

[ Back to top ]