Fターム[5J043DD07]の内容

Fターム[5J043DD07]に分類される特許

1 - 20 / 62

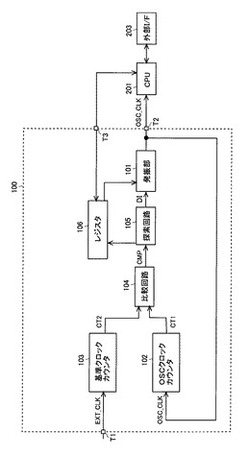

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

発振回路

【課題】共振部とインバータを並列接続する発振回路では、インバータのトランスコンダクタンスが発振周波数に拘わらず一定なので、スプリアスへの収束を回避することが難しい。本発明はスプリアスへの収束を回避できる発振回路を提供することを目的にする。

【解決手段】インバータの入力信号の遷移点(立ち上がり、立ち下がり)で一定幅のパルス信号を出力するワンショット回路を用い、このワンショット回路のパルス幅がインバータへの入力信号のパルス幅より大きいときに、インバータへの電源供給を停止するようにした。スプリアスではトランスコンダクタンスの時間平均が小さくなり、発振が持続しない。

(もっと読む)

パルス発生回路、集積回路装置、検出装置

【課題】 パルス幅を容易かつ正確に調整可能であって、システムクロックとは非同期にパルス信号を生成することが可能なパルス発生回路を提供する。

【解決手段】 所定の電流値の電流を生成する定電流源32と、前記定電流源32からの電流によって電荷が充電されるキャパシター36と、前記キャパシター36に充電された電荷に基づく電圧130と、所定の電圧値VRを有するリファレンス電圧42とを比較した結果に基づいて、パルス信号を出力するコンパレーター40と、を含むパルス発生回路。前記コンパレーターの出力端子を、高電位側の電源電位にプルアップするプルアップ用トランジスター44を含む。

(もっと読む)

電子回路

【課題】発振回路部の信号反転素子及びインターフェース回路部のインターフェース回路部のインターフェース集積回路素子で消費される電流を抑えて消費電力が少ない電子回路を提供する。

【解決手段】発振回路部とインターフェース回路部と被駆動回路部と備えた電子回路であって、発振回路部用電源電圧印加端子と発振回路部の間に発振回路部用電流制限抵抗が設けられ、インターフェース回路部用電源電圧印加端子とインターフェース回路部との間にインターフェース回路部用電流制限抵抗が設けられ、発振回路部用電流制限抵抗の両端部からグランドに接続されている第一のコンデンサが設けられ、インターフェース回路部用電流制限抵抗の両端部からグランドに接続されている第二のコンデンサが設けられ、インターフェース回路部から出力され被駆動回路部に入力される信号電圧が被駆動回路部が動作するために必要な電圧より大きいことを特徴とする。

(もっと読む)

発振回路

【課題】簡単な構成で発振周波数が低いときの消費電力を低減する発振回路を提供することを目的とする。

【解決手段】周波数選択信号に応じて発振周波数を切り替えてメインクロックを出力するクロック発振器23と、前記周波数選択信号に応じて分周比を切り替え、前記メインクロックを分周したサブクロックを出力する分周回路24とを有し、前記発振周波数が高いときと低いときとで前記サブクロックの周波数を一定とした。好ましくは、前記サブクロックに同期して前記周波数選択信号を変化させる同期部22を有する。

(もっと読む)

可変抵抗回路および発振回路

【課題】回路規模を比較的小さくすることができ且つ高精度な抵抗値調整が可能な可変抵抗回路を提供し、また、かかる可変抵抗回路を用いた比較的回路規模が小さく高精度な発振周波数を実現し得る発振回路を提供する。

【解決手段】

可変抵抗回路は、複数の抵抗素子からなる第1の直列抵抗回路と、制御信号に応じて第1の直列抵抗回路の所定のノードのうちの1つを選択的に第1の端子に接続せしめる第1のスイッチ部と、を有する第1の抵抗調整回路と、第2の端子に接続された複数の抵抗素子からなる第2の直列抵抗回路と、制御信号に応じて第1の直列抵抗回路を第2の直列抵抗回路の所定ノードのうちの1つに選択的に接続せしめる第2のスイッチ部と、を有する第2の抵抗調整回路と、を含む。

(もっと読む)

パルス幅に応じて動作するシュミットトリガー回路

【課題】入力されるパルスの幅を基準としてリリースポイント及びオペレーティングポイントが決定されるヒステリシス特性を有するシュミットトリガー回路を提供する。

【解決手段】前記シュミットトリガー回路は、アナログ信号の入力を受けて前記アナログ信号の大きさに相応する幅を有する入力パルスを生成する信号/パルス切り替え部と、前記信号/パルス切り替え部で生成された入力パルスの幅を予め設定された第1の臨界幅及び前記第1の臨界幅より大きい第2の臨界幅と比較し、その結果を表す状態情報を出力するパルス幅判断部と、前記状態情報によって、前記入力パルスの幅が前記第2の臨界幅より小さい状態から大きい状態に変動される場合、ハイ信号を出力し、前記入力パルスの幅が第1の臨界幅より大きい状態から小さい状態に変動される場合、ロー信号を出力する出力決定部と、を含むことができる。

(もっと読む)

信号多重化方法および信号多重化回路

【課題】 複雑なディジタル処理回路を必要とすることなく、複数のディジタル的状態信号と、アナログ信号とを多重化して1本の伝送線により送信可能な信号多重化方法および信号多重化回路を提供すること。

【解決手段】 複数のディジタル的状態信号とアナログ信号とを多重化する信号多重化方法であって、前記ディジタル的状態信号は、発振回路11で生成されるパルスの周波数および/またはデューティー比を異ならせることで前記パルスに含ませ、前記アナログ信号は、前記パルスの高さ信号として前記パルスに含ませることを特徴とする。

(もっと読む)

発振回路

【課題】発振周波数の精度を改善することが可能な発振回路を提供すること。

【解決手段】PTAT出力とCTAT出力とを加算して出力する基準電圧発生回路と、加算割合を切り替え温度に依存した基準電圧発生回路の出力の変動を最小化する第1切替手段と、基準電圧発生回路の出力に基づいて定電流を発生させる電流源と、基準電圧発生回路の出力に基づいて定電圧を発生させるレギュレータ回路と、一端が電流源に接続され電流源の定電流によって充放電される第1容量及び第2容量と、レギュレータ回路から供給される定電圧を電源として第2容量の他端を駆動するインバータと、電流源の定電流の値を切り替え発振周波数を調整する第2切替手段と、第1容量の容量値を切り替え第1容量及び第2容量の一端における発振振幅を調整する第3切替手段と、を備え、第1切替手段、第2切替手段、第3切替手段のトリミングによって所望の大きさの一定周波数を生成する。

(もっと読む)

水晶発振器

【課題】水晶発振器の出力振幅の調整機能を簡易な構成で実現する。

【解決手段】水晶発振器は、電源に接続される電源端子(VCC)と、接地電位に維持される接地端子(GND)と、電源端子と接地端子とに接続され、電源端子と接地端子との間に印加された電源電圧に基づく振幅レベルの発振信号(V0)を出力する水晶発振回路(6)と、イネーブル信号(VEN1、VEN2)が入力されるイネーブル端子(EN1、EN2)と、イネーブル端子と接地端子とに接続され、水晶発振回路から入力される発振信号を波形整形してイネーブル端子と接地端子との間のイネーブル信号の電圧に応じた振幅レベルの基準クロック信号(CLK1、CLK2)を出力するバッファ回路(2a、2b)と、バッファ回路から出力される基準クロック信号が出力される出力端子(OUT1、OUT2)と、を備える。

(もっと読む)

電源回路

【課題】どの条件下でも一定のパルス幅で駆動する電源回路を提供する

【解決手段】電源回路10は、外部回路20と接続可能である。電源回路10は、一定の内部電圧を外部回路20に印加するフィードバック回路12と、パルスのパルス幅に応じた電荷を外部回路20に供給する電荷供給回路14と、外部回路20のオペレーションに対応するオペレーション状態に依存しない一定のパルスを電荷供給回路14に供給する電源制御回路16と、備える。

(もっと読む)

極低電圧発振回路及びそれを用いた極低電圧DCDC変換装置

【課題】太陽電池や燃料電池は単一セルでは出力電圧が0.2Vから0.6Vと非常に低くその電圧を昇圧してエネルギーを2次電池に蓄積する場合、昇圧回路が0.2V程度からの極低電圧領域から昇圧動作を開始する必要がある。

【解決手段】FETのサブスレシュオールド領域を利用して極低電圧から発振を開始するとともに周囲温度の変化に対しても安定な周波数を発生する補正機構を組み込むことにより確実に起動しかつ正確にDCDC変換装置を実現する。

(もっと読む)

ダブルエッジトリガフリップフロップを有する回路用の一体型クロックゲーティングセル

ダブルエッジトリガ回路は、クロック信号及びイネーブル信号に応答してゲーテッドクロック信号を出力するクロックゲータと、ゲーテッドクロック信号に応答してデータ信号を送り出す第1のダブルエッジトリガフリップフロップと、クロック信号に応答してデータ信号を捕捉する第2のダブルエッジトリガフリップフロップとを含み、クロックゲータは、イネーブル信号が第1の論理状態のときに第1の論理値にてゲーテッドクロック信号を停止し、イネーブル信号が第2の論理状態のときに次のクロックエッジにてゲーテッドクロック信号を第1の論理値からスイッチングする。 (もっと読む)

伝送装置及び伝送信号のジッター抑圧方法

【課題】伝送装置の出力信号のジッターを抑制することを目的とする。

【解決手段】伝送装置は入力信号が入力しているか否かを検出する入力信号断検出部と、発振器と、前記入力信号断検出部により入力信号が入力していることが検出されたときには、前記発振器の発振周波数と、入力信号から抽出されるクロック信号を分周した分周信号の周波数との差の周波数がフィルタの通過帯域外となるように前記発振器の発振周波数を設定する周波数設定部とを備える。

(もっと読む)

パルス生成回路およびパルス生成方法

【課題】電源電圧の変動しやすい容量の小さい電源である環境下でも、安定したパルス信号を生成できるようにする。

【解決手段】タイミング制御回路1−1,1−2と論理回路2−1とを設ける。タイミング制御回路1−1,1−2は、放電制御端子S11,S21と充電制御端子S12,S22,と信号出力端子T1,T2を有し、内部に時定数素子を備えている。先ず、充電制御端子S12,S22へ充電の開始を指示し、端子T1,T2から出力される電圧VT1,VT2を「H」レベルとする。次に、放電制御端子S11へ放電の開始を指示し、遅延時間τ1経過後に電圧VT1を「L」レベルとし、タイミング制御回路1−2での放電を開始させ、遅延時間τ2経過後に電圧VT2を「L」レベルとする。このタイミング制御回路1−1,1−2からの電圧VT1,VT2を論理回路2−1へ与え、論理回路2−1よりタイミング制御回路1−2での遅延時間τ2をパルス幅とするパルス信号PS1を得る。

(もっと読む)

デジタル制御発振器

【課題】TDCに関する冗長構成を削減可能なDCOを提供する。

【解決手段】DCOは、デジタル制御信号によって遅延量が制御される3以上の奇数個の単相インバータ101〜105を環状に接続したリングオシレータと、単相インバータの各々の出力信号をバッファリングし、第1の差動信号として夫々出力する奇数個のバッファ111〜115と、基準信号の立ち上がりエッジまたは立ち下がりエッジにおける第1の差動信号の値を保持して第2の差動信号として夫々出力する奇数個のフリップフロップ121〜125と、奇数個のフリップフロップから出力される奇数組の第2の差動信号を入力し、奇数組の第2の差動信号を位相の進み順に配列したときの、連続する高レベル値または連続する低レベル値の末尾を示す情報を出力するエッジ検出器130とを具備する。

(もっと読む)

予め定められたデューティサイクル信号発生器

予め定められたデューティサイクルを有する信号を発生させる技術である。例示的な実施形態では、第1のカウンタは、発振器信号のサイクルの第1の数をカウントするように構成されており、第2のカウンタは、発振器信号のサイクルの第2の数をカウントするように構成されており、第2の数は第1の数よりも大きい。第2のカウンタの出力は、第1および第2のカウンタをリセットするために使用されるが、第1および第2のカウンタの出力は、さらに、予め定められたデューティサイクルを有する信号を発生させるトグルラッチを駆動する。さらなる態様は、第2の数に対する奇数値と偶数値とを対応する技術を含む。 (もっと読む)

電圧−周波数変換回路およびそれを備えた血圧測定装置

【課題】簡易な方式により精度の高い電圧−周波数変換回路を提供する。

【解決手段】抵抗素子16は、入力端子とノードN0との間に設けられる。スイッチ素子15は、ノードN0と接地電圧GNDとの間に設けられ、ノードNCの電圧レベルに応じて導通する。抵抗素子13は、ノードN0とノードNAとの間に設けられる。抵抗素子12は、ノードNAとNOR回路11Aの入力ノードの一方側との間に設けられる。コンデンサ14は、ノードNAとノードNCとの間に接続される。NOR回路11Aの入力ノードは、抵抗素子12を介してノードNAと、接地電圧GNDと接続される。NOR回路11Bの入力ノードは、NOR回路11Aの出力ノードと、接地電圧GNDと接続される。NOR回路11Cの入力ノードは、ノードNCと、接地電圧GNDと接続される。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を提供する。

【解決手段】パルス発生装置100を、起動開始信号D0の入力に応じて単位パルス信号を発生する、各々の信号出力部が独立した単位パルス発生回路20_1〜20_Nと、単位パルス発生回路20_1〜20_Nのうち単位パルス信号を出力する予定の一部の回路の信号出力端子を順次選択して、該選択した信号出力端子を共通の信号出力線Pu_Coutに電気的に接続し、残りの単位パルス発生回路の信号出力端子を共通の信号出力線Pu_Coutから電気的に切断するスイッチ制御回路30及び選択スイッチ40とを含む構成とした。

(もっと読む)

パルス発生回路およびパルス幅変調器、遅延回路ならびにそれらを利用したスイッチング電源の制御回路

【課題】消費電力を低減する。

【解決手段】パルス発生部42は、所定の周波数のクロックCLKを受け、そのポジティブエッジと同期して遷移するパルス信号PWM1を発生する。インバータ44は、クロックCLKを反転する。フリップフロップ46は、インバータ44からの反転クロックCLK#のポジティブエッジのタイミングで、パルス信号PWM1を取り込む。論理ゲート48は、パルス信号PWM1とフリップフロップ46の出力PWM2を多重化する。セレクタ50は、論理ゲート48の出力と、パルス信号PWM1のいずれかを選択する。

(もっと読む)

1 - 20 / 62

[ Back to top ]