Fターム[5J081CC06]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 特性の改善 (481) | 周波数特性の改善 (302) | 周波数の安定化 (99)

Fターム[5J081CC06]に分類される特許

21 - 40 / 99

高周波二倍波発振器

【課題】本発明は、位相雑音の劣化原因によらず位相雑音を低減できる高周波二倍波発振器を提供することを目的とする。

【解決手段】トランジスタと、該トランジスタのベース側に接続された第一電気信号線路と、該第一電気信号線路に接続され他の端は接地された第一シャントキャパシタと、該トランジスタのコレクタ側に接続された第二電気信号線路と、該第二電気信号線路に接続され他の端は接地された第二シャントキャパシタと、該第一電気信号線路と該第二電気信号線路を接続する大容量キャパシタとを備える。該第一電気信号線路の線路長は、基本波信号の波長の1/4の値を奇数倍した長さから基本波信号の波長の1/16の長さを減算した長さと、基本波信号の波長の1/4の値を奇数倍した長さに基本波信号の波長の1/16の長さを加算した長さとの間の値である。

(もっと読む)

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

発振装置

【課題】発振周波数の変動を防止することができる発振装置を提供する。

【解決手段】トランジスタのゲート電圧に応じて入力端子の信号を出力端子から出力するトランスファゲートPM5,NM5と、トランスファゲートの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第1のインバータIV1と、第1のインバータの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第2のインバータPM6,NM6と、第1のインバータの出力信号の論理反転信号を入力し、入力した信号の論理反転信号をトランスファゲートの入力端子に出力する第3のインバータPM4,NM4と、トランスファゲートの出力端子及び第2のインバータの出力端子間に接続される第1の容量C1と、トランスファゲートの出力端子及び基準電位ノード間に接続される第2の容量C2とを有する発振装置。

(もっと読む)

高周波帯電圧制御発振器

【課題】共振回路における発振周波数の公差を低減し、PLL回路に用いられる論理回路の低電圧化傾向の下でも、発振周波数の高周波化を図る。

【解決手段】発振周波数を可変制御するLC同調型の電圧制御発振器において、発振用トランジスタ1のエミッタ側で、接地電位となる一対のスルーホールH1 ,H2 の間に、同一線路長のマイクロストリップ線路からなる2つのショートスタブP1 ,P2 を形成し、これらショートスタブP1 とP2 との間に上記トランジスタ1のエミッタを接続する。即ち、ショートスタブP1 とP2 は、エミッタ接続点を中心に対称となる位置で並列に接続される。また、コンデンサC1 ,C2 でDCカットされたバラクタCvのカソードに、0〜5Vの制御用電圧Vtを印加すると共に、アノードに、基準電圧源6から例えば−5Vの基準電圧を印加する。

(もっと読む)

インダクタを備えた半導体集積回路

【課題】半導体集積回路をパッケージに実装した後に、インダクタンスを増加および減少させる調整が可能な半導体集積回路を提供する。

【解決手段】LSIの内部回路106が形成された同一の半導体基板に磁気検出素子100が形成されており、ボンディングパッド114とLSIの内部回路106の間に接続された第1インダクタ101のインダクタンスを磁気検出素子100と磁気検出回路105の出力電圧でモニタし、第1インダクタ101の片方の端子と第2インダクタ102の一端と第3インダクタ103の一端が第1接続部107を介して接続される第1スイッチ108、第2インダクタ102の片方の端子が第2接続部109を介して接続される第2スイッチ110、および、第3インダクタ103の片方の端子が第3接続部111を介して接続される第3スイッチ112を接続または切断状態に切り替えることにより、第一のインダクタ101をトリミングする。

(もっと読む)

半導体回路

【課題】安定した動作を行うことができる半導体回路を提供することを課題とする。

【解決手段】ソースが第1の電位ノードに接続される第1のpチャネルトランジスタ(201)と、ソースが第2の電位ノードに接続される第1のnチャネルトランジスタ(202)と、ゲートが第1のnチャネルトランジスタのドレインに接続され、ドレインが第1のnチャネルトランジスタのゲートに接続される第2のpチャネルトランジスタ(203)と、ゲートが第1のpチャネルトランジスタのドレインに接続され、ドレインが第1のpチャネルトランジスタのゲートに接続される第2のnチャネルトランジスタ(204)と、第1のpチャネルトランジスタ及び第1のnチャネルトランジスタのドレイン間に接続される第1の抵抗(301,302)と、第2のpチャネルトランジスタ及び第2のnチャネルトランジスタのドレイン間に接続される第2の抵抗(303,304)とを有する。

(もっと読む)

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

発振回路

【課題】高周波発振であっても安定した発振を行なえる。

【解決手段】発振回路1は、圧電振動子を所定の周波数で励振させる発振回路部を備え、発振回路部の等価回路ECは、負性抵抗RLと容量性リアクタンスCLが直接接続された直列モデルで構成されている。発振回路部の一方の端子ECAにコイルLSの一方の端子が直列接続され、発振回路部の他方の端子ECBとコイルLSの他方の端子との間に抵抗RPが並列接続されている。コイルLSの他方の端子と抵抗RPの一方の端子との接続点が、圧電振動子との接続を行う一方の圧電振動子接続用端子Aとされ、抵抗RPの他方の端子と発振回路部の他方の端子ECBとの接続点が、圧電振動子との接続を行う他方の圧電振動子接続用端子Bとされている。また、抵抗RPの絶対値は、負性抵抗RLの絶対値よりも大きい。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

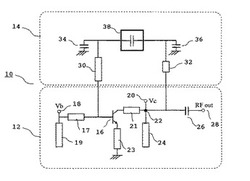

発振器

【課題】負荷容量に応じて最適な波形を出力可能な発振器を提供する。

【解決手段】発振回路12からの出力を、出力バッファ(前段出力バッファ14、出力バッファ22)を介して負荷回路に出力する発振器10であって、発振器10は、出力バッファ22の駆動能力を出力バッファから流れる電流に応じて調整可能なバッファ制御回路48を有する。ここで出力バッファ22は、発振回路12の後段に複数並列に接続されるとともに、バッファ制御回路48は、出力バッファから流れる電流に応じて出力バッファ22の稼動数を調整する信号を出力バッファ22に出力することにより出力バッファ22の駆動能力を調整している。

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

マイクロ波発振素子及びマイクロ波発振装置

【課題】マイクロ波発振素子及びマイクロ波発振装置に関し、複雑な成膜工程や微細加工の必要がない簡単な素子構造によりマイクロ波発振を可能にする。

【解決手段】強磁性体層11とスピン軌道相互作用を有する金属層12との積層構造からなり、金属層両端の端子131、132との間に電源14から電圧を印加して、金属層12に電流を流す事で、スピンホール効果により金属層12から強磁性体層11へ純スピン流が注入され、マイクロ波発振を励起する。

(もっと読む)

変圧器をベースとしたCMOS発振器

【解決手段】低電圧源で動作可能な変圧器に基づいたCMOS発振器を提供するための技術である。LCタンクは、トランジスタペアのドレインに設けられ、LCタンクのインダクタンスは、トランジスタペアのゲート間のインダクタンスに相互磁気結合される。分離相補型トランジスタペアはLCタンクにも結合される。典型的な実施形態によって、タンク間の3方向結合、トランジスタペアのゲート間のインダクタンス、及び相補型トランジスタペアのゲート間のインダクタンスだけでなくトランジスタペアのゲートにLCタンクが更に供給される。 (もっと読む)

基準周波数制御回路

【課題】 基準周波数を生成する発振回路の発振周波数の変化を抑制可能な基準周波数制御回路を提供する。

【解決手段】 入力信号のレベルに応じた周波数で発振する発振回路からの発振信号が入力され、前記発振信号の周波数に応じた出力電圧を出力する周波数電圧変換回路と、前記出力電圧が所定レベルとなるよう前記入力信号のレベルを制御する制御回路と、を備えることを特徴とする基準周波数制御回路。

(もっと読む)

電圧制御発振回路およびクロック信号生成回路

【課題】制御電圧に対する可変容量の容量値の変化の線形性を向上して位相ノイズを低減した電圧制御発振回路の実現。

【解決手段】制御電圧に応じて発振周波数が変化する発振信号OUT,OUTXを出力する電圧制御発振回路において、印加電圧に応じて容量値が変化する複数の可変容量VAC1-VAC4と、制御電圧を分圧して複数の可変容量に印加する分圧電圧VT,VT1-VT3を生成する分圧電圧生成部R1-R4と、を備える。

(もっと読む)

PLL回路、及び無線機

【課題】 位相誤差の小さい、発振信号の精度が高いPLL回路及び無線機を提供する。

【解決手段】 第一差動信号を生成する第一発振部と、前記第一差動信号を90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とするPLL回路。

(もっと読む)

発振器

【課題】周波数を高くしても分布定数線路の線路長を長くできてQ値を向上できるとともに、製造誤差を小さく抑えることができる発振器を提供する。

【解決手段】1波長の線路長であって、両端をグランドに接地した分布定数線路16を有し、この分布定数線路16の一端から1/4波長の位置に設けた第1の中間タップに発振トランジスタ27のべースを接続するようにした。これにより、分布定数線路16の線路長が従来の1/4波長の線路長の分布定数線路より長くなり、その分Q値の向上が図れるとともに、製造誤差を小さく抑えることが可能となる。分布定数線路16の長さを1/2波長としても従来の1/4波長の長さの分布定数線路に比べて2倍長くできる。このようにしてもQ値の向上が図れ、また製造誤差を小さく抑えることが可能となる。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

高周波発振器

【課題】周囲の環境温度による光ファイバの熱伸縮に対してもPLL制御を正常に行うことができる高周波発振器を得る。

【解決手段】レーザ光源が発生したレーザ光を光変調器により変調し、光ファイバを介して伝送した変調後のレーザ光を光電変換器により高周波信号に変換し、変換後の高周波信号からバンドパスフィルタにより所定の通過帯域成分を取り出し、当該所定の通過帯域成分の高周波信号の周波数を変調信号として前記光変調器に帰還すると共に発振信号として出力する高周波発振器において、高周波信号の周波数が一定になるように制御するPLL制御手段と、当該高周波発振器の発振周波数の変動をPLL制御手段の予め設定した周波数引き込み範囲内に納めるように高周波信号の位相を調整する位相調整手段を備えた。

(もっと読む)

21 - 40 / 99

[ Back to top ]