Fターム[5J081FF18]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路素子 (660) | 半導体 (256) | トランジスタ (180) | FET (124)

Fターム[5J081FF18]に分類される特許

21 - 40 / 124

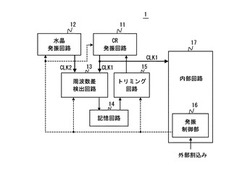

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

周波数逓倍器装置及びその操作方法

【課題】本発明は、従来の周波数逓倍器による悪い高調波抑圧比を改善し、又、周波数逓倍器からの発振周波数は、他の高調波に妨害されにくいため、周波数逓倍器装置及びその操作方法を提供することを目的とする。

【解決手段】本発明の周波数逓倍器装置は、高調波発生器、高調波抑制器及び特定高調波応用装置を含んでいる。前記高調波発生器は、基本周波数を有する入力信号を受信して、第一高調波信号成分及び第二高調波信号成分を含む高調波信号を発生させる。前記高調波抑制器は、前記高調波信号を受信して、前記第一高調波信号成分を抑制し、前記第二高調波信号成分を高める。前記周波数逓倍器装置は、高められた前記第二高調波信号成分を受信する。

(もっと読む)

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

発振装置

【課題】発振周波数の変動を防止することができる発振装置を提供する。

【解決手段】トランジスタのゲート電圧に応じて入力端子の信号を出力端子から出力するトランスファゲートPM5,NM5と、トランスファゲートの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第1のインバータIV1と、第1のインバータの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第2のインバータPM6,NM6と、第1のインバータの出力信号の論理反転信号を入力し、入力した信号の論理反転信号をトランスファゲートの入力端子に出力する第3のインバータPM4,NM4と、トランスファゲートの出力端子及び第2のインバータの出力端子間に接続される第1の容量C1と、トランスファゲートの出力端子及び基準電位ノード間に接続される第2の容量C2とを有する発振装置。

(もっと読む)

発振回路及び半導体装置

【課題】周波数可変範囲の広い発振回路及び発振回路を備えた半導体装置を提供する。

【解決手段】第1の端子と第2の端子との間に接続されたインダクタンス素子と、インダクタンス素子と並列に第1の端子と第2の端子との間に接続された増幅回路と、第1の端子及び第2の端子に接続された第1の容量素子と、を備えた共振型発振回路であって、インダクタンス素子の配線の途中に2箇所以上の引き出し部を設け、2箇所以上設けた引き出し部の間にオンしたときに当該引き出し部間を短絡するスイッチ素子と第2の容量素子とが並列に接続されている。

(もっと読む)

MOSFETのソースバルク電圧を用いた信号処理ASIC用の温度補償RC発振器

温度補償CMOS RC発振回路は、抵抗と温度相関バイアス電流とを用いてソースバルク電圧を変化させて、温度に対するMOSFETの閾値電圧の変動を安定させる。この温度層間バイアス電流はまた、抵抗を流れる。温度が上昇すると、バイアス電流も増え、MOSFETのソースバルク電圧を上昇させる。上昇したソースバルク電圧は、高い温度にてMOSFETの閾値電圧を安定させるのを補助する。この発振器には省電力ロジックも組み込まれており、低い電力消費で高い周波数が得られる。本発明では、得られる発振器が低出力設計となってしまう高利得オペアンプや高速比較器はなく、他のシステムとともにシングルチップに組み込むことができる。 (もっと読む)

切り替え可能インダクタネットワーク

制御信号に応じて設定可能インダクタンスを有する切換可能インダクタネットワークを提供するための技術。前記切り替え可能インダクタネットワークは、差動モード動作の寄生素子の影響を低減するために完全に対称的なアーキテクチャを採用することができる。前記切り替え可能インダクタネットワークは、特に、マルチモード通信回路への用途、例えば、電圧制御発振器(VCO)またはそのような回路におけるアンプもしくはバッファに適している。 (もっと読む)

温度安定化された電圧制御発振器

【課題】温度安定化された電圧制御発振器を提供する。

【解決手段】セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a、310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370、380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b、320a、320bを含んでいる。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

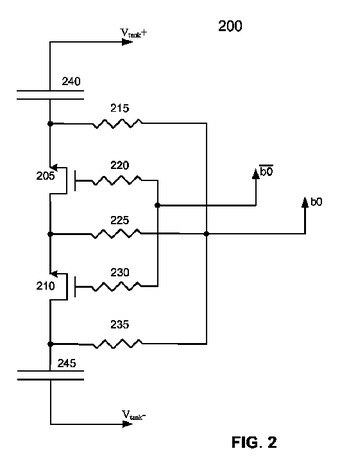

キャパシタスイッチング回路

キャパシタンススイッチング素子(200)が、トランジスタ(205、210)によって直列に接続された、第1のキャパシタ(240)と第2のキャパシタ(245)とを含む。トランジスタのゲートは、一組の抵抗器(220、230)を介して第1の信号(b0/)によってバイアスをかけられ、ソースおよびドレインは、第2の組の抵抗器(215、225、235)を介して第2の信号(b0)によってバイアスをかけられる。信号はレベルシフトされており、相補的であってよい。素子をオンにするためには、第1の信号(b0/)をVDDに設定することができ、第2の信号(b0)をゼロに設定することができる。素子をオフにするためには、第1の信号(b0/)をVDD/2の倍数に設定することができ、第2の信号(b0)をVDD/2の倍数プラス1(the multiple plus one)に設定することができる。素子が発振器同調回路で使用されるとき、トランジスタの圧力ストレスが低減され、トランジスタを薄酸化物で製作することができる。発振器は、セルラアクセス端末のトランシーバにおいて使用されてもよい。  (もっと読む)

(もっと読む)

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

発振回路及び、その発振回路を用いた無線機

【課題】 信号振幅が大きい高調波信号を提供することができる発振器を提供する。

【解決手段】 一導電型又は逆導電型の第1のMOSトランジスタ20と、第1のMOSトランジスタ20のドレイン端子に接続された負荷素子30と、第1のMOSトランジスタ20のソース端子に接続され、高調波信号を出力する基本発振器40とを備え、第1のMOSトランジスタ20のドレイン端子から、基本発振器40から出力される高調波信号の増幅信号を出力することを特徴とする発振回路。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、Y−Y’上の点Bを通るY−Y’に関して線対称なインダクタ部Ind1及びInd2を備える。インダクタ部Ind2は、点B以外でインダクタ部Ind1と交わらず、インダクタ部Ind1及びInd2は共に曲線のみで構成される。インダクタ部Ind1の線路長はInd2の線路長よりも短い。Ind1は、Y−Y’上の点Z1を中心点とした円周上の円弧で構成され、端子D’から点Bを通って端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、Y−Y’上の点Z2を中心点とした円周上の円弧で構成され端子E’から点Bを通って端子E’とY−Y’に関して線対称な端子E’’まで延在する。

(もっと読む)

発振回路

【課題】製造バラツキ等による、S/N比の劣化が発生すると、出力信号の品質が劣化する可能性がある

【解決手段】本発明は、振幅制御値に応じて動作状態となる個数が変化する複数の第1電流源と、前記複数の第1電流源から出力されるバイアス電流値の合計値に応じて振幅が制御される出力信号を生成する信号生成回路と、振幅設定値に応じて動作状態となる個数が変化する複数の第2電流源と、前記複数の第2電流源から出力される振幅設定電流の合計値と前記出力信号の振幅に応じて生成される振幅検出電流との差に基づき振幅検出信号を出力する振幅検出回路と、前記振幅検出信号に基づき前記振幅制御値を変更する制御回路と、を有する発振回路である。

(もっと読む)

半導体発振回路および携帯電話

【課題】基準周波数生成回路は、ロジック回路の電源ノイズの影響を受けて、周波数偏差やピリオドジッターの悪化を引き起こしていた。

【解決手段】CPUや周辺回路などのロジック回路12の電源はレギュレータ13より供給し、基準周波数生成回路11の電源には電源の高周波ノイズを10dB以上の減衰量を持つローパスフィルター10を介してから供給する。これによりロジック回路12で発生する高周波ノイズ起因での周波数偏差やジッターの悪化を抑えることができ、この基準周波数をUARTシリアル回路に接続して通信ができる。

(もっと読む)

オーム調節可能な発振周波数を有する発振器

調節可能な発振周波数を有する発振器は、端子で負性入力抵抗を示している能動素子、負性入力抵抗を示しているその能動素子の端子と連結した発振回路、および、その発振器の発振周波数が調節可能である調節可能なオーム抵抗を有する素子を含む。 (もっと読む)

バッファ回路

【課題】可変容量ダイオードの最小サイズに制限を有する半導体集積化プロセスによる複数のバッファ回路を用いたVCOにおいて、制御電圧の変化に対する発振周波数の変化を必要に応じて小さくできるようにしたバッファ回路を提供すること。

【解決手段】カスコード接続されたトランジスタQ1〜Q4とL1、L2 インダクタL1、L2により形成されているバッファ回路において、時定数回路素子を構成する可変容量ダイオードD1、D2をトランジスタQ3、Q4のソース端子側に接続したもの。基本動作上でトランジスタQ3、Q4のソース端子の電圧変動が小さくなるので、電圧制御端子Vcont1に印加する電圧を変化させたときの可変容量ダイオードD1、D2による静電容量の変化が小さくなる。制御電圧の変化に対して静電容量の変化が小さくなれば、VCOに適用したときに制御電圧の変化に対する発振周波数の変化が抑制され、安定度が向上する。

(もっと読む)

電圧制御発振回路およびクロック信号生成回路

【課題】制御電圧に対する可変容量の容量値の変化の線形性を向上して位相ノイズを低減した電圧制御発振回路の実現。

【解決手段】制御電圧に応じて発振周波数が変化する発振信号OUT,OUTXを出力する電圧制御発振回路において、印加電圧に応じて容量値が変化する複数の可変容量VAC1-VAC4と、制御電圧を分圧して複数の可変容量に印加する分圧電圧VT,VT1-VT3を生成する分圧電圧生成部R1-R4と、を備える。

(もっと読む)

21 - 40 / 124

[ Back to top ]