Fターム[5J106EE08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−付属構成 (846) | 検出回路 (618) | 誤動作検出 (274) | 同期・非同期検出 (247)

Fターム[5J106EE08]の下位に属するFターム

Fターム[5J106EE08]に分類される特許

1 - 20 / 112

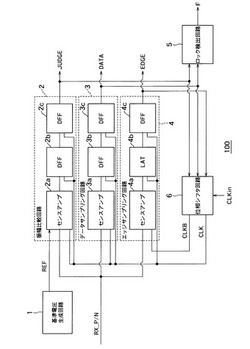

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

誤ロック防止回路、防止方法及びそれを利用した遅延ロックループ

【課題】遅延ロックループにおいて誤ロックが生じた場合、そこから抜け出すために使用される誤ロック防止回路、防止方法及びそれを利用した遅延ロックループを提供する。

【解決手段】誤ロック防止回路はハーモニックロックを検出する検出器とスタックロックを検出する検出器とで構成される。ハーモニックロック検出器は前記遅延クロックを本発明の特徴的な方法でサンプリングする複数個のフリップフロップ及び論理部で構成される。ハーモニックロック検出器では基準クロックと基準クロックから遅延された複数個の遅延クロックの立ち上がりエッジを比較してこれらの立ち上がりエッジが基準クロックの1周期から離れた場合を検出する。スタックロック検出器は位相検出器の出力信号と前記遅延クロックのうち1つを利用した論理回路であり、論理演算の結果で位相検出器をリセットさせる。

(もっと読む)

PLL回路

【課題】 電源投入時及び基準周波数信号断から基準周波数信号入力有りの時からロックまでの時間を短くでき、ロック時の発振を安定化させ、更にロック状態から基準周波数信号断となった時にロックから制御電圧の中心付近まで早く落ち着かせることができるPLL回路を提供する。

【解決手段】 電源投入時とREF断状態からREF有りとなった場合に、積分器15内のオペアンプ39の利得を大きくし、増幅器16内のオペアンプ37の利得を大きくすることで、ロックまでの時間を短くでき、ロック時に増幅器16内のオペアンプ37の利得を小さくし、ロック状態でREF断となった場合に、積分器15内のオペアンプ39の利得を小さくしているので、自走時にコンデンサ28の電荷の放電を早めて、自走周波数に移行する時間を短くして安定化を早めることができるPLL回路である。

(もっと読む)

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

PLL回路

【課題】PLL回路の引き込時間を短縮する。

【解決手段】位相比較器10は、PLL回路100への入力クロックの位相と、PLL回路100の出力から分周器40を介して帰還される帰還クロックの位相とを比較し、その位相差に応じた信号を生成する。LPF20は、位相比較器10の出力信号に応じた直流電圧を生成する。電圧制御発振器30は、LPF20により生成された電圧に応じた周波数のクロックを出力する。サイクルスリップ予測回路50は、位相比較器10により生成される信号を監視し、サイクルスリップの発生を予測する。サイクルスリップ予測回路50によりサイクルスリップの発生が予測されたとき、入力クロックの位相、帰還クロックの位相および電圧制御発振器に入力される電圧のいずれかが調整される。

(もっと読む)

PLL回路

【課題】 基準周波数断時におけるフリーランの出力周波数の精度を向上させるPLL回路を提供する。

【解決手段】 比例積分方式のPLL回路を用いて、積分器14の後にA/D変換部15とパタン生成部16を付加した構成とし、A/D変換部15が、ロック時の積分器14の出力電圧をデジタル信号として得て、ロック外れ時はロック時のデジタル信号を保持する機能を備え、ロック外れ時で基準周波数断時には、保持したデジタル信号に応じてパタン生成部16がパタン生成し、セレクタ13によって積分器14に出力するものであり、基準周波数断時には、パタン生成の波形を積分器14に代替入力するPLL回路である。

(もっと読む)

位相同期発振器および送信機

【課題】従来に比べて正確にロック状態およびアンロック状態を判定することができる位相同期発振器を提供する。

【解決手段】位相同期発振器はサンプリング位相検波器SPDを備える。サンプリング位相検波器は、基準信号と、電圧制御発振器VCOから出力される発振信号の位相差に応じた電圧信号を出力する。シュミット回路34は、サンプリング位相検波器の出力に応じてパルス信号を生成する。判定回路は、パルス信号の有無に応じてロック/アンロックを判定する。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

同期信号生成装置および同期信号生成方法

【課題】ホールドオーバー状態からGPSロック状態に復帰する際の基地局の状態に応じて、内部パルスおよび内部周波数信号をGPS基準パルスに同期させた状態に復帰させることができる同期信号生成装置および同期信号生成方法を提供することである。

【解決手段】本発明に係る基地局3にパルスを提供する同期信号生成装置は、GPS衛星から受信した信号からGPS基準パルスを生成するGPS受信器11と、内部周波数信号を生成する発振器15と、内部周波数信号を分周して内部パルスを生成する分周器12と、GPS基準パルスと内部パルスとを比較して前記内部パルスを前記GPS基準パルスに同期させる同期部14と、基地局3の状態に応じて、ホールドオーバー状態からGPSロック状態に復帰するときの、同期部14のループタイムを決定する制御部13と、を備える。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】発振器のウォームアップの完了を容易に判定できるようにする。

【解決手段】クロック供給装置1は、通信装置内の処理に用いられるクロック信号を供給する。発振器1aは、クロック信号を生成する。測定部1bは、通信装置に接続された伝送路から抽出されたリファレンスクロック信号を取得し、クロック信号とリファレンスクロック信号との周波数ずれを測定する。判定部1cは、周波数ずれの測定結果と電力供給の状況とに基づいて、発振器1aのウォームアップが完了したか否か判定する。

(もっと読む)

PLL回路、PLL回路の動作方法およびシステム

【課題】 回路規模を増加することなく、PLL回路の精度を向上する。

【解決手段】 時間計測回路は、基準クロックの遷移エッジが現れてから、出力クロックの遷移エッジが2回現れるまでの時間間隔をカウント値として計測する。位相差正規化回路は、計測された時間間隔を出力クロックのクロック数で表される微少位相差に正規化する。また、位相差正規化回路は、PLL回路のロック後に、”1”または”2”を示す微少位相差が連続して現れるときに、”1”と”2”がランダムに現れるまで正規化係数を徐々にずらす。演算回路は、出力クロックの積算値から微少位相差の値を引いた値を、周波数制御語の積算値から差し引いて、基準クロックと出力クロックの位相差を示す位相差信号を生成する。発振回路は、基準クロックと出力クロックの位相を合わせるために、位相差信号に基づいて出力クロック信号の周波数を変更する。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有するPLL回路等を提供する。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

リファレンスリークの発生や位相ノイズを低減できるPLL回路

【課題】リファレンスリークを低減することができ、位相ノイズを抑制することができるPLL回路を提供する。

【解決手段】切り替え機能付き周波数位相比較器は、入力されるロック検出信号に基づいて、入力される2つの信号の立ち上がりエッジを検出することにより当該2つの信号の位相差を検出する周波数比較と、入力される2つの信号の電圧レベルを検出することにより当該2つの信号の位相差を検出する位相比較とを切り替えて行う。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

回路、制御システム、制御方法及びプログラム

【課題】ジッタ・ワンダ抑圧性能を満足しつつ、高速な周波数追従性能を実現することが可能な回路を提供する。

【解決手段】本実施形態の回路は、OTN(Optical Transport Network)信号からSDH(Synchronous Digital Hierarchy)信号及びEthernet信号のクロックを再生するPLL部100の位相比較データを基に、ジッタ・ワンダ成分及び周波数急変状態を検出、解析し、その結果を基に、PLL部100のループゲインを制御することを特徴とする。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

1 - 20 / 112

[ Back to top ]