Fターム[5J106HH03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 電圧、電流、電力 (414)

Fターム[5J106HH03]の下位に属するFターム

利得 (51)

Fターム[5J106HH03]に分類される特許

1 - 20 / 363

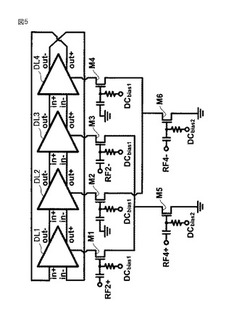

分周回路およびPLL回路

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

原子発振器

【課題】磁気量子数mF=0におけるEIT信号のピーク値を高くした原子発振器を提供する。

【解決手段】本発明の原子発振器100は、アルカリ金属原子に電磁誘起透過現象を発現させるための第1の共鳴光、及び第2の共鳴光を発生する半導体レーザー(光源)1と、半導体レーザー1から発生した共鳴光1aを円偏光するλ/4波長板2と、アルカリ金属原子が封入された原子セル3と、原子セル3から出射した共鳴光3aの強度を検出する光検出手段5と、アルカリ金属原子に所定の強度の直流磁場を与える直流磁場発生手段4と、直流磁場の強度に応じた所定の周波数の交流磁場をアルカリ金属原子に与える交流磁場発生手段8と、光検出手段5から出力された共鳴光の中心波長を制御する中心波長制御手段9と、アルカリ金属原子にEIT現象を発現させるように、第1の共鳴光と第2の共鳴光との周波数差を制御する制御手段10と、を備えて構成されている。

(もっと読む)

半導体装置及びこれを搭載する無線通信端末

【課題】回路規模の増大を抑止しつつ、ループ帯域の切替に際して生じるオフセットを補償する。

【解決手段】半導体装置(110)を構成する位相検出器(111)は、発振器(114)の出力信号を帰還した帰還信号と参照信号との間の位相差を検出し、位相差に応じた値を示す位相差値を生成する。増幅器(112)は、外部からの制御信号に応じて決定される増幅率で、位相差値を増幅する。フィルタ(113)は、増幅器(112)の出力値を平滑化する。発振器(114)は、フィルタ(113)の出力値に応じて、出力信号の周波数を制御する。

(もっと読む)

PLL回路

【課題】PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制できるようにする。

【解決手段】PLL部のチャージポンプ20及びループフィルタ30をスリープ状態にし、校正部60のループフィルタ62の出力電圧V’inと校正用電源66の出力電圧Vdd/2とを電圧比較器63で比較する。比較結果を基に、V’in≒Vdd/2となるように、電流制御装置64によりデジタル制御電圧を生成し、デジタルアナログ変換器65によりアナログ制御電圧V+、V-に変換し、VCO40内の電圧電流変換回路41に供給する。

(もっと読む)

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号が「断」となった場合には、SW3に可変電圧供給回路12からの出力電圧にループフィルタ4に出力させる切替信号を出力し、更にループフィルタ4からの出力電圧を1/N分圧器13で分圧した電圧を微調制御電圧とし、オフセット電圧供給回路15からの電圧を粗調電圧として加算器14で加算してOCXO5の制御電圧として出力する周波数シンセサイザである。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

位相ロック・ループにおけるVCOの動的バイアス印加

【課題】無線通信機器における局部発振器を提供する。

【解決手段】局部発振器が位相ロック・ループを含む。位相ロック・ループは電圧制御発振器23と新規のVCO制御回路27を含む。VCO制御回路はプログラム可能で設定可能であることが出来る。1つの例では、前記VCOの電力状態を変更するために、命令が前記VCO制御回路に受信される。命令は、セルラー電話における無線チャネル状態の検出された変化(例えば、信号対雑音判定の変化)に応答して、他の回路によって発せられる。応答して、VCO制御回路は、PLLのループ帯域幅を徐々に拡大し、次に該VCOバイアス電流を徐々に変更して該VCO電力状態を変更し、そして次にPLLのループ帯域幅を縮小して元の帯域幅に戻す、制御信号を出力する。PLL帯域幅を拡大すること、VCO電力状態を変更すること、及びPLL帯域幅を縮小すること、の全過程はPLLがロックされたままで行われる。

(もっと読む)

位相同期回路及びテレビジョン信号受信回路

【課題】チューニングラインに設けられるラインフィルタのフィルタ特性の低下を防止すること。

【解決手段】この位相同期回路は、チャージポンプ(35)から出力されるパルス信号を積分するローパスフィルタ(19)と、ローパスフィルタ(19)から電圧制御発振回路(17A)に対して制御電圧を供給する制御電圧供給ライン(LUHF)に設けられたラインフィルタ(20)と、を具備し、ラインフィルタ(20)のキャパシタ(C1)の一端をチャージポンプ(35)の出力端子からCP電流切替回路(36)の抵抗(r)を介してグランドに高周波的に接続した。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

制御装置、光受信装置および制御方法

【課題】特性の制御を安定させること。

【解決手段】制御装置120は、第1演算器122と、更新制御回路123と、取得部125と、第2演算器126と、を備えている。第1演算器122は、処理装置の第1特性の検出結果に基づいて、第1特性を変化させる処理装置のパラメータを操作する。更新制御回路123は、第1演算器122の機能を更新する場合に、第1演算器122によるパラメータの操作を停止させる。取得部125は、パラメータの操作量と、第1特性を変化させる処理装置の第2特性の変化量との関係を示す関係情報を取得する。第2演算器126は、更新制御回路123によって第1演算器122によるパラメータの操作が停止している場合に、取得部125によって取得された関係情報と、第2特性の検出結果の変化量と、に基づく操作量によってパラメータを操作する。

(もっと読む)

モータ速度制御装置、及び画像形成装置

【課題】安価な構成で、基準パルスと検出パルスの位相差を広範囲、且つ精密に検出でき、外乱に対しても同期はずれの生じる危険性を少なくして、精密なPLL制御が可能な速度制御装置を提供する。

【解決手段】本発明のモータ速度制御装置120は、tgt_frqに基づくrefclkを出力する基準クロック発生器101と、モータ107の所定回転角度ごとに所定数のfgを出力するエンコーダ108と、refpulseを出力する分周器102と、整数位相差ph_intとして出力する整数位相差検出器103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frcとして出力する小数位相差検出器104と、ph_intとph_frcを混合器105で所定の比率で加算してpherrとし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

(もっと読む)

高周波発振源

【課題】位相雑音の劣化を抑制することができる高周波発振源を得ることを目的とする。

【解決手段】所定の周波数で発振する基準発振器1と、その基準発振器の出力波が注入されていない場合の発振周波数が、その基準発振器の出力波の周波数の整数倍に設定されている(または設定される)注入同期発振器とを備え、その基準発振器から注入同期発振器に注入される電力を、注入同期発振器の低離調周波数の位相雑音が基準発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように、かつ高離調周波数の位相雑音が注入電力がない時の注入同期発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように適切な注入電力とする電力調整手段を設ける。

(もっと読む)

通信装置及び通信方法

【課題】PLL回路をベースとしたCDR回路を使用したトランシーバ間において、再同期を高速に行うことを目的とする。

【解決手段】PLL回路により構成されるクロック抽出部16に、受信信号を受信していない非受信状態の場合には、受信信号を受信している受信状態から非受信状態へ移行する時点におけるクロック信号の位相を示す位相情報を保持しておく受信側位相保持部22を追加する。データ送信時には、受信側位相保持部22が保持した位相情報を用いて生成されたクロック信号を用いて送信データを送信する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】ループフィルタをオンチップ化する際、トランジスタの素子サイズのバラツキによるPLL回路の特性バラツキを軽減して、回路規模と消費電力の増大を軽減する。

【解決手段】半導体集積回路は、位相周波数比較器1とループアッテネータ2とチャージポンプ3とループフィルタ4と電圧制御発振器5と分周器6を具備するフェーズロックドループ回路を内蔵する。アッテネータ2は、サンプリング回路21とカウンタ22とを含む。回路21にサンプリングパルスSPL_CLKと位相周波数比較器1から出力される第1と第2の出力信号が供給され、回路21はサンプリング出力信号を出力する。カウンタ22は回路21から出力される所定個数のサンプリングパルスのカウントアップを完了すると、カウントアップ完了出力信号を出力する。チャージポンプ3は、カウントアップ完了出力信号に応答してループフィルタ4に充電電流または放電電流を出力する。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【課題】電圧制御発振器の制御利得を発振周波数に対して比較的一定に維持し、位相ノイズを低減したプログラマブルバラクタ装置を提供する。

【解決手段】プログラマブルバラクタ装置100は、複数のデジタルバラクタビットB0、B1、B2によって制御される複数のバイナリ重み付けバラクタ104,106,108を含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。

(もっと読む)

1 - 20 / 363

[ Back to top ]