国際特許分類[H01L29/868]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅,発振またはスイッチされる電流を流す1つ以上の電極に電流または電圧のみの変化のみを与えることにより制御可能なもの (2,569) | ダイオード (2,495) | PINダイオード (194)

国際特許分類[H01L29/868]に分類される特許

11 - 20 / 194

半導体装置の製造方法

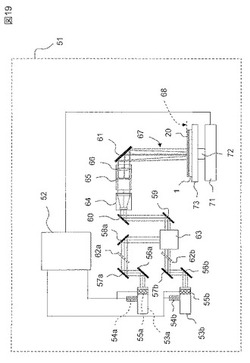

【課題】SiC半導体基板の裏面電極は、低コンタクト抵抗を実現するために、ニッケル等のシリサイド形成用メタル膜を堆積後、PDAとして摂氏1000度程度の熱処理を必要とする。この熱処理を通常の熱処理やRTAで実行する場合には、ウエハの表面側がアルミニウム等の融点を超えるため、アルミニウム膜等の形成前に実施しなければならないという制約がある。また、既存の紫外線レーザを用いたレーザアニールでは、コンタクト抵抗を十分に下げられないという問題がある。

【解決手段】本願の一つの発明は、SiC基板の表面側にアルミニウム系メタル膜が形成された状態で、裏面にシリサイド形成用メタル膜を成膜し、この裏面に対してレーザビームによってシリサイド化処理を実行する半導体装置の製造方法であって、このレーザビームを、前記シリサイド形成用メタル膜を実質的に透過しない波長域に属する可視光とするものである。

(もっと読む)

ダイオードの製造方法

【課題】 空乏層がp型領域からショットキー接続部に広がり易いダイオードの製造方法を提供する。

【解決手段】 半導体基板の一方の表面に形成されているアノード電極と、半導体基板の他方の表面に形成されているカソード電極と、半導体基板内に形成されており、アノード電極に対してオーミック接続されているp型領域と、半導体基板内に形成されており、p型領域に隣接しており、アノード電極に対してショットキー接続されており、カソード電極に対してオーミック接続されているn型領域を有するダイオードの製造方法。この製造方法は、p型不純物をマスクを通して半導体基板に注入する第1注入ステップと、その後に、第1注入ステップと注入深さを変更して前記p型不純物と同種のp型不純物を前記マスクと同一のマスクを通して半導体基板に注入する第2注入ステップとを実行することで、前記p型領域を形成する。

(もっと読む)

スーパージャンクション構造を有する半導体装置

【課題】高温環境下で半導体装置に長時間逆バイアスを与えた場合であってもリーク電流が増加したり耐圧が低下したりすることのない、スーパージャンクション構造を有する半導体装置を提供する。

【解決手段】n−型半導体層(第1導電型の半導体層)114と、活性領域R1に形成された複数の柱状埋込層118と、活性領域R1に形成されたショットキーバリアメタル層(第1電極層)132と、耐圧領域R2に形成された複数のガードリング層(環状柱状埋込層)124と、耐圧領域R2及び周辺領域R3に形成された絶縁層130とを備える、スーパージャンクション構造を有する半導体装置であって、周辺領域R3に形成された第2ガードリング層(第2環状柱状埋込層)136と、周辺領域R3に形成された環状導電層142とをさらに備える、スーパージャンクション構造を有する半導体装置100。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体装置

【課題】耐圧領域付近への電流集中と電力損失を抑制する半導体装置を提供する。

【解決手段】半導体装置1aは第1導電型の半導体基板2と、前記半導体基板の一方の側に設けられた第1主電極17と、前記半導体基板の他方の側に前記半導体基板の縁部から離れて設けられた第2導電型の第1半導体層11と、前記半導体基板の他方の側に前記縁部と前記第1半導体層との間において選択的に設けられた複数の第2導電型の第2半導体層12と、前記縁部から前記第1半導体層の一部を覆うように設けられた絶縁膜13と、前記絶縁膜及び前記第1半導体層の一部を覆うように設けられた導電膜14と、前記第1半導体層及び前記導電膜に接するように設けられた第2主電極15を有する。

(もっと読む)

半導体装置

【課題】SiCを含む基板を用いたショットキーダイオードのショットキー界面のドリフト層に結晶欠陥が生じている場合に、逆方向漏れ電流の発生を防ぐことで、半導体装置の信頼性を向上させる。

【解決手段】半導体基板上のドリフト層2とショットキー電極4とのショットキー接合部を含むショットキーダイオードにおいて、ドリフト層2の上面に達する結晶欠陥12の上面に、ショットキー電極4を構成する金属に応じて規定される濃度および深さで、アクセプタ不純物を導入してp型半導体領域3を形成し、逆方向漏れ電流の増大を防ぐ。

(もっと読む)

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

過渡電圧抑制器のための方法およびシステム

【課題】炭化シリコン過渡電圧抑制器(TVS)アセンブリを形成する方法および過渡電圧抑制器(TVS)アセンブリのためのシステムを提供する。

【解決手段】TVSアセンブリは、第1の極性の導電性を有する第1の広バンドギャップ半導体の第1の層306と、第1の層と電気的に接触して結合された第2の極性の導電性を有する第1または第2の広バンドギャップ半導体の第2の層308であって、第2の極性は第1の極性と異なる、第2の層とを含むメサ構造の半導体ダイ302を含む。TVSアセンブリはまた、第2の層と電気的に接触して結合された第1の極性の導電性を有する第1、第2、または第3の広バンドギャップ半導体の第3の層312も含む。第2の極性の導電性を有する層は、第1の極性の導電性を有する層に比して低濃度にドープされる。

(もっと読む)

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

半導体装置

【課題】高耐圧を確保できながら、逆方向リーク電流および順方向電圧を低減することができる半導体装置を提供すること。

【解決手段】その表面12にショットキーメタル22が形成されたエピタキシャル層6を備えるショットキーバリアダイオード1において、エピタキシャル層6の表面12に沿う方向に互いに間隔を空けて配列され、それぞれが表面12から裏面11へ向かってエピタキシャル層6の厚さ方向に延びるp型ピラー層17を形成することにより、エピタキシャル層6にスーパージャンクション構造を形成する。また、エピタキシャル層6の表面12の近傍に、p型ピラー層17よりも不純物濃度の高い電界緩和層19を選択的に形成する。

(もっと読む)

11 - 20 / 194

[ Back to top ]