Fターム[2G132AL00]の内容

電子回路の試験 (32,879) | 目的、その他 (6,788)

Fターム[2G132AL00]の下位に属するFターム

被試験体の識別、存在の検知 (22)

接続の確実化 (517)

接続の確認、誤接続の検出 (109)

接続線の本数の減少(端子数の減少) (295)

多品種への対応(汎用性のあるもの) (130)

試験時間の短縮 (1,339)

試験精度の向上 (1,554)

不良箇所、原因の特定等 (520)

試験装置の調整 (288)

インピーダンスマッチ (76)

温度調整 (87)

レベル変換 (8)

複数の被試験体の試験 (254)

母線(バス等)に接続した状態での試験 (19)

異常時の処理、保護 (119)

低機能装置で高機能素子を試験 (203)

試験装置の構成要素の配置改善 (287)

試験装置の動作試験 (78)

試験方法としては一般的なもの (13)

Fターム[2G132AL00]に分類される特許

861 - 870 / 870

半導体スイッチ回路

入力端子と出力端子との間に第1、第2、第3半導体スイッチを直列接続して挿入し、入力端子に接続された第1半導体スイッチ及び出力端子に接続された第3半導体スイッチのそれぞれに第1、第2電圧印加手段を並列接続し、それぞれの電圧印加手段を、利得が約+1の状態に設定され、入力側が入力端子及び出力端子に接続された直流増幅器と、電圧印加手段用半導体スイッチとの直列接続回路で構成し、この電圧印加手段用半導体スイッチの一端を第1と第2半導体スイッチの接続点Jまたは第2と第3半導体スイッチの接続点Kに接続し、スイッチ制御手段が第1〜第3半導体スイッチと電圧印加手段用半導体スイッチを逆モードでをオン及びオフ状態に制御し、第1〜第3半導体スイッチがオフ状態に制御されたときに、第1及び第2電圧印加手段が入力端子及び出力端子の電位を接続点J及びKに印加するように構成した半導体スイッチ回路。 (もっと読む)

電流測定装置及び試験装置と、これに用いる同軸ケーブル及び集合ケーブル

測定第1端子と、測定第2端子との間を流れる被測定電流を測定する電流測定装置であって、一端が測定第1端子と電気的に接続され、他端が測定第2端子と電気的に接続された複数の1次コイルと、複数の1次コイルに流れる被測定電流に応じて、被測定電流を示す電圧を生じる2次コイルと、それぞれが複数の1次コイルのそれぞれに対応し、対応する1次コイルの一端と測定第1端子とを電気的に接続する信号線と、シールドとを有する複数の同軸ケーブルとを備え、同軸ケーブルのそれぞれは、信号線と、信号線を被覆する絶縁層と、絶縁層の外周に巻き付けられたテープ状の導電体を有する第1のシールドと、第1のシールドの外周に設けられた導電体により構成される第2のシールドとを有することを特徴とする電流測定装置を提供する。 (もっと読む)

テストヘッド位置決めシステム

負荷を支持する第1支持構造体(60)と負荷を支持する第2支持構造体(4)とを備える、負荷を取り扱い操作する装置(1)であり、この装置は、また、第1支持構造体(60)と第2支持構造体(4)との間に結合されたカップリング(3)を有し、カップリング(30)は、負荷の重心が回転軸から離れて位置する回転軸の軸周りのコンプライアント動作範囲を負荷に対して与えるコンプライアント機構(340a)を有しており、この回転軸は非垂直の軸である。

(もっと読む)

(もっと読む)

電子部品における基準電圧の自己診断方法及び装置

電子部品における基準電圧の自己テストの方法を提供し、この方法により、オンチップテストの形態で実現可能な、すなわち外部基準電圧源を不要とする基準電圧の自己テストの回路装置が規定される。基準電圧(Uref)は、電圧制御型発振器に供給される。この発振器の出力は、ウィーン−ロビンソンブリッジの入力を形成する。このブリッジの出力信号は、そのブリッジの平衡状態をチェックするために当該ブリッジへの入力に対するその位相シフトに関する位相検出器においてチェックされる。ウィーン−ロビンソンブリッジは、基準電圧(Uref)のために選択された公称値(Uref.tes)で発振器において発生される周波数(Ωref.test)で平衡を保つように設定され、ブリッジが平衡を保つと合格信号が発生され、それ以外は不合格信号が発生される。  (もっと読む)

(もっと読む)

テストヘッド位置決めシステムと方法

負荷を支持するための装置は、空気装置と負荷の対向側面に連結される連結器を備える。連結器は、空気装置の作動に応答して、第1の軸と平行に負荷を移動させる。少なくとも1つの連結器は、第1の軸と直角の第2の軸を回転支点として負荷を回転させる。負荷は第1の軸方向に沿って移動するとともに第2の軸の回りにコンプライアント動作する。少なくとも1つの空気装置が第1の軸方向に沿った移動とともに第2の軸の回りのコンプライアンスを提供する。

(もっと読む)

(もっと読む)

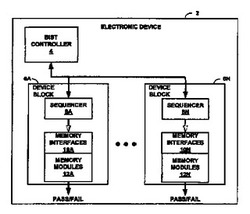

分散された命令解読及び一般化された命令プロトコルを有するメモリ内蔵自己診断(BIST)アーキテクチャ

【課題】分散された命令解読及び一般化された命令プロトコルを有するメモリ内蔵自己診断(BIST)アーキテクチャ。

【解決手段】分散されたアルゴリズム解読を有する内蔵自己診断(BIST)アーキテクチャが説明される。本アーキテクチャは、概念の3つの階層:中央集中化されたBISTコントローラ、シーケンサの組、及びメモリ・インタフェースの組、を含む。BISTコントローラは、メモリ・モジュールの物理的特性又はタイミング要求条件に関係なく、メモリ・モジュールを試験するためのアルゴリズムを包括的に規定する命令の組を記憶する。シーケンサは、命令プロトコルに従って命令を解読し、メモリ動作の系列を発生する。メモリ・インタフェースは、例えば、命令により説明されたビット・パターンを実現するために、メモリ・モジュールの行列配置に基づいてアドレス信号及びデータ信号を変換することにより、メモリ・モジュールの物理的特性に従ってメモリ・モジュールにメモリ動作を適用する。命令プロトコルは、強力なアルゴリズムが多様な特性を有するメモリ・モジュールに適用されることができる非常に簡潔な方法で説明されることを可能にする。

(もっと読む)

プローブカード装置

【課題】LSI開発の初期評価で使用するために、高額なLSIテストシステムを必要とせずにLSI検査システムの構築を可能にする。

【解決手段】LSI検査プログラムおよびLSI検査結果データを格納する不揮発性メモリとLSI検査プログラムを実行するCPUとを内蔵するLSIテストチップ111をプローブカード装置101に搭載し、LSI検査プログラムはパーソナルコンピュータ103に接続した専用治具を介してLSIテストチップにロードし、LSIテストチップは検査開始信号および検査終了信号によりウエハ検査搬送機102を制御してLSI検査プログラムを実行する。

(もっと読む)

検査用プローブ基板及びその製造方法

【課題】製造効率が良く、且つ半導体チップとの接触抵抗をより小さくして正確な検査を行なうことが可能である検査用プローブ基板及びその製造方法を提供すること。

【解決手段】銅箔を備えた基板に突起と該突起に接続する配線パターンとを形成する検査用プローブ基板の製造方法において、前記突起の形成は、Auボールをボンディングした後にAuワイヤをクランプしたキャピラリを移動することにより行ない、その後前記突起の上に第1のめっき及び第2のめっきを施したことにある。

(もっと読む)

スキャン多重化

【課題】DUT内のIC部品のテストのコスト効果及び時間効率を向上させる。

【解決手段】複数の状態データを各テスタメモリ位置(42及び44)に多重化することによって、スキャン動作の実効周波数を高くし、同時にメモリ容量を大きくすることができる。システム(10)は、テスト対象装置(DUT)(18)への入力刺激としての状態データのスキャンインシーケンス(14)と予測された状態データのスキャンアウトシーケンス(16)を提供するためのソースを含む。ベクトルプロセッサ(30)が、スキャンインシーケンス(14)と予測されたスキャンアウトシーケンス(16)を受け取り、多重化された状態データの交換を可能にする。多重化係数がmの場合には、装置サイクルレートをテスタサイクルレートのm倍にすることができる。多重化係数は、個々のテスタメモリ位置(42及び44)の記憶容量と、実効ベクトル交換レートをテスタサイクルレートのm倍にすることができるということに基づいて選択される。

(もっと読む)

低消費電力テスト回路

【課題】 この発明は、スキャンF/Fを使用した半導体装置のテストにおいて、消費電力を低減した低消費電力テスト回路を提供することを課題とする。

【解決手段】 この発明は、スキャンF/F11,12と遅延要素14との間に、テスト動作時又はテスト動作におけるスキャン動作時にのみスキャンデータを遅延要素14に与えるゲート回路13を挿入して構成される。

(もっと読む)

861 - 870 / 870

[ Back to top ]