Fターム[4K029BA17]の内容

Fターム[4K029BA17]に分類される特許

41 - 60 / 419

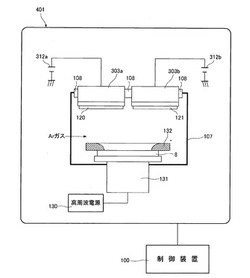

スパッタリング装置およびスパッタリング方法

【課題】1つの真空チャンバで複数の異種の基板に膜を形成することができると共に、高品質な半導体デバイスを生産できるスパッタリング装置を提供する。

【解決手段】排気系およびガス導入系と接続された真空チャンバ(107)と、真空チャンバ(107)内に設置されスパッタリング電源(312a)と接続された第1スパッタリングカソード(303a)と、真空チャンバ(107)内に設置されスパッタリング電源(312b)と接続された第2スパッタリングカソード(303b)と、基板(8)が載置される基板ホルダ(131)と、基板(8)に高周波電圧を印加して基板(8)を逆スパッタ(S12)する高周波電源(130)と、を備えたことを特徴とする。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】薄膜トランジスタの半導体層に酸化物半導体を用いたとき、薄膜トランジスタのスイッチング特性およびストレス耐性が良好な薄膜トランジスタの半導体層用酸化物を提供する。

【解決手段】本発明に係る薄膜トランジスタの半導体層用酸化物は、薄膜トランジスタの半導体層に用いられる酸化物であって、前記酸化物は、In、Ga、およびZnよりなる群から選択される少なくとも一種の元素と;Al、Si、Ni、Ge、Sn、Hf、Ta、およびWよりなるX群から選択される少なくとも一種の元素と、を含んでいる。

(もっと読む)

断続的コンベヤシステムを有するコータ

【課題】基板(例えば、大面積ガラス基板)上に膜を塗布するための方法およびコータを提供する。

【解決手段】シート状基板上に薄膜を塗布するためのコータ及び、基板をコータを通って延びる基板走行路に沿って搬送するよう適合させた移送システムであり、基板移送システムは、基板走行路の所望の一部に沿って搬送される際、コーティング材料を、上方向に、ギャップを通って基板の底主面上に供給するよう適合させたコーティング材料源を有する。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタル層の金属配線に対する密着性を向上させつつ、金属配線の低抵抗化を図った半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜15に形成された凹部16、17内にバリアメタル層20を形成した後、凹部16、17内にCu配線層23を形成する。バリアメタル層20の形成工程は、凹部16、17内にTi含有量が50原子%を超える第1のTiNx膜18を形成した後、側壁部上と比較して底部上に相対的に多く形成されるように、Ti含有量が第1のTiNx膜18より多い第2のTiNx膜(またはTi膜)19を形成する。

(もっと読む)

真空成膜装置用部品の製造方法

【課題】真空成膜装置で内部応力が大きい薄膜を成膜する際に、成膜工程中に付着する成膜材料の剥離を安定かつ有効に防止し、装置クリーニングや部品の交換などに伴う生産性の低下や成膜コストの増加を抑える。

【解決手段】Ti、Zr、Hf、Nb、Ta、W、Ru、Pd、Ir、Pt、Ag、AuおよびInから選ばれる金属元素の単体、もしくは前記金属元素を含む合金または化合物の薄膜を成膜する真空成膜装置の構成部品の製造方法であって、部品本体の表面にCuの含有比率が65〜95質量%の範囲のCu−Al合金からなるCu−Al合金膜を形成する工程と、前記Cu−Al合金膜に1.33×10−3Pa以下の真空雰囲気中で300〜800℃の温度でアニール処理を行う工程とを有する。

(もっと読む)

バッキングプレートの製造方法

【課題】スパッタリングの際のパーティクルの発生を効果的に低減し、かつ、Naを始めとするアルカリ金属不純物による汚染防止を図ることができるバッキングプレートを簡便に得られるバッキングプレートの製造方法を提供する。

【解決手段】スパッタリングターゲット2を保持するバッキングプレート1を製造する方法において、前記バッキングプレート1表面の前記スパッタリングターゲットが接合される領域以外、すなわち、外周部1a及び側周面1bの少なくとも一部を、レーザ加工により凹凸を形成して粗面化する工程を経る。

(もっと読む)

圧電体薄膜ウェハの製造方法、圧電体薄膜素子、及び圧電体薄膜デバイス

【課題】圧電体薄膜を短時間に精度よく微細加工することを可能とした圧電体薄膜ウェハの製造方法、圧電体薄膜素子、及び圧電体薄膜デバイスを提供する。

【解決手段】圧電薄膜ウェハ1は、基板上に形成された組成式(K1−xNax)NbO3(0.4≦x≦0.7)で表されるアルカリニオブ酸化物系ペロブスカイト構造の圧電体薄膜4に、Arを含むガスを用いてドライエッチングを行うエッチング工程と、放出されるイオンプラズマ中のNaの発光ピーク強度の変化を検出してエッチング速度を変更する工程とにより製造される。

(もっと読む)

スパッタリング装置

【課題】装置のダウンタイムを低減し生産性を向上するスパッタリング装置を提供する。

【解決手段】スパッタリング装置10は、外部より低圧な雰囲気に維持可能なチャンバ12と、チャンバ12内で基材14を保持する保持部16と、保持部16で保持された基材14に周面が対向するように設けられた回転可能な回転陰極18であって、表面のターゲット材料をスパッタリングするための電力が供給される筒状の回転陰極18と、回転陰極18の表面に金属材料を供給可能な金属材料供給手段と、成膜室22と金属材料供給室24との間のガスの移動を規制するガス遮蔽部材130と、を備える。金属材料供給手段は、化学反応により回転陰極18の表面にターゲット材料として成膜される原料を外部から供給可能な原料供給路220を有する。

(もっと読む)

硬質皮膜被覆切削工具

【課題】4μm以上に厚膜化した2層以上の硬質皮膜における圧縮応力を低減し、密着強度を確保し耐摩耗性に優れた硬質皮膜被覆切削工具を提供する。

【解決手段】超硬合金基材側の硬質皮膜層1および表面側の硬質皮膜層2を有し、硬質皮膜層1の組成は(AlaCr1−a)1−xNx(元素の含有量は原子比であり、0.5≦a<0.7、および0.48≦x≦0.52である。)で表され、X線回折における(111)面のピーク強度Ir、(200)面のピーク強度Isとしたとき、0.3≦Is/Ir<1であり、硬質皮膜層2の組成は、(Ti1−bSib)1−yNy(元素の含有量は原子比であり、0.01≦b≦0.15、および0.48≦y≦0.52である。)で表され、X線回折における(111)面のピーク強度Iu、(200)面のピーク強度Ivとしたとき、0.3≦Iv/Iu<1であることを特徴とする硬質皮膜被覆切削工具。

(もっと読む)

薄膜トランジスタの半導体層用酸化物およびスパッタリングターゲット、並びに薄膜トランジスタ

【課題】薄膜トランジスタのスイッチング特性に優れており、特に保護膜形成後も良好な特性を安定して得ることが可能な薄膜トランジスタ半導体層用酸化物を提供する。

【解決手段】本発明に係る薄膜トランジスタの半導体層用酸化物は、薄膜トランジスタの半導体層に用いられる酸化物であって、前記酸化物は、Zn、SnおよびSiを含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン構造を有するCu配線において、バリア膜の拡散防止機能を低下させずにCu配線内のCuの埋め込み性を改善し、半導体装置の歩留まりおよび信頼性を向上する。

【解決手段】ダマシン配線を有する半導体装置において、第2層間絶縁膜6に形成した配線溝G2およびビアホールV2のそれぞれの内壁にバリア膜としてTaN膜7およびCuと濡れ性の良いTiからなるTi膜8とを順に形成することにより、Ti膜8上に均一にCuシード膜9aを形成することを可能とする。これにより、Cuシード膜9aを電極として電界メッキ法によりCu膜9を形成した際に、配線溝G2およびビアホールV2内に空隙が形成されることを防ぐ。

(もっと読む)

半導体領域の形成方法及び蓄電装置の作製方法

【課題】放電容量を高める等の蓄電装置の性能を向上させることが可能な蓄電装置の作製方法を提供する。また、蓄電装置等に用いることで性能を向上させることが可能な半導体領域の形成方法を提供する。

【解決手段】導電層上に、LPCVD法により、結晶性半導体で形成される複数のウィスカーを有する結晶性半導体領域を形成し、シリコンを含む堆積性ガスを含む原料ガスの供給を停止した後、結晶性半導体領域を加熱処理する結晶性半導体領域の形成方法である。また、当該結晶性半導体領域を蓄電装置の活物質層として用いる蓄電装置の作製方法である。

(もっと読む)

圧電素子の製造方法、および液体噴射ヘッドの製造方法

【課題】環境に優しく、圧電体の配向性が高い圧電素子の製造方法を提供する。

【解決手段】本発明に係る圧電素子の製造方法は、鉄酸マンガン酸ビスマスランタンを主成分とする圧電体を含む圧電素子の製造方法であって、第1電極を形成する第1電極形成工程と、第1電極の上方に、前駆体を塗布する塗布工程と、前駆体を、150℃以上200℃以下の温度で熱処理する第1熱処理工程と、第1熱処理工程の後に、前駆体を、350℃以上450℃以下の温度で熱処理する第2熱処理工程と、第2熱処理工程の後に、前駆体を焼成することにより結晶化させて、圧電体を形成する焼成工程と、圧電体の上方に、第2電極を形成する第2電極形成工程と、を含む。

(もっと読む)

光学素子の成形方法

【課題】プレス成形において、曇りのない光学素子を得ることができ、歩留まりの向上、生産性の向上に寄与する光学素子の成形方法を提供する。

【解決手段】光学素子の成形面とされた一対の上型2及び下型3の成形面に、耐熱性及び易酸化性を有する保護膜6が形成された光学素子用成形型に、ビスマス系のガラス素材を収容し、光学素子用成形型を加熱してガラス素材を軟化させる加熱工程と、軟化したガラス素材を、プレス手段を用いて光学素子用成形型により加圧して光学素子形状を付与するプレス工程と、プレス工程後、光学素子用成形型を冷却し、光学素子形状を付与したガラス素材を固化させる冷却工程と、を有する光学素子の成形方法。

(もっと読む)

圧電体薄膜ウェハの製造方法、圧電体薄膜素子、及び圧電体薄膜デバイス

【課題】圧電体薄膜を短時間で微細加工することができるとともに、選択的に加工を停止させることができる圧電体薄膜ウェハの製造方法、圧電体薄膜素子、及び圧電体薄膜デバイスを提供する。

【解決手段】基板2上に圧電体薄膜4を備えた圧電体薄膜ウェハ1は、Arを含むガスを用いてイオンエッチングを行う第1の加工工程と、反応性ガスとArとを混合した混合エッチングガスを用いて反応性イオンエッチングを行う第2の加工工程とにより製造される。圧電体薄膜4だけを短時間でエッチングすることが可能である。

(もっと読む)

被成膜基材の前処理方法、被成膜基材への薄膜の成膜方法、プラズマCVD装置、蒸着装置、スパッタ装置及びプラスチック基材

【課題】薄膜と被成膜基材との密着性を十分に確保できる被成膜基材への薄膜の成膜方法を提供する。

【解決手段】本発明の一態様は、プラスチック又はプラスチックにSiO2及びAl2O3の少なくとも一方を分散させた材料からなる被成膜基材2の表面に酸素プラズマ処理、オゾン処理及び紫外線照射処理のいずれかの処理を施した後に、前記被成膜基材2の表面上に、プラズマCVD法、スパッタ法及び蒸着法のいずれかの方法により薄膜を成膜することを特徴とする被成膜基材への薄膜の成膜方法である。

(もっと読む)

無電解ニッケルメッキ膜の製造方法およびそれを用いた磁気記録媒体用基板

【課題】無欠陥の無電解ニッケルメッキ膜の製造方法の提供。

【解決手段】スパッタ法を用いて、基材上に99.99%以上の純度および2.5μm以上の膜厚を有するアルミニウム層を形成する工程と、無電解メッキを用いて、アルミニウム層の上に無電解ニッケルメッキ膜を形成する工程とを含むことを特徴とする無電解ニッケルメッキ膜の製造方法。ここで、基材とアルミニウム層との間に99.99%以上の純度を有するチタン層を形成する工程をさらに含んでもよい。

(もっと読む)

振動型ジャイロセンサ

【課題】安定した特性と高い強度を確保して振動子の振動特性を調整する。

【解決手段】本発明に係る振動型ジャイロセンサは、一方の面に圧電膜、駆動電極、一対の検出電極、及び配線接続端子が形成された振動型ジャイロセンサ素子と、この振動型ジャイロセンサ素子が実装されるランドが形成された支持基板とを備える。前記振動型ジャイロセンサ素子は片持ち梁状の振動子部を有し、前記一方の面側を前記支持基板側に向けて実装されているとともに、前記一方の面以外の領域を、前記振動子部の振動特性調整用の凹部が形成された被加工領域としている。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

微粒子の皮膜形成方法及びその装置

【課題】微粒子の表面全体に均一厚さのPVD皮膜を形成することができるようにする。

【解決手段】真空チャンバ1内に蒸着源2及びこれと一定の位置関係に保持された処理容器3を配置して、処理容器3内において微粒子にこれを運動させつつPVD皮膜を形成するようにした微粒子の皮膜形成方法において、処理容器3を、これが回転盤6の外周部に複数のバケット7を周方向に並列配置してなるものとして、回転盤表面6aの水平面12に対する角度αが1°〜75°となる傾斜状態で回転盤表面6aに直交する軸線14回りで一定方向Rに回転させることにより、上方へと回行したバケット7から回転盤表面6a上に放出された微粒子が当該表面6a上を転動しつつ流下して下方に位置するバケット7に流入するようにして、微粒子に、これが回転盤表面6a上を転動,流下する間において、PVD皮膜を形成するようにする。

(もっと読む)

41 - 60 / 419

[ Back to top ]