Fターム[4K029CA06]の内容

Fターム[4K029CA06]に分類される特許

121 - 140 / 2,017

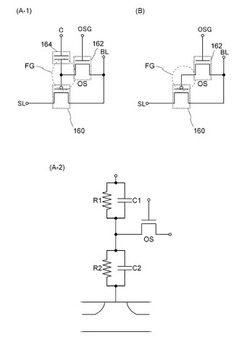

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

太陽電池用スパッタリングターゲット

【課題】スパッタ初期のスパッタレートが高く、かつスパッタレートの経時的な低下が小さく、さらに均質な膜が形成できる太陽電池用スパッタリングターゲットを提供する。

【解決手段】インジウム製の鋳塊に物理的応力を加える加工を行って該鋳塊の厚みを元の厚みの70%以下にすることにより得られたターゲット材とバッキングプレートとを、インジウム-スズまたはインジウム-ガリウム合金製のボンディング材により接合することにより形成されたことを特徴とする太陽電池用スパッタリングターゲット。

(もっと読む)

光情報記録媒体用記録膜および光情報記録媒体、並びに上記記録膜の形成に用いられるスパッタリングターゲット

【課題】光情報記録媒体の層数を低減しながら、所定の要求特性(低い記録パワーで記録が可能であること、高い変調度を有すること、低いジッター値を有すること、再生に十分な高い反射率を有すること)をすべて満足し、生産性を高めることのできる光情報記録媒体用記録膜を提供する。

【解決手段】本発明の光情報記録媒体用記録膜は、レーザー光の照射により記録が行われる光情報記録媒体用記録膜であって、Mnと;Bi、Ag、Co、Cu、In、Sn、およびZnよりなる群(X群)から選択される少なくとも一種の元素(X群元素)と;酸素(O)と、を含み、Mnの少なくとも一部、およびX群元素の少なくとも一部が酸化されている。

(もっと読む)

成膜方法及び成膜装置

【課題】 成膜したフッ素含有樹脂からなる有機層と無機層との密着性が高い成膜方法及び成膜装置を提供する。

【解決手段】 成膜方法は、被処理基板2に成膜された無機物からなる無機層3上にフッ素含有樹脂からなる有機層を形成する成膜方法であって、無機層を形成する際に、反応性ガスとして水蒸気を用いた反応性スパッタリングを行って被処理基板上に無機層を形成し、次いで無機層上に有機層を形成する。成膜装置は、この成膜方法を実施できる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】新規な非シリコン系半導体薄膜を用いた薄膜トランジスタを提供する。

【解決手段】ガリウムが酸化インジウムに固溶していて、原子比Ga/(Ga+In)が0.001〜0.12であり、全金属原子に対するインジウムとガリウムの含有率が80原子%以上であり、In2O3のビックスバイト構造を有する酸化物薄膜を用いることを特徴とする薄膜トランジスタ。

(もっと読む)

圧電膜素子、圧電膜素子の製造方法、及び圧電デバイス

【課題】非鉛の圧電膜と下部電極とのエッチング選択性を確保するとともに、高精度に加工することができる圧電膜素子、圧電膜素子の製造方法、及び圧電デバイスを提供する。

【解決手段】圧電膜素子1は、基板2と、基板2上に形成されたPt又はPtを主成分とする合金からなる第1の下部電極層4と、第1の下部電極層4上に形成されたTi、Cr若しくはこれらのいずれかを主成分とする合金の単層又は積層体からなる第2の下部電極層5と、第2の下部電極層5上に形成されたペロブスカイト構造を有する非鉛のアルカリニオブ酸化物系化合物からなる圧電膜7と、圧電膜7上に形成された上部電極とを備える。

(もっと読む)

耐食導電性皮膜とその製造方法および耐食導電材

【課題】耐食性および導電性に優れる耐食導電性皮膜を提供する。

【解決手段】本発明の耐食導電性皮膜は、P、TiおよびOからなるアモルファス相を少なくとも一部に有してなる。この耐食導電性皮膜が基材表面に形成された耐食導電材は、従来になく優れた耐食性および導電性を発現する。特にTi原子比(Ti/Ti+P)が0.5〜0.8である場合やNが導入された場合、その耐食導電性皮膜の耐食性は、導電性を低下させることなく著しく向上する。本発明の耐食導電性皮膜は、腐食環境下で高い導電性が要求される電極等に用いられると好ましい。例えば、本発明の耐食導電性皮膜により表面が被覆された燃料電池用セパレータは、耐食性および導電性に優れて好適である。

(もっと読む)

スパッタリング方法

【課題】耐熱温度の低い樹脂材料などに、膜応力が大きい膜材料を成膜するときに、膜クラックの発生が少なく、環境試験寿命を大幅に長くできるスパッタリング方法を提供することを目的としている。

【解決手段】樹脂基板9などに高屈折率膜15,低屈折率膜16,高屈折率膜17,低屈折率膜18をスパッタする場合に、スパッタの開始前の圧力を10−1Pa台の低真空として、膜応力を引張応力とすることを特徴とする。

(もっと読む)

窒化ガリウム柱状構造の形成方法、及び窒化ガリウム柱状構造の形成装置

【課題】触媒金属の混入を抑えることの可能な窒化ガリウム柱状構造の形成方法、及び該方法を用いる窒化ガリウム柱状構造の形成装置を提供する。

【解決手段】

窒化ガリウム柱状構造を下地層上に反応性スパッタによって形成する。このとき、真空槽11内に供給されるアルゴンガス及び窒素ガスの総流量に占める窒素ガスの流量の割合である窒素濃度を窒化ガリウム膜の成長速度が窒素供給によって律速され、且つ、窒化ガリウムの成長速度における極大値の91%以上100%以下の窒化ガリウムの成長速度となるような窒素濃度とする。また、基板Sの温度T、ガリウムのターゲット14に供給される周波数が13.56MHzであるバイアス電力Pが、600≦T≦1200、0<P≦4.63、P<0.0088T−6.60、P≧0.0116T−11.37を満たす条件にて窒化ガリウム柱状構造を形成する。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

透明導電性フィルム、その製造方法及びそれを備えたタッチパネル

【課題】ペン入力耐久性および高温高湿信頼性に優れる透明導電体層を有する透明導電性フィルムを提供すること。

【解決手段】透明なフィルム基材の片面に少なくとも1層のアンダーコート層を介して、透明導電体層を有する透明導電性フィルムであって、前記透明導電体層は、厚さdが15〜35nmであり、平均表面粗さRaが0.37〜1nmであることを特徴とする透明導電性フィルム。

(もっと読む)

ガスバリアフィルムの製造方法及び製造装置並びにガスバリアフィルム

【課題】可視光域の透過性がよく、水蒸気バリア性にも優れるガスバリアフィルムの製造方法及び製造装置を提供する。

【解決手段】長尺の基材フィルム1に対向配置させた1組又は2組以上のデュアルターゲット42を備えた反応性マグネトロンスパッタリング装置20を用い、その装置20内の成膜圧力を0.05Pa以上0.12Pa以下とし、デュアルターゲット42を構成する各ターゲット43,43の法線方向の磁束密度を基材フィルム1の幅方向(TD方向)で250G以上として、基材フィルム1を移動させながら基材フィルム1上に酸化珪素膜2を成膜する、ガスバリアフィルム10の製造方法によって、上記課題を解決した。デュアルターゲット42には交流波形又はパルス波形の電圧を印加することが望ましい。

(もっと読む)

金属薄膜積層基板の製造方法及び静電容量型タッチパネルの製造方法

【課題】ロール・ツー・ロールで搬送される長尺の樹脂フィルムの両面に金属薄膜を成膜する場合に、第1の面の金属薄膜の表面と第2の面の金属薄膜の表面とがくっつくことによる、しわ、膜剥がれ等の不具合を防ぐことができ、両面積層基板の生産効率を低下させることのない金属薄膜積層基板の製造方法を提案する。

【解決手段】長尺のフィルム基板Fの両面に金属薄膜を真空成膜により成膜したのち、該金属薄膜の少なくとも一方の金属薄膜の表面に金属酸化物の薄膜を形成し、その後金属薄膜積層基板Fをロール状に巻き取ることを特徴とする。

(もっと読む)

121 - 140 / 2,017

[ Back to top ]