Fターム[4M104BB34]の内容

Fターム[4M104BB34]に分類される特許

61 - 80 / 257

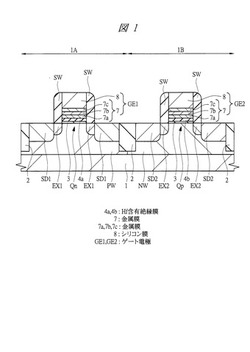

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域にエピタキシャル結晶を含み、エピタキシャル結晶上の金属シリサイドに起因する接合リークの発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、ファセット面13fを有するエピタキシャル結晶層13を有するMISFET10と、MISFET10を他の素子から電気的に分離し、上層3aのゲート電極12側の端部の水平方向の位置が下層3bのそれよりもゲート電極12に近く、上層3aの一部がファセット面13fに接する素子分離絶縁膜3と、エピタキシャル結晶層13の上面、およびファセット面13fの上層3aとの接触部よりも上側の領域に形成されたシリサイド層18と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:ハフニウムおよび/またはジルコニウムを含む第1の酸化物材料を含む高誘電体層と;前記高誘電体層の上部に蒸着され、ランタン、ランタニド、および/または、アルミニウムを含む第2の酸化物材料を含むキャップ層と、を備えたスタックを準備する工程と;酸化剤を含む水溶液である液体Aを前記半導体ウエハの表面に供給する工程SAと;工程SAの後に、6未満のpH値の液体である液体Bを前記半導体ウエハの前記表面に供給する工程SBと;工程SBの後に、少なくとも10ppmのフッ素濃度の酸性水溶液である液体Cを前記半導体ウエハの前記表面に供給する工程SCとを備える方法が開示されている。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜及びメタルゲート電極を備えたCMISFETの生産性や性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有絶縁膜5を形成し、その上に窒化金属膜7を形成し、窒化金属膜7上のフォトレジストパターンをマスクにしたウェットエッチングによって、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aの窒化金属膜7を選択的に除去する。それから、希土類元素を含有するしきい値調整層8を形成し、熱処理を行って、nMIS形成領域1AのHf含有絶縁膜5をしきい値調整層8と反応させるが、pチャネル型MISFET形成予定領域であるpMIS形成領域1BのHf含有絶縁膜5は、窒化金属膜7があるためしきい値調整層8とは反応しない。その後、未反応のしきい値調整層8と窒化金属膜7を除去してから、nMIS形成領域1AとpMIS形成領域1Bにメタルゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのしきい値電圧制御のために使用する金属酸化膜の膜減り等に起因するしきい値電圧ばらつきを抑制し、所望のしきい値電圧を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に、高融点金属酸化物を含む材料からなるゲート絶縁膜3が形成され、ゲート絶縁膜3上に金属酸化膜4が形成される。次いで、金属酸化膜4を構成する金属原子を、金属酸化膜4からゲート絶縁膜3の表面部へ拡散させる処理が実施される。当該金属原子の拡散工程後、上記金属酸化膜4がゲート絶縁膜3に対して選択的に除去される。そして、金属原子が拡散されたゲート絶縁膜3上に導電膜7、8が形成され、当該導電膜7、8を加工することでゲート電極30、31が形成される。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

炭化珪素半導体装置

【課題】炭化珪素半導体装置のpベースオーミックコンタクトは、高濃度イオン注入により形成されるp++層と金属電極とで構成される。高濃度イオン注入を室温で行うと、p++層の結晶が著しく劣化しプロセス不良の原因となるため、高温中で注入を行う方法が用いられる。デバイスのスイッチング損失等の観点から、pベースオーミックコンタクト抵抗率はより低いことが望ましい。

【解決手段】上記イオン注入工程に於いて、炭化珪素ウェハの温度を175〜300℃、望ましくは175〜200℃に保持しておく。175〜300℃でのイオン注入により形成されるp++領域を用いたpベースオーミックコンタクト抵抗率は8E−4Ωcm2以下となり、300℃を超える温度でイオン注入した場合よりも低くなる。又、プロセス不良も発生しない。

(もっと読む)

ダイヤモンド電極構造

【課題】 高温あるいは強反応性化学物質中においても金属、ダイヤモンド接合の品質を保持したまま、機能を発揮するダイヤモンド電極構造を提供する。

【解決手段】

ダイヤモンド表面にルテニウム(Ru)もしくは酸化ルテニウム(RuO2)からなる電極を設けることにより、電気的接合を行うことを特徴とするダイヤモンド電極構造。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置の製造方法

【課題】異なる積層構造を有する異なる導電型のトランジスタにおいて、ゲート電極における形状不良の抑制を図る。

【解決手段】半導体装置の製造方法は、第1導電型のMISFETを有する第1領域及び第2導電型のMISFETを有する第2領域における半導体基板1上に、ゲート絶縁膜3を形成する工程と、前記第1領域における前記ゲート絶縁膜上に、第1金属材料層4を形成する工程と、前記第1領域における前記第1金属材料層上及び前記第2領域における前記ゲート絶縁膜上に、第2金属材料層7からなる第2ゲート電極7a及び7bをそれぞれ形成する工程と、前記第1領域及び前記第2領域における前記第2ゲート電極の側面に、第1側壁絶縁膜11a及び11bをそれぞれ形成する工程と、前記第1側壁絶縁膜をマスクとして、前記第1領域における前記第1金属材料層を加工して第1ゲート電極4aを形成する工程と、を具備する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】カーバイド化する金属を用いて、あるいはカーバイド化する金属とシリサイド化する金属とを組み合わせてオーミック電極を形成する際に、より低抵抗化ができるSiC半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bに、カーバイドを生成する金属を含む金属薄膜50を形成する金属薄膜形成工程を実施したのち、金属薄膜50とSiCに含まれるCとを反応させてカーバイド層70を形成する電極形成工程を実施し、その後、カーバイド層70の表面に生じたシリコン粒子やシリコンの酸化物を除去する除去工程を行うことにより、カーバイド層70を含むドレイン電極11を形成する。

(もっと読む)

半導体装置の製造方法

【課題】素子特性を劣化させることなく、しきい値電圧の低い、金属のゲート電極を有するPチャネルMOSトランジスタを備えた半導体装置を製造することを可能にする。

【解決手段】半導体領域2上にゲート絶縁膜5を形成するステップと、第1金属元素と、OH基、NOx(x=1,2)基のうち少なくとも一つを含有する酸素含有金属層6をゲート絶縁膜上に形成するステップと、酸素含有金属層上に第2金属元素を含むゲート電極膜7を形成するステップと、ゲート電極膜を形成した後、酸素含有金属層の熱分解反応或いは脱水反応が生じる温度以上に加熱するステップと、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

61 - 80 / 257

[ Back to top ]