Fターム[4M104BB38]の内容

Fターム[4M104BB38]に分類される特許

21 - 40 / 553

半導体装置用Al合金膜

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられた半導体装置用Al合金膜を提供する。

【解決手段】500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が500nm〜5μmであることを特徴とする半導体装置用Al合金膜。(a)Alマトリックスの最大粒径が800nm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、480℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が1〜5μmであることを特徴とする半導体電極構造。

(a)Alマトリックスの最大粒径が1μm以下

(b)ヒロック密度が1×109個/m2未満

(c)電気抵抗率が10μΩcm以下

(もっと読む)

Cu合金膜および表示装置

【課題】酸化物半導体層を用いた表示装置において、保護膜形成時のプラズマ処理におけるCu配線の酸化を有効に防止し得る技術を提供する。

【解決手段】基板1の上に、基板側から順に、薄膜トランジスタの半導体層4と、電極に用いられるCu合金膜5と、保護膜6と、を備えており、半導体層は酸化物半導体からなる。Cu合金膜5は、基板側から順に、第一層(X)5aと第二層(Z)5bを含む積層構造を有し、第一層(X)は、純Cu、またはCuを主成分とするCu合金であって第二層(Z)よりも電気抵抗率の低いCu合金からなり、第二層(Z)は、Zn、Ni、Ti、Al、Mg、Ca、W、Nb、希土類元素、Ge、およびMnよりなる群から選択される少なくとも1種の元素を合計で2〜20原子%含むCu−Z合金からなり、第二層(Z)の少なくとも一部は、前記保護膜と直接接続されている。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】ゲート絶縁層と、ゲート絶縁層の一方の面に接する第1のゲート電極と、ゲート絶縁層の他方の面に接し、第1のゲート電極と重畳する領域に設けられた酸化物半導体層と、酸化物半導体層と接するソース電極、ドレイン電極、及び酸化物絶縁層と、の積層構造を有し、酸化物半導体層の窒素濃度は2×1019atoms/cm3以下であり、ソース電極及びドレイン電極は、タングステン、白金及びモリブデンのいずれか一又は複数を含む半導体装置を提供する。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

導電性膜形成用銀合金スパッタリングターゲットおよびその製造方法

【課題】 ターゲットの大型化に伴い、ターゲットに大電力が投入されてもスプラッシュを抑制することができると共に、耐食性および耐熱性に優れ、低電気抵抗の膜を形成可能な導電性膜形成用銀合金スパッタリングターゲットおよびその製造方法を提供すること。

【解決手段】 導電性膜形成用銀合金スパッタリングターゲットが、Ga,Snの内の1種または2種を合計で0.1〜1.5質量%を含有し、残部がAgおよび不可避不純物からなる成分組成を有した銀合金で構成され、銀合金の結晶粒の平均粒径が120〜400μmであり、結晶粒の粒径のばらつきが、平均粒径の20%以下である。

(もっと読む)

配線膜、薄膜トランジスタ、ターゲット、配線膜の形成方法

【課題】信頼性の高い薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ20のゲート電極15、ソース、ドレイン電極33、34のうち、いずれか一つ以上の電極はバリア膜25を有し、バリア膜25が成膜対象物21又は半導体層30に密着している。NiとMoを100原子%としたときに、バリア膜25は、Moを7原子%以上70原子%以下含有し、ガラスからなる成膜対象物21や半導体層30に対する密着性が高い。また、バリア膜25表面にCuを主成分とする金属低抵抗層26が形成された場合に、Cuが半導体層30に拡散しない。

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理後も低い電気抵抗率を有する新規なCu合金膜を提供する。

【解決手段】基板上にて、基板及び/又は絶縁膜と直接接触するCu合金膜であって、前記Cu合金膜は基板側から順に、合金成分としてX(Xは、Ag、Au、C、W、Ca、Mg、Al、Sn、BおよびNiよりなる群から選択される少なくとも一種の元素)を含有するCu−Mn−X合金層(第一層)と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる層(第二層)で構成されたCu合金膜である。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

半導体装置とその製造方法

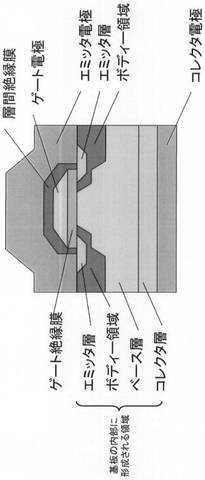

【課題】高耐圧な半導体素子を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、第一と第二の主面を有する炭化珪素基板と、炭化珪素基板の第一の主面に設けられた第一導電型の第一の炭化珪素層と、第一の炭化珪素層の表面に形成された第二導電型の第一の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第一導電型の第二の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第二導電型の第三の炭化珪素領域と、第一の炭化珪素層、第一の炭化珪素領域および第三の炭化珪素領域の表面に連続的に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された炭化珪素からなる第一の電極と、第一の電極上に形成された第二の電極と、第一と第二の電極を被覆する層間絶縁膜と、第二の炭化珪素領域と第三の炭化珪素領域と電気的に接続される第三の電極と、炭化珪素基板の第二の主面に形成された第4の電極と、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

ダイオード用半導体担持電極材料

【課題】良好な整流特性を示すショットキー型ダイオードデバイスに利用可能な、半導体層を担持した安価な材料を提供する。

【解決手段】Cr含有量が10.5〜32.0質量%であるFe−Cr系合金の母材21と、その母材を酸化性雰囲気に加熱することによって形成させた表面酸化皮膜22とが一体となった材料であって、AESによる前記酸化皮膜表面からの深さ方向分析において酸素濃度が最大酸素濃度の1/2となる深さ位置に対応するSiO2換算深さを当該酸化皮膜の膜厚とするとき、当該酸化皮膜は、膜厚が17〜50nmのn型半導体であり、かつ皮膜表面側から順にFe主体アモルファス酸化物、Cr濃化したFe−Cr結晶酸化物を形成して母材とオーミック接合で一体化しており、n型半導体中のドナー密度が1E16cm−3〜1E18cm−3の範囲で含まれているダイオード用n型半導体担持電極材料。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

酸化物膜の製造方法

【課題】p型の導電膜及びp型の透明導電膜としての高性能な酸化物膜の、量産性に優れた製造方法を提供する。

【解決手段】

本発明の1つの酸化物膜の製造方法は、酸素を含むガスの雰囲気下で、反応性スパッタリング法により、銅(Cu)からなる第1ターゲット30a,30aとニオブ(Nb)およびタンタル(Ta)からなる群から選択される1種類の遷移元素からなる第2ターゲット30b,30bとを用いて交互にスパッタを行うことにより、基板10上に第1酸化物膜(不可避不純物を含み得る)を形成する工程、及びその第1酸化物膜を不活性ガス雰囲気中で加熱焼成することにより第2酸化物膜(不可避不純物を含み得る)を形成する工程を含む。従って、この製造方法によって形成された酸化物膜は、大型基板上への膜の形成が容易になることから、量産性に優れている。

(もっと読む)

Al基合金スパッタリングターゲット、及びCu基合金スパッタリングターゲット

【課題】Al基合金スパッタリングターゲットやCu基合金スパッタリングターゲットを用いたときのプレスパッタリング時、及び続いて行われる基板等へのスパッタリング時の成膜速度が高められ、且つスプラッシュなどのスパッタリング不良を抑制し得る技術を提供すること。

【解決手段】Al基合金またはCu基合金スパッタリングターゲットの最表面から1mm以内の深さのスパッタリング面法線方向の結晶方位<001>±15°と、<011>±15°と、<111>±15°と、<112>±15°と、<012>±15°との合計面積率をP値としたとき、下記(1)および/または(2)の要件を満足するスパッタリングターゲット。

(1)前記P値に対する、<011>±15°の面積率PA:40%以下、

(2)前記P値に対する、<001>±15°と<111>±15°との合計面積率PB:20%以上

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体用銅合金配線及びスパッタリングターゲット並びに半導体用銅合金配線の形成方法

【課題】半導体用銅合金配線自体に自己拡散抑制機能を有せしめ、活性なCuの拡散による配線周囲の汚染を効果的に防止することができ、またエレクトロマイグレーション(EM)耐性、耐食性等を向上させ、バリア層が任意に形成可能かつ容易であり、さらに半導体用銅合金配線の成膜工程の簡素化が可能である半導体用銅合金配線及び同配線を形成するためのスパッタリングターゲット並びに半導体用銅合金配線の形成方法を提供する。

【解決手段】Mn0.05〜5wt%を含有し、Sb,Zr,Ti,Cr,Ag,Au,Cd,In,Asから選択した1又は2以上の元素の総量が10wtppm以下、残部Cuである自己拡散抑制機能を備えた半導体用銅合金配線。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】材料の選択幅が広く、生産性が高いTFT、アクティブマトリクス基板、およびそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2と、半導体層5と、半導体層5の上に設けられ、半導体層5と電気的に接続されたソース電極7、及びドレイン電極8と、を備えた薄膜トランジスタであって、半導体層5が、透光性半導体膜5aと、透光性半導体膜5a上に配置され、透光性半導体膜5aよりも光透過率の低いオーミック導電膜5bと、を有し、オーミック導電膜5bが、透光性半導体膜5aからはみ出さないように形成され、オーミック導電膜5bが、ソース電極7とドレイン電極8の間のチャネル部9を挟むように分離して形成され、ソース電極7、及びドレイン電極8が、オーミック導電膜bを介して、透光性半導体膜5aに接続されているものである。

(もっと読む)

スパッタリングターゲット、半導体装置および半導体装置の製造方法

【課題】Cu配線層に含まれるCuの周囲への拡散を抑制すると共に密着性および動作特性に優れた半導体装置およびその製造方法、並びに、その半導体装置の製造に用いるスパッタリングターゲットを提供する。

【解決手段】実施の形態に係るスパッタリングターゲットは、1.5原子%以上5.0原子%以下のMnと、(Mgの原子%)/(Mnの原子%)で示される比率が0.3以上2.1以下となるMgと、10wtppm以下のCと、2wtppm以下のO2と、を含むCu合金を用いて形成される。

(もっと読む)

21 - 40 / 553

[ Back to top ]