Fターム[4M104DD52]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 塗布、又は液体からの析出 (2,321) | 電解メッキ (613)

Fターム[4M104DD52]に分類される特許

141 - 160 / 613

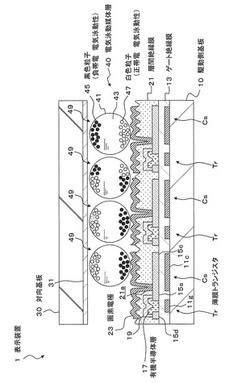

表示装置および表示装置の製造方法

【課題】有機半導体層を用いた薄膜トランジスタと画素電極とを含む層間に発生する応力を緩和することが可能で、これによりトランジスタ特性の劣化を防止して、表示特性および信頼性の向上が図られた表示装置を提供する。

【解決手段】有機半導体層を用いた薄膜トランジスタが配列形成された基板と、薄膜トランジスタを覆う状態で基板上に設けられた層間絶縁膜と、層間絶縁膜上に設けられた画素電極とを備えたものである。特に、層間絶縁膜は、薄膜トランジスタよりも平面視的なサイズが小さい凹凸パターンからなる凹凸表面を有しており、この凹凸表面上に画素電極が設けられていることを特徴としている。

(もっと読む)

銀含有金属オーミック接触電極

【課題】既存の業界工程と互換でき、有効に、生産コストを低減できる銀含有金属オーミック接触電極を提供する。

【解決手段】ニッケル(Ni)層とゲルマニウム(Ge)層、銀(Ag)層、パラジウム(Pd)層或いはプラチナ(Pt)層及び厚い膜金属(Thick Metal)層からなり、順に、n形III-V族化合物半導体層上に堆積されてから、アニール(Anneal)処理を介して形成された構造で、上記銀層とゲルマニウム層との厚さ比例範囲が、Ag/Ge=7〜8の間にある。また、上記の低い電気抵抗率(Electric

Resistivity)と高い熱伝導率(Thermal Conductivity)のオーミック接触電極は、銀が材料として形成される。

(もっと読む)

めっき方法及びめっき装置

【課題】貫通電極用凹部の底部からのめっき膜の成長速度を遅くすることなく、貫通電極用凹部内に銅等の金属を、内部にボイド等の欠陥を生じさせることなく完全に充填することができるめっき方法を提供する。

【解決手段】表面に貫通電極用凹部12を有する基板Wとアノードとをめっき液中に互いに対峙させて配置し、基板Wとアノードとの間に電圧を印加しながら基板Wとアノードとの間のめっき液を攪拌して貫通電極用凹部12内へ金属を充填し、貫通電極用凹部内12への金属の充填量に相関して、基板とアノードとの間のめっき液の攪拌条件を変化させる。

(もっと読む)

電解銅めっき浴および電解銅めっき方法

【課題】本発明の目的は、微細な構造であっても溝や穴に電解銅めっきによって銅を良好に埋め込むことのできる抑制剤と、促進剤および平滑剤を必須の有効成分として含有する電解銅めっき浴、およびこの電解銅めっき浴を用いた電解銅めっき方法を提供することにある。

【解決手段】本発明は、特定のブロック重合体化合物からなる抑制剤を0.001〜5質量%;特定の促進剤を0.01〜100質量ppm;およびジアリルアミンと硫酸化合物との塩・マレイン酸共重合体、ビニルピロリドン・N,N−ジメチルアミノエチルメタクリル酸共重合体と硫酸化合物との塩、塩化メチルビニルイミダゾリウム・ビニルピロリドン共重合体、N−アシル−N’−カルボキシエチル−N’−ヒドロキシエチルエチレンジアミンまたはそのアルカリ金属塩(ここで、アシルは、炭素数8〜20の脂肪族アシル基を示す)から選ばれる少なくとも1種の平滑剤を0.01〜250質量ppmを含有してなることを特徴とする電解銅めっき浴に係る。

(もっと読む)

半導体基板のコンタクト形成方法

【課題】半導体基板とのコンタクトを形成する方法、とくに太陽電池とのコンタクトを形成するのに適し、少ない労力でできるだけ高い接触品質が得られる方法を提供する。

【解決手段】基板(10)の表面上に金属種晶構造(26)をLIFTプロセスによって生成してコンタクトを形成する。その後種晶構造(26)を強化する(28)。

(もっと読む)

電子素子

【課題】簡便な方法で製造することができる電子素子を提供する。

【解決手段】第1の電極及び第2の電極を有し、該第1の電極と該第2の電極との間に有機材料を含む有機層を有し、該有機材料が該第1の電極又は該第2の電極と直接又は他の層を介して電子の授受を行う電子素子において、該第1の電極が金属又は金属の合金を含み、該金属又は金属の合金の融点が100℃以下であることを特徴とする電子素子。金属の合金がガリウムを含むことが好ましい。電子素子としては、有機エレクトロルミネッセンス素子、光電変換素子等が挙げられる。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置の製造方法

【課題】最新の0.15μmパワーMOSFETにおいては、微細化によるセル・ピッチの縮小のためトレンチ部(ソース・コンタクト用の溝)において、アルミニウム・ボイド(アルミニウム系電極内に形成されるボイド)が多発することが、本願発明者らによって明らかにされた。この欠陥の発生は、主にアスペクト比が前世代の0.84から一挙に2.8に上昇したことによると考えられる。

【解決手段】本願の一つの発明は、アスペクト比の大きい繰り返し溝等の凹部をアルミニウム系メタルで埋め込む際に、アルミニウム系メタル・シード膜の形成から埋め込みに至るまで、イオン化スパッタリングにより、実行するものである。

(もっと読む)

自己組織化単分子膜形成方法、ならびに半導体素子の銅配線およびその形成方法

【課題】 ボイド(void)およびシーム(seam)の発生を防止することができる自己組織化単分子膜形成方法、ならびに半導体素子の銅配線およびその形成方法を提供する。

【解決手段】 半導体素子の銅配線形成方法は、半導体基板の上に配線形成領域を有する層間絶縁膜を形成する工程と、前記配線形成領域表面を含む層間絶縁膜上に自己組織化単分子膜(Self Assembled Monolayer)を形成する工程と、前記自己組織化単分子膜の表面に触媒粒子を吸着させる工程と、前記触媒粒子が吸着された自己組織化単分子膜上に無電解メッキ法で銅シード膜を形成する工程と、前記銅シード膜上に前記配線形成領域を埋め立てるように銅膜を形成する工程とを含む。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

半導体ウェーハの薄膜を堆積および平坦化する装置

【課題】半導体ウェーハの堆積および平坦化に関し、特に、局所堆積を使用して薄膜をより効果的に堆積させると共に、局所平坦化を可能にする装置および手法を提供する。

【解決手段】ウェーハ104の表面に金属層108を堆積させる電気メッキ装置100が提供される。一例においては、陽極として帯電可能な近接ヘッド102を、ウェーハ104の表面に極めて近接して配置する。メッキ流体116を、前記ウェーハ104と前記近接ヘッド102との間に提供し、局所金属メッキ108を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体層の一方の面に基板が形成された半導体素子について、特性の劣化を避けながら容易に形成することを実現する。

【解決手段】半導体素子1は、半導体材料からなる半導体層5と、半導体層5の一方の面に接合された金属層18とを備え、金属層18は、磁性体層16を有し、磁性体層16は、少なくともFe及びNiを含む合金からなる層を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線間リーク電流の増加を抑制できる配線構造を備えた半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に設けられ、シリコン、酸素、炭素および水素を含む、配線溝5が形成された絶縁膜3,4と、配線溝5内に設けられた金属配線8と、金属配線8の上面に選択的に形成されたメタルキャップ10とを具備してなり、絶縁膜4は、その表面を含む第1の領域と、第1の領域下の第2の領域とを備えており、前記第1の領域の炭素濃度は前記表面から深くなるに従って減少し、前記第2の領域内の炭素濃度は、前記第1の領域との界面から一定距離の深さまでは深くなるに従って減少し、前記一定の距離減を越えると深くなるに従って増加し、前記表面における炭素濃度を超えることを特徴とする。

(もっと読む)

半導体ウェーハの薄膜を堆積および平坦化する装置

【課題】半導体ウェーハの堆積および平坦化に関し、特に、局所堆積を使用して薄膜をより効果的に堆積させると共に、局所平坦化を可能にする装置および手法を提供する。

【解決手段】陽極として帯電可能な近接ヘッド102を、ウェーハ104の表面に極めて近接して配置する。メッキ流体を、前記ウェーハと前記近接ヘッドとの間に提供し、局所金属メッキを形成する。近接ヘッドが方向120でウェーハ全体を進む際に、シード層106上に堆積層108が形成される。堆積層は、近接ヘッドとシード層との間に定められたメニスカス116に含有される電解質110によって促進される電気化学反応を介して形成される。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、Ru膜上にCVD法によりCu膜を成膜するにあたり、チャンバー1の壁部の温度を、副生成物であるCu(hfac)2の蒸気圧が成膜処理時のチャンバー1内の圧力と等しくなる温度以上で成膜原料であるCu(hfac)TMVSの分解温度未満に制御する。

(もっと読む)

CVD−Ru膜の形成方法および半導体装置の製造方法

【課題】Cuの濡れ性が良好なCVD−Ru膜の形成方法を提供すること。

【解決手段】有機金属化合物を含む成膜原料を用いてCVDにより基板上にRu膜を成膜する工程と、前記Ru膜が成膜された基板に対し、水素含有雰囲気でのアニールを行う工程とによりCVD−Ru膜を形成する。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】表面性状が良好でかつ高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にウエハWを収容し、チャンバー1内にカルボン酸第1銅錯体、例えばCH3COOCuとこれを還元する還元剤とを気相状態で導入して、ウエハW上にCVD法によりCu膜を成膜する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】カーバイド化する金属を用いて、あるいはカーバイド化する金属とシリサイド化する金属とを組み合わせてオーミック電極を形成する際に、より低抵抗化ができるSiC半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bに、カーバイドを生成する金属を含む金属薄膜50を形成する金属薄膜形成工程を実施したのち、金属薄膜50とSiCに含まれるCとを反応させてカーバイド層70を形成する電極形成工程を実施し、その後、カーバイド層70の表面に生じたシリコン粒子やシリコンの酸化物を除去する除去工程を行うことにより、カーバイド層70を含むドレイン電極11を形成する。

(もっと読む)

141 - 160 / 613

[ Back to top ]