Fターム[4M104DD52]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 塗布、又は液体からの析出 (2,321) | 電解メッキ (613)

Fターム[4M104DD52]に分類される特許

81 - 100 / 613

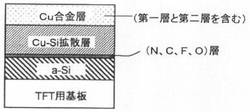

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

パターン形成体の製造方法、機能性素子の製造方法および半導体素子の製造方法

【課題】本発明は、高精細なパターニングが可能なパターン形成体の効率的な製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に形成され、表面が疎水性を示す疎水性層上にフォトレジストパターンを形成するフォトレジストパターン形成工程と、上記フォトレジストパターンが形成された上記疎水性層の表面にエネルギーを照射して親水化し、親水性領域を形成する親水化工程と、上記フォトレジストパターンを剥離し、上記疎水性層表面に、上記親水性領域と上記親水化工程にて上記フォトレジストパターンで覆われていた疎水性領域とがパターン状に形成された親疎水パターンを形成するフォトレジストパターン剥離工程とを有することを特徴とするパターン形成体の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーションの影響を低減できるCu配線を備えた半導体装置

及びその製造方法を目的とする。

【解決手段】

Cu配線10を備える半導体装置1において、

Cu配線10の断面構造は、側部及び下部をバリアメタル20に接し、上部を絶縁膜3

0に接し、絶縁膜30に接するCu配線10の上部のグレインサイズが、Cu配線10の

中央部のグレインサイズより小さ。さらに、バリアメタルに接するCu配線10の側部及

び下部のグレインサイズが、Cu配線10の中央部のグレインサイズより小さい。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、簡素な製造工程でありながら、ボイドを発生させずにトランジスタセルの高密度化を実現する半導体装置の製造方法を提供することを目的とする。

【解決手段】半導体層60にトレンチ型のゲート90が形成され、該ゲート90の両側に拡散層50が形成されたトランジスタセルを複数含むセル部61と、該セル部61を囲むガードリング部62とを有する半導体装置の製造方法であって、

前記ゲート90及び前記拡散層50が形成された前記半導体層60の表面に、層間絶縁膜120を形成する工程と、

前記セル部61に形成された前記層間絶縁膜120を、エッチバックにより薄膜化する工程と、

前記層間絶縁膜120の前記拡散層50上の位置に、孔状又は溝状のコンタクト部130を形成する工程と、

前記層間絶縁膜120上に、金属膜140を形成する工程と、を含むことを特徴とする。

(もっと読む)

貫通孔配線基板の製造方法

【課題】めっき反応速度を調整することでめっき未着を防ぐことが可能な貫通孔配線基板の製造方法を提供することである。

【解決手段】微小デバイスを構成する貫通孔配線基板の製造方法であって、基板40の両表面を貫通する貫通孔41を形成する工程と、貫通孔41の少なくとも内表面にNiめっきを成長させる工程と、を備え、貫通孔41の少なくとも内表面にNiめっきを成長させる工程では、Niめっきの析出レートを50nm/min未満にしてめっきを成長させる。

(もっと読む)

半導体装置の製造方法

【課題】ボイド、ディッシング、及びエロージョンの発生を抑制することのできる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に幅の異なる複数の開口部36,37を形成し、次いで、絶縁膜の上面、及び幅の異なる複数の開口部内にシード層38を形成し、次いで、第1の成長速度により、シード層の表面を覆う第1のめっき膜71を形成し、次いで、第1の成長速度よりも速く、かつボイドを生じさせない第2の成長速度により、第1のめっき膜の表面に第2のめっき膜72を形成し、次いで、第2の成長速度よりも速い第3の成長速度により、第2のめっき膜上に第3のめっき膜73を形成し、その後、シード層及び第1乃至第3のめっき膜のうち、絶縁膜の上面よりも上方に形成された部分を研磨により除去することで、開口部内に少なくとも第1及び第2のめっき膜よりなる導電部を形成する。

(もっと読む)

薄膜電極、及びその製造方法

【課題】実効キャリアー濃度が増加し、物質間のエネルギーバンドギャップ調節によりショットキー障壁が減少し、高い透過率を有する、優れた電気的、光学的、熱的及び構造的特性を有する新概念のオーミック接触システムを提供する。

【解決手段】発光ダイオード又はレーザーダイオードにおいてオーミック接触を形成するための薄膜電極において、p型窒化ガリウム層上に積層され、Ni−X固溶体を含有する第1電極層と、前記第1電極層上に積層され、Au、Pt、Pd、Ni、Ru、Rh、Re、C、Cu、及びIrからなる群から選択される少なくとも1種以上の元素を含有する第2電極層と、を含むことを特徴とする、薄膜電極である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、電極表面を平坦化した高い信頼性を有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】n形ベース層2と、n形ベース層2の表面に設けられたp形ベース領域3と、p形ベース領域3の表面に選択的に設けられたn形エミッタ領域4と、p形ベース領域3およびn形エミッタ領域4とゲート絶縁膜を介して対向するゲート電極5と、p形ベース領域3およびn形エミッタ領域4に電気的に接続されたエミッタ電極21と、エミッタ電極21の表面に形成された凹部31を埋め込んだ絶縁部材25と、エミッタ電極21と絶縁部材25との上に設けられたエミッタ電極23と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】デバイス特性を維持し、ゲートリーク電流を低減できる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】本発明に係る電界効果トランジスタ100は、III−V族窒化物半導体層構造と、半導体層構造上に離間して形成されたソース電極105及びドレイン電極106と、ソース電極105及びドレイン電極106の間に形成されたゲート電極108と、ソース電極105上及びドレイン電極106上に形成された電極保護膜107と、半導体層構造上に、ソース電極105、ドレイン電極106、ゲート電極108及び電極保護膜107の上面の少なくとも一部を覆うように形成され、半導体層構造を保護する第1のパッシベーション膜109を備え、第1のパッシベーション膜109は、所定の材料に対して化学的に活性であり、電極保護膜107は、所定の材料に対して化学的に不活性な金属である。

(もっと読む)

半導体素子の製造方法

【課題】ドリフト領域、ベース領域およびソース・エミッタ領域からなる寄生素子による影響をなくすことができ、また、オン電圧が増大することを防止することができる半導体素子の製造方法を提供すること。

【解決手段】半導体基板のおもて面に、ベース領域を貫通し、ドリフト領域1まで達するトレンチ3を形成する。ついで、ゲート絶縁膜4を介して、トレンチ3の内部に、ベース領域2の表面と同じ高さにまで達しないようにゲート電極5を埋め込み、第2凹部を形成する。ついで、第2凹部の内部に埋め込むように層間絶縁膜7を形成する。ついで、エッチバックを行い、ゲート電極5の表面にのみ層間絶縁膜7を残す。そして、エッチングによって、ベース領域2の表面がゲート電極5と層間絶縁膜7との界面より低い位置になるまで、ベース領域2の表面層を除去し、第1凹部6を形成する。ついで、第1凹部6の内部にソース電極8を埋め込む。

(もっと読む)

表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】表示装置の形成方法は、基板上に下地絶縁層を設け、その層上に配線パターンに沿った第1の銅拡散防止層を設ける。次に、その第1の銅拡散防止層上面に第1の銅拡散防止層の幅より僅かに狭い銅配線層を積層し、銅配線層の全表面を覆うように、第2の金属拡散防止層を設ける方法である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

電気銅メッキ用の含リン銅アノード電極、その製造方法および電気銅メッキ方法

【課題】アノードスライムの発生およびメッキ欠陥の発生を抑えた半導体ウエハ等の電気銅メッキ用の含リン銅アノード電極、該含リン銅アノード電極の製造方法およびこの含リン銅アノード電極を用いた電気銅メッキ方法を提供する。

【解決手段】リン含有量が0.01〜0.08質量%である電気銅メッキ用の含リン銅アノード電極において、該アノード電極は熱処理により、その表面の残留歪みが0.05%以下とされ、該アノード電極は炭化水素系溶剤で洗浄され、回転リングディスク電極法で測定される一価銅の検出量が電解時間300sec以上において5×10−9mol/sec以下である表面清浄度を備える電気銅メッキ用の含リン銅アノード電極とその製造方法および電気銅メッキ方法。

(もっと読む)

半導体装置、集積回路、マトリックス回路、表示素子、無線通信装置、電子機器、半導体装置の製造方法

【課題】エッチングによりソース・ドレイン電極を形成しても、有機半導体層が損傷を受けることなく、良好なオン/オフ比を示す有機半導体装置、及びその製造方法を提供することを目的とする。

【解決手段】基板1と、前記基板上に形成されたゲート電極2と、ゲート電極2及び基板1上に形成されたゲート絶縁層3と、ゲート絶縁層3上に形成されたp型有機半導体層4と、有機半導体層4上に形成された保護層5と、保護層5上に形成されたソース電極8及びドレイン電極9と、を有する半導体装置を構成する。

(もっと読む)

電子デバイスの製造方法

【課題】配線部をスパッタリングにより形成するスパッタ配線工程において、基板の外周部を、スパッタ装置内のヒーターとクランプリングとにより挟み込み、基板を保持することによる、基板の欠けの発生を抑制する。

【解決手段】緩衝層形成工程において、基板1の表面1Aに緩衝層3を形成するとともに、緩衝層3の材料と同じ材料を用いて、緩衝層形成工程の保護層形成工程を実施し、半導体装置10の製造方法を複雑化させることなく、基板1の表面1Aの外周部1B、および裏面1Dの外周部1Eに保護層4を形成するので、緩衝層形成工程の後に実施するスパッタ配線工程において、基板1の表面1Aおよび裏面1Dを直接挟み込むことなく、保護層4を介在させて挟み込み、基板1を保持することができ、基板1、特に基板1の外周部1B、および外周部1Eに欠けが発生することを抑制して、スパッタ膜11を形成することができる。

(もっと読む)

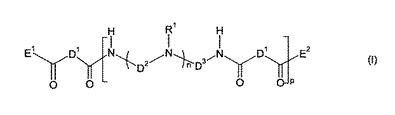

平滑化剤を含む金属電気メッキのための組成物

金属イオン供給源、及び式I

【化1】

によって表される、少なくとも1種のポリアミノアミド、又は完全な、又は部分的なプロトン化、N−四級化、又はアシル化によって得ることができる、式Iのポリアミノアミドの誘導体を含む、少なくとも1種の添加剤を含む組成物。

(もっと読む)

半導体集積回路装置の製造方法

【課題】タリウム濃度低下による金メッキの不良発生を抑止できる信頼性の高い半導体集積回路装置の製造方法を提供する。

【解決手段】半導体集積回路装置の製造方法において、非シアン系メッキ液を用いた電解金メッキ技術によって金バンプ電極を形成する工程中、メッキ液21への印加電圧をモニターすることにより、メッキ液21へのタリウムの添加量を検出して、タリウム添加濃度の減少による異常析出等のメッキ不良の発生を抑止する。

(もっと読む)

ケイ化ニッケルの向上した形成方法

【課題】半導体及び先端実装技術、例えば、ゲート電極、オーミック接触、相互接続ライン、ショットキー障壁ダイオード接触、光起電力、太陽電池及び光電子部品形成などにおける様々な目的のために使用されうるケイ化ニッケルの形成工程数を削減する形成方法を提供する。

【解決手段】ケイ素含有基体をニッケルでコーティングし、このニッケルは保護層でコーティングし、この組み合わせはケイ化ニッケルを形成するのに充分な温度に加熱される。このケイ化ニッケル形成は酸素含有環境において行われうる。

(もっと読む)

81 - 100 / 613

[ Back to top ]