Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

81 - 100 / 542

化合物半導体装置及びその製造方法

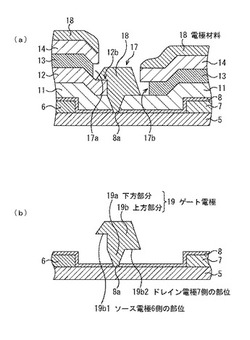

【課題】ゲート−ソース間の容量低減及びソース抵抗を低減させ、且つ耐圧向上、高出力化及び高周波化を、容易且つ確実に可能とする量産化に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極19を形成する際に、4層の電子線レジスト11〜14を用いてゲート開口17を形成し、ゲート開口17内に、キャップ層5の表面との接触面を含む幹状の下方部分19aと下方部分19aから傘状に拡がる上方部分19bとが一体形成されてなり、下方部分19aの接触面がドレイン電極7に比べてソース電極6に偏倚した位置に設けられており、上方部分19bの傘状の下端面のうちソース電極6側の部位がドレイン電極7側の部位よりもキャップ層5の表面からの高さが高いゲート電極19を形成する。

(もっと読む)

パターン画像の形成方法

【課題】有機薄膜トランジスタソース/ドレイン電極などに適する厚みが均一で高精細なパターン画像の形成方法を提供する。

【解決手段】特定の構造単位を有するポリイミド前駆体及び該ポリイミド前駆体を脱水閉環して得られるポリイミドからなる群より選ばれる少なくとも一種の重合体を含むパターン画像下層膜形成液を基板上に塗布し、乾燥、焼成することでパターン画像下層膜を得る工程と、

得られるパターン画像下層膜に紫外線を照射しパターン画像下層膜の濡れ性を変化させる工程と、

パターン画像形成液が付着したブレードと上記パターン画像下層膜とを相対的に移動させることにより、上記パターン画像下層膜の紫外線照射領域に上記パターン画像形成液を塗布させ、乾燥する工程と、

を有することを特徴とする。

(もっと読む)

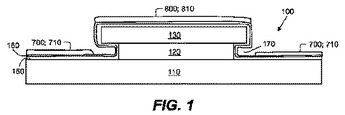

半導体装置及びその製造方法

【課題】プロセス負荷を軽減するとともに、EOTを十分に低減するための絶縁膜の薄膜化と、バンドエッジ近傍の仕事関数を有するゲート構造とを実現した半導体装置を提供する。

【解決手段】基板101の異なる領域に形成されたp型トランジスタ100a及びn型トランジスタ100bを備える半導体装置100であって、p型トランジスタ100aは、基板101上方に形成された、第1高誘電率材料からなる第1高誘電率膜106aと、第1高誘電率膜106a上方に形成された、全体が金属によりシリサイド化された第1フルシリサイド電極107aとを備え、n型トランジスタ100bは、基板101上方に形成された、第2高誘電率材料が添加された第1高誘電率材料からなる第2高誘電率膜106bと、第2高誘電率膜106b上方に形成された、全体が金属によりシリサイド化された第2フルシリサイド電極107bとを備える。

(もっと読む)

結晶欠陥の除去方法

【課題】エピタキシャル成長法により堆積させたSiC層の表面から深い位置に形成された結晶欠陥でも、確実に除去することができる方法を提供する。

【解決手段】単結晶SiCからなる半導体基板1表面にエピタキシャル層2を積層させて形成したSiC基板の表面にレジスト膜12を形成し、基板裏面から紫外線を照射することで、表面のレジスト膜12を露光する。結晶欠陥11のある部分は、レジスト膜12は露光されないため、開口が形成される。その開口部内にイオン注入することで、エピタキシャル層2、半導体基板1を高抵抗化し、結晶欠陥を除去する。最後に、レジスト膜12を除去することで、半導体装置を形成することができるSiC基板が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術により倒れにくいマスクパターンを形成するNANDフラッシュメモリ等の製造方法を提供する。

【解決手段】非晶質シリコン膜21上に第1膜のシリコン酸化膜22を形成し(a)、所定のラインアンドスペースのパターンに加工して中間パターン23を形成する(b)。中間パターン23は、パターン部23aを有するとともに、パターン部23aの間に残存部23bを残してた状態で形成される。中間パターン23をスリミング処理し、非晶質シリコン膜21上に芯材パターン24を形成する(c)。残存部23bは除去される。芯材パターン24上に第2膜のシリコン窒化膜を形成し、エッチバック処理で側壁パターンを形成し、芯材パターン24を除去してマスクパターンを得る。マスクパターンは、段差のない非晶質シリコン膜21上に形成されるので応力差に起因した倒れの発生を抑制できる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた高性能な半導体装置を提供する。

【解決手段】基板上に酸化物半導体層を形成し、酸化物半導体層上に第1の導電層を形成し、第1の導電層上に第2の導電層を形成し、第2の導電層をエッチングすることで、第1のパターンを形成し、第1のパターンを酸化することにより膨張させ、膨張後の第1のパターンをマスクとして第1の導電層をエッチングすることで、ソース電極及びドレイン電極となる第2のパターンを形成し、膨張後の第1のパターン及び第2のパターン及び酸化物半導体層を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する。

(もっと読む)

トランジスタ及びその作製方法

【課題】スイッチング特性が良好で、且つ信頼性が高いトランジスタを提供する。

【解決手段】例えば、ボトムゲートトップコンタクト構造のトランジスタを作製するに際して、第1の配線層を形成し、該第1の配線層を覆って第1の絶縁膜を形成し、該第1の絶縁膜上に半導体層を形成し、該半導体層上に導電膜を形成し、該導電膜に少なくとも2段階のエッチングを行って第2の配線層を離間させて形成し、前記2段階のエッチングが、少なくとも前記導電膜に対するエッチングレートが前記半導体層に対するエッチングレートより高い条件により行う第1のエッチング工程と、前記導電膜及び前記半導体層に対するエッチングレートが、前記第1のエッチング工程よりも高い条件により行う第2のエッチング工程と、を有する方法によりトランジスタを作製する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

MEMS及びMEMSの製造方法

【課題】回路構成の設計自由度の高いMEMS及びMEMSの製造方法を提供する。

【解決手段】基板10と、基板10の一方の面側に設けられる第1半導体部21と、基板10の一方の面側に設けられる振動子31と、を備えるMEMSにおいて、第1半導体部21の側面側に設けられ、かつ基板表面に対して略垂直な第1面21aと、振動子31の側面側に設けられ、かつ基板表面に平行な方向において第1面21aと対向する第2面31aが設けられると共に、第2面31a側の表層部分は第1面21a側をゲート電極として電圧が印加された際にチャネルとなることで、第1半導体部21における第1面21aを含む部分と振動子31における第2面31aを含む部分とで電界効果トランジスタが構成されることを特徴とする。

(もっと読む)

半導体装置及び電子機器

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体回路パターンの形成方法

【課題】スループットを短縮し、所望の回路パターンを形成することが可能な半導体回路パターンの形成方法を提供する。

【解決手段】半導体基板上に被エッチング膜を形成し、この被エッチング膜上に現像液溶解性膜を形成する。次に、現像液溶解性膜上にフォトレジスト膜を形成し、フォトマスクを介してフォトレジスト膜を露光する。さらに、現像液を用いてフォトレジスト膜を現像する。この工程では、フォトレジストパターンの下側の現像液溶解性膜を、アンダーカット状の残存部分を残すように溶解させる。次に、フォトレジスト膜を覆うように耐エッチング膜を形成したのち、フォトレジスト膜を除去することにより、被エッチング膜上に、フォトレジスト膜の開口部に対応する耐エッチング膜のパターンを形成するリフトオフ工程を行う。その後、現像液溶解性膜と耐エッチング膜とをマスクとして、被エッチング膜をエッチングする。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

81 - 100 / 542

[ Back to top ]