Fターム[4M104EE02]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極下 (1,572)

Fターム[4M104EE02]の下位に属するFターム

ゲート絶縁膜 (1,401)

Fターム[4M104EE02]に分類される特許

141 - 160 / 171

半導体素子

【課題】電極または金属配線と所望の絶縁膜とを密着でき、所望の低リーク電流特性および高耐圧特性を得ることができること。

【解決手段】この発明にかかるHEMT100は、基板1の上部に形成された化合物半導体層の電子供給層5の上部に、ソース電極6とゲート電極7とドレイン電極8と絶縁膜9,10とを有する。ソース電極6、ゲート電極7、およびドレイン電極8と絶縁膜10との各接合界面には窒化物系の接合膜11a,11d,11cが形成され、ゲート電極7と絶縁膜9との接合界面には窒化物系の接合膜11bが形成される。接合膜11a,11d,11cは、ソース電極6、ゲート電極7、およびドレイン電極8と絶縁膜10とをそれぞれ接合する。接合膜11bは、ゲート電極7と絶縁膜9とを接合する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜に高誘電率膜を使用し、ゲート電極に金属を含む導体膜を使用するpチャネル型MISFETにおいて、生産性向上を図ることができる技術を提供することにある。そして、金属を含む導体膜の仕事関数値が酸化シリコン膜に接するとした場合にシリコンの価電子帯近傍の値から離れたものであっても、pチャネル型MISFETのしきい値電圧を下げることができる技術を提供する。

【解決手段】半導体基板1上に形成されたpチャネル型MISFETQ1は、酸化ハフニウム膜よりなるゲート絶縁膜10を有し、このゲート絶縁膜10上に、酸化アルミニウム膜よりなる金属酸化物膜11を有する。そして、金属酸化物膜11上に窒化タンタル膜よりなるゲート電極12を有している。ここで、金属酸化物膜11は、ゲート電極12の仕事関数値をシフトする機能を有している。

(もっと読む)

半導体デバイス及びその製造方法

【課題】樹脂層と電極パッドとの密着性が向上された半導体デバイス及びその製造方法を提供する。

【解決手段】第1実施形態に係る半導体デバイスの製造方法は、半導体素子2上に設けられシリコン原子を含む樹脂層4aの表面4asを、酸素原子を含むガスとフッ素原子を含むガスとの混合ガスから生成されたプラズマP1によって処理することにより、酸化膜6aを形成する第1のプラズマ処理工程と、酸化膜6a上に金属からなる電極パッド8を形成する電極パッド形成工程とを含む。

(もっと読む)

炭化珪素半導体素子の製造方法

【課題】種々のポリタイプの種々の面方位の面を主面とするSiCウェハーを用いて、理論耐圧を有するトレンチゲート型の半導体素子を作製すること。

【解決手段】SiC基板21にトレンチを形成し、このトレンチの底にSiO2膜29を埋め込む。トレンチ底のSiO2膜29の厚さをtox[μm]とし、素子の絶縁耐圧をBV[kV]とすると、4H−SiC(0001)Si面を主面とするSiC基板を用いる場合には、toxが[−0.04BV2+0.4476BV+0.3996]よりも大きくなるようにする。SiC基板のポリタイプおよび主面の面方位に応じて、所定の関係式から導かれる値よりもtoxを大きくする。

(もっと読む)

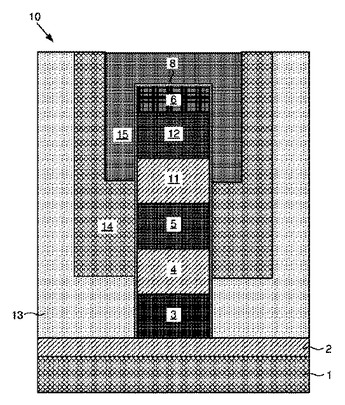

MOSデバイスおよびMOSデバイスの製造方法

本発明は、多数の積重された半導体領域を有する突起部またはフィン構造を備える三次元積層フィン型金属酸化物半導体(SF−MOS)デバイスを提供するもので、第2半導体領域が分離領域によって第1半導体領域から分離されている。ゲート分離層が少なくとも突起部の側壁に延在し、ゲート電極がゲート分離層に延在する。ゲート電極は複数のゲート領域を備え、各ゲート領域が他の半導体領域にわたって延在する。これにより、各ゲート領域が他の半導体領域の伝導チャネルに影響を与え、その結果SF−MOSデバイスの性能を最適化し得る他の自由度を付加する。本発明は、さらに本発明に係るSF−MOSデバイスを製造する方法を提供する。  (もっと読む)

(もっと読む)

高速回復整流器構造体の装置および方法

高速回復整流器構造体の装置および方法。具体的には構造体は第1のドーパントの基板(120)を含む。第1のドーパントが低濃度ドープされた第1のエピタキシャル層(140)が基板に結合されている。第1の金属層(190)が第1のエピタキシャル層に結合されている。複数のトレンチ(175)が第1のエピタキシャル層内に窪んでおり、その各々が金属層と結合している。装置は各々第2のドーパント型がドープされた複数のウェルも含み、各ウェルは対応するトレンチの下に且つ隣接して形成されている。複数の酸化物層(170)が対応するトレンチの壁および底部上に形成されている。第1のドーパントがドープされた複数のチャネル領域が、2つの対応するウェル間の第1のエピタキシャル層内に形成されている。複数のチャネル領域(150)の各々は第1のエピタキシャル層より高濃度に第1のドーパントがドープされている。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】Fin型トランジスタの金属ゲート電極を高抵抗化させることなく、トランジスタを正常に動作させることができる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、半導体材料から成り、上面が保護膜40で被覆されたFin30を絶縁層20上に形成し、Finの側面にゲート絶縁膜50を形成し、Finを被覆するようにゲート電極材料60を堆積し、ゲート電極材料を平坦化し、ゲート電極材料を加工することによってゲート電極62を形成し、ゲート電極を被覆するように層間絶縁膜90を堆積し、ゲート電極の上面を露出させ、ゲート電極の上面上に金属110を堆積し、ゲート電極と金属とを反応させることによってゲート電極をシリサイド化し、金属のうち未反応の金属を除去することによって、保護膜の上面上に溝115が形成され、溝に導電体120を充填することを具備する。

(もっと読む)

スタンプ及びスタンプ製造方法、ナノパターン形成方法、並びにそれを利用した薄膜トランジスタの製造方法及び液晶表示装置の製造方法

【課題】スタンプ製造方法、それを利用した薄膜トランジスタ及び液晶表示装置の製造方法を提供する。

【解決手段】本発明は、基板との接触性が向上したスタンプ(Stamp)の製造方法を提供し、前記スタンプを利用して、基板上に帯電された領域を作った後に、前記帯電領域の電荷と反対電荷に帯電されたナノ物質を塗布又はメッキさせて、セルフアセンブリ(self−assembled)を介して自己組織化単分子膜(SAM;self−assembled monolayer)を形成することによって、精密なナノパターンを有する薄膜トランジスタ及び液晶表示装置の製造方法を提供し、これによって素子の性能を向上させることができる。

(もっと読む)

半導体デバイスの製造方法及びかかる方法によって得られる半導体デバイス

本発明は、基板(11)と、少なくとも1つの半導体素子(E)を備える半導体本体(12)とを有する半導体デバイス(10)の製造方法であって、この半導体本体(12)の表面上にメサ型半導体領域(1)が形成され、メサ型半導体領域(1)の頂部上での厚みがメサ型半導体領域(1)に隣接する領域(3)における厚みよりも小さな絶縁層(2)が、このメサ型半導体領域を覆って堆積され、次いで、メサ型半導体領域(1)の上側がなくなるように、メサ型半導体領域(1)の頂部の絶縁層(2)の一部を除去した後、メサ型半導体領域(1)に接触する導電膜(4)を、得られた構造を覆って堆積する方法に関する。本発明によれば、絶縁層(2)は、高密度プラズマ堆積プロセスを用いて堆積される。このような処理は、特に、例えばナノワイヤ形成のような小さなメサ型領域(1)を有するデバイスの製造方法に適している。好ましくは、絶縁層(2)の堆積前に、薄い更なる絶縁層(5)を、他の共形的堆積プロセスを用いて堆積する。  (もっと読む)

(もっと読む)

膜パターンの形成方法、デバイスの製造方法、デバイス、電気光学装置、及び電子機器

【課題】基板に対する膜パターンの密着力を向上し、膜パターンを良好に形成することが

できる膜パターンの形成方法を提供する。

【解決手段】機能液を基板上に供給して膜パターンを形成する際、基板と膜パターンとの

密着力を向上させるための中間層を基板上に形成する工程と、中間層上に機能液を供給す

ることによって膜パターンを形成する工程とを経て形成する。中間層はシロキサン結合を

主鎖とした無機材料を含む。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物基板裏面とそこに形成される電極との間における、コンタクト抵抗の低減および安定性の向上することが可能な半導体装置及びその製造方法を提供する。

【解決手段】窒化物半導体装置は、半導体素子が形成されるn型GaN基板1と、当該GaN基板1の裏面に形成された金属電極であるn電極10とを備える。GaN基板1とn電極10との間には、窒化物半導体以外の材料であってシリコンを含むものから成る接続層20が形成される。

(もっと読む)

平面電子表示装置及びその製造方法

【課題】Cuに添加する添加元素が、Cu部材と接触するガス雰囲気又は固体に含まれる酸素と優先的に反応してCuの酸化を抑止する酸化被膜を形成することができる高導電率の配線、電極等を備える平面電子表示装置を提供する。

【解決手段】基板上にマトリックス状に交叉する電極線17、18と、その交点に配置された液晶画素20と、外部の駆動回路に接続された端子電極とを有するアクティブマトリックス方式の液晶表示装置において、電極線17、18、電極、配線層、端子電極のうちの少なくとも一つを銅を主成分とし、基板との界面に銅に添加した添加元素の酸化物層を形成する銅合金で形成する。この添加元素は、酸化物形成自由エネルギーがCuより小さく、Cu中における拡散係数がCuの自己拡散係数より大きく、Cu中における1at.%当たりの電気抵抗上昇率が5μΩ・cm以下であり、Cu中における活量係数γが、活量係数γ>1の関係を満足する。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な薄膜トランジスタ及びその作製技術を提供することを目的とする。また、薄膜トランジスタを構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】薄膜トランジスタが有する配線や電極パターンは、第1の領域及び第2の領域を有する絶縁表面上に設けられた配線層と、配線層に接する電極層とを有し、前記配線層は前記第2の領域に設けられ、電極層は第1の領域に設けられ、電極層及び配線層に対するぬれ性は、前記第1の領域より前記第2の領域が高い領域に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】フルシリサイドゲート又はメタルゲートを用いたCMOSトランジスタ構造であって、特にフェルミ・レベル・ピニング現象の原因となる高誘電率材料とゲート電極材料との反応を抑制して所望の仕事関数を得られるようにし、且つ均一性及び歩留まりを高くできるようにする。

【解決手段】 CMOS型の半導体装置は、Siからなる基板101の上に順次形成され、HfSiONからなるゲート絶縁膜104A及び全体がニッケルシリサイドからなるゲート電極106Bを有するn型トランジスタと、HfSiONからなるゲート絶縁膜104A及び全体がニッケルシリサイドからなるゲート電極106Dを有するp型トランジスタとを備えている。p側のゲート電極106Cの金属濃度は、n側のゲート電極106Bの金属濃度よりも高くなるように設定されている。

(もっと読む)

少数キャリアの注入が抑制される炭化シリコン接合障壁ショットキーダイオード

接合障壁ショットキー(JBS)構造内のビルトインPiNダイオードの電流伝導を阻止する一体構造が提供される。このPiNダイオードと直列に、PiNダイオードとは逆向きのショットキーダイオードを組み込むことができる。PiNダイオードとショットキーコンタクトとの間に、直列抵抗または絶縁層を形成することができる。ダイオードのドリフト領域内に配置された炭化シリコン接合障壁領域を含む炭化シリコンショットキーダイオード、およびこの炭化シリコンショットキーダイオードを製造する方法も提供される。この接合障壁領域は、ダイオードのドリフト領域内にあって第1のドーピング濃度を有する第1の炭化シリコン領域と、ドリフト領域内にあって、第1の炭化シリコン領域とショットキーダイオードのショットキーコンタクトとの間に配置された第2の炭化シリコン領域とを含む。第2の領域は、第1の炭化シリコン領域およびショットキーコンタクトと接触する。第2の炭化シリコン領域は、第1のドーピング濃度よりも低い第2のドーピング濃度を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層の表面準位によって生じる逆方向バイアス時のリーク電流を低減する半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板1の上に形成された第1の半導体層4と、第1の半導体層4の上に互いに間隔をおいて形成されたショットキー電極7及びオーミック電極8と、ショットキー電極7及びオーミック電極8を露出し且つ第1の半導体層4の上を覆うように形成された第2の半導体層5とを備えている。第2の半導体層5は、第1の半導体層4と比べてバンドギャップが大きい半導体層である。

(もっと読む)

銅配線層、銅配線層の形成方法、半導体装置、及び半導体装置の製造方法

【課題】広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な銅配線層の形成方法を提供すること。

【解決手段】基板上に銅シード層のパターンを形成する工程、及び前記銅シード層のパターン上に銅配線層を無電解めっき法で形成する工程を具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 III族窒化物半導体層とオーミック電極との間のコンタクト抵抗を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】 III族窒化物半導体層(12)と、III族窒化物半導体層(12)とオーミック接触するオーミック電極(15)とを有し、III族窒化物半導体層(12)はAlxGa1−xNで表される半導体からなり、オーミック電極(15)は、Gd、Eu、Sm及びSrから選ばれる少なくとも1種を含む第1電極層(13)を有する半導体装置(1)とする。

(もっと読む)

差異的酸化膜厚さを有するトレンチショットキーバリアダイオード

トレンチ内の酸化膜が差異的厚さを有するトレンチショットキーダイオード用の製造プロセスは、第1窒化層を基板表面に形成する工程と、その後に、場合により終端トレンチを含む、複数のトレンチを基板に形成する工程とを含む。犠牲酸化層の形成および除去に続いて、トレンチの側壁および底面が酸化される。次に、第2窒化層が基板に施され、第2窒化層がトレンチ側壁の酸化層を覆うが、トレンチ底面の酸化層を露出させるようにエッチングされる。次に、トレンチ底面は再び酸化され、次に、残りの第2窒化層は側壁から除去されて、厚さが変化する酸化層が各トレンチの側壁および底面に形成される。次に、トレンチはP型多結晶シリコンで充填され、第1窒化層は除去され、ショットキーバリア金属が、基板表面に施される。 (もっと読む)

配線装置

【課題】レーザ光によって加工を行う際に、被加工部分以外の部分が悪影響を受けない配線装置を提供する。

【解決手段】基板301上に、シリコン酸化膜からなる下部絶縁層302と、Alからなる下部配線層303と、ポリイミドからなる上部絶縁層304と、Alからなる上部配線層306とを有する。上記下部配線層303と、上部配線層306とが、接続配線308によって電気的に接続されている。下部絶縁層302は基板301に比べ熱伝導率が高く上部絶縁層304の開口形成時にレーザによる下部配線層303に溜った熱を放熱し下部配線層303の溶解や剥がれを防ぐ。

(もっと読む)

141 - 160 / 171

[ Back to top ]