Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

961 - 980 / 992

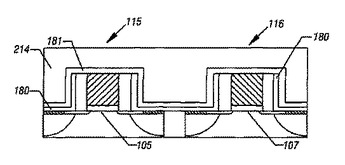

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

陥没トレンチを用いた表面側ドレインを有する半導体電力素子

本発明による半導体電力素子は、第1導電型を有する基板と、該第1導電型を有し且つ該基板の表面を覆ってこれと接触するエピタキシャル層とを含む。第1トレンチが該エピタキシャル層の内部に伸張してそこで終端する。陥没トレンチが該エピタキシャル層の表面から伸張し該エピタキシャル層を通って該基板の内部で終端する。該陥没トレンチは、該第1トレンチの横に間隔をおいて設けられ、該第1トレンチよりも広く且つ深く伸張する。該陥没トレンチは自身の側壁に沿ってのみ絶縁体によって裏打ちされることで、該陥没トレンチを充填する導電材料が該基板との電気的接続を該陥没トレンチの底部に沿ってなすと共に、相互接続層との電気的接触を該陥没トレンチの表面側に沿ってなす。  (もっと読む)

(もっと読む)

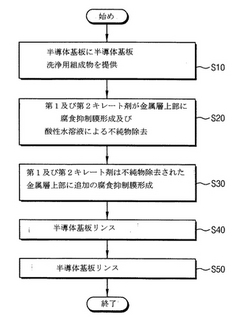

半導体基板洗浄用組成物を用いた半導体装置製造方法

【課題】不純物の除去力を向上させながらも、金属層の損傷を最小化することができる半導体基板洗浄用組成物を用いた半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法において、半導体基板上に金属を含む構造物パターン形成し酸性水溶液78ないし99.98質量%、第1キレート剤0.01ないし11質量%を含む半導体基板洗浄用組成物を、半導体基板に適用して構造物パターンの不純物が覆っていない第1表面部位上に第1腐食抑制膜を形成し、構造物パターンの不純物が覆っている第2表面部位上の不純物を除去する。

(もっと読む)

配線基板、及び半導体装置、並びにその作製方法

【課題】少ない工程数で大面積基板に微細な形状を有する配線を形成する方法、及びそれにより形成された配線基板を提供する。また、少ない工程数及び原料の削減により、コスト削減及びスループットの向上が可能であり、かつ微細構造の半導体素子を有する半導体装置、及びその作製方法を提供する。

【解決手段】金属粒子と有機樹脂とで形成される組成物102をインクジェット法で基板101上に描画し、それにレーザ光103を照射し、金属粒子の一部を焼成して、配線、電極等に代表される導電層105を基板上に形成することを特徴とする。また、上記焼成された導電層を配線又は電極として有する半導体装置を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 サイドウォールの酸化膜・シリコン界面の窒化による界面準位の発生を抑制することにより、トランジスタの性能劣化を防止する。

【解決手段】 基板101上に形成されたゲート電極104と、ゲート電極104の側壁に形成された第1のサイドウォールである酸化膜105と第2のサイドウォールである窒化膜106と、ゲート電極104の側方に位置する基板101の領域の中に形成された低濃度不純物拡散領域107と高濃度不純物拡散領域109とを備え、第1のサイドウォールである酸化膜105と低濃度不純物拡散領域107との界面における窒素濃度が1×1020cm-3以下である。これにより低濃度不純物拡散領域107と第1のサイドウォールである酸化膜105の界面における界面準位の発生量が少なくなり、界面準位による低濃度不純物拡散領域への空乏層の形成を抑制し、トランジスタ性能の劣化を防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】 低コストで歩留り良く製造でき、ゲート絶縁膜の信頼性が高く、しきい値電圧のばらつきが小さい半導体装置及びその製造方法を提供する。

【解決手段】 金属シリサイド膜4は、ゲート絶縁膜3上にアモルファスSi膜、金属膜及びSi膜5を順次形成し、熱処理によって金属膜をシリサイド化することにより得られる。金属膜の上にSi膜5を形成し、ゲート電極のゲート絶縁膜3側からのシリサイド化反応により金属シリサイド膜4を形成するため、不純物イオンがゲート電極とゲート絶縁膜3との界面に濃縮することが無い。これにより、不純物イオンのゲート絶縁膜3中又はチャネル領域への拡散を抑制し、MISFETのしきい値のばらつきを低減できる。また、ゲート絶縁膜3とゲート電極との界面における不純物の偏析を抑制し、ゲート電極の剥離を防止することができるため、ゲート絶縁膜3の信頼性が高い。

(もっと読む)

半導体装置およびその製造方法

【課題】 メタルゲート及びhigh-kゲート絶縁膜を有するCMOSにおいて、nMOS及びpMOSトランジスタの低しきい値化を実現する。

【解決手段】 n型MISFET形成領域11のゲート絶縁膜3aはHfO2膜であり、メタルゲート電極4aは、TiN膜と、ゲート絶縁膜との界面に生成されたにゲート電極に含まれるIV族遷移金属と酸素を含むがシリコンは含まない界面層とからなり、その仕事関数はn型MISFETのゲート電極材料に適した4.0〜4.2eVである。p型MISFET形成領域12のゲート絶縁膜3bはHfSiO2/HfO2であり、メタルゲート電極4bはTiNと、ゲート絶縁膜との界面に形成されたにゲート電極に含まれるIV族遷移金属と酸素および金属的シリコン(Si0)からなる界面層とからなり、その仕事関数は、p型MISFETのゲート電極材料に適した4.9eVとなっている。

(もっと読む)

ナノクラスタ電荷蓄積デバイスの形成方法

一実施形態では、ナノクラスタ電荷蓄積デバイスを形成する方法が提供される。半導体装置(10)の第1の領域(26および30)が1つまたは複数の非電荷蓄積デバイスを配置するために特定される。この半導体装置の第2の領域(28)が1つまたは複数の電荷蓄積デバイスを配置するために特定される。この1つまたは複数の非電荷蓄積デバイスのゲート絶縁体として使用されるゲート酸化物(22)がこの半導体装置の第1の領域(26および30)中に形成され、引き続きナノクラスタ電荷蓄積層がこの半導体装置の第2の領域(28)中に形成される。  (もっと読む)

(もっと読む)

High−k誘電材料をエッチングするための方法及びシステム

【課題】high−k(高誘電率)誘電材料をエッチングするための方法及びシステム

【解決手段】本発明のある実施形態では、エッチ反応剤が、high−k層と反応したときに揮発性エッチ製品を形成するために利用される。代わりに、high−k層はパターン化されたフォトレジストまたはハードマスクに従って異方エッチングすることができ、中性原子のハイパーサーマルビームがhigh−k層とのエッチ反応剤の反応を助けるために使用される。代わりに、中性原子のハイパーサーマルビームまたはプラズマ処理はhigh−k層を修正し、その後、該修正されたhigh−k層と反応するエッチ反応剤を活用して該修正されたhigh−k層をエッチングするために使用することができる。

(もっと読む)

ドープ窒化膜、ドープ酸化膜、およびその他のドープ膜

【課題】一般に、半導体デバイスの製造に使用される被膜、特に窒化被膜および酸化被膜を提供すること。

【解決手段】窒化シリコン、酸化シリコン、酸窒化シリコン、または炭化シリコン被膜の形成中、少なくとも1つの非シリコン前駆体(ゲルマニウム前駆体や炭素前駆体など)を添加することによって、堆積速度が改善され、または被膜の応力を調整するなどこの被膜の特性を調整することが可能になり、あるいはその両方が可能になる。また、ドープ型酸化シリコンまたはドープ型窒化シリコンまたはその他のドープ型構造では、ドーパントが存在することを利用して、このドーパントに関連する信号(目印)をエッチング・ストップとして測定することができ、またはその他の場合にはエッチング中の制御を実現することができる。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】 不純物のプロファイルを精度よく制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体領域1に不純物元素のイオンを注入する工程と、半導体領域に、所定元素としてIV族の元素又は不純物元素と同一導電型であって不純物元素よりも質量数が大きい元素のイオンを注入してアモルファス状態の結晶欠陥領域5を形成する工程と、不純物元素及び所定元素が注入された領域にフラッシュランプの光を照射してアニールを行い、アモルファス状態の結晶欠陥領域の結晶欠陥を回復させるとともに不純物元素を活性化する工程と、を備え、フラッシュランプの光を照射してアニールを行う工程を、結晶欠陥領域のアモルファス状態が維持される温度で半導体領域を予め加熱した状態で行う。

(もっと読む)

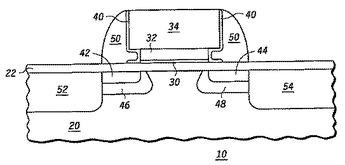

平面デュアルゲート半導体装置

デュアルゲート半導体装置の製造方法は、シリコン体(16)の第1の表面(14)の一部分上に第1のゲート(12)が形成された後であるが、前記第1の表面の反対側のシリコン体の第2の表面(44)上に第2のゲート(52)を形成する前に行われるソース及びドレインコンタクト領域(34,36)のシリサイド化を備える。第1のゲート(12)はソース及びドレインコンタクト領域がシリコンチャネル(18)に位置合わせされることを保証するマスクの働きをする。さらに、製造の早い段階でシリサイド化を行うことにより、第2のゲートの材料の選択が高温処理により制限されない。シリサイド化によるシリコン体の第2の表面での材料特性の違いがシリサイドのソースコンタクト領域とドレインコンタクト領域との間に前記第2のゲートを横方向に位置合わせされることを可能にすることが有利である。  (もっと読む)

(もっと読む)

半導体デバイス用の改良型誘電体パシベーション

半導体デバイスは、少なくとも1つの表面を含むIII族窒化物半導体材料の層と、半導体材料の電気的応答を制御するための、表面上にある制御コンタクトと、制御コンタクトに隣接する1つの表面の少なくとも一部を被覆する誘電体バリア層であって、III族窒化物のバンドギャップよりも大きなバンドギャップと、III族窒化物の導電帯からずれている導電帯とを有する、誘電体バリア層と、III族窒化物の表面の残り部分を被覆する誘電体保護層とを備えている。  (もっと読む)

(もっと読む)

使い捨てスペーサを隆起ソース/ドレイン処理に取り入れた半導体デバイスの製造方法

半導体形成プロセスでは、ゲート電極(10)を基板(108)の上に形成する。第1シリコン窒化膜スペーサ(122)をゲート電極の側壁に隣接するように形成し、そして次に、使い捨てシリコン窒化膜スペーサ(130)をオフセットスペーサに隣接するように形成する。次に、使い捨てスペーサ(130)の境界によって画定される隆起ソース/ドレイン構造(132)をエピタキシャル成長により形成する。次に、使い捨てスペーサ(130)を除去して、ゲート電極(110)の近位に位置する基板を露出させ、そしてハロイオン注入(140)及びエクステンションイオン注入(142)のようなシャロージャンクションイオン注入を、ゲート電極の近位に位置する露出基板に行なう。取り替えスペーサ(136)を、使い捨てスペーサ(130)が形成されていた領域とほぼ同じ領域に形成し、そしてソース/ドレインイオン注入(140)を行なって、ソース/ドレイン不純物分布を隆起ソース/ドレイン(132)に形成する。ゲート電極(110)は被覆窒化シリコンキャップ層(144)を含むことができ、そして第1シリコン窒化膜スペーサ(122)はキャップ層(144)とコンタクトしてポリシリコンゲート電極(110)を窒化シリコンで取り囲むことができる。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

CMOSシリサイド金属ゲート集積化

本発明は、ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。本発明の集積化方式を用いて形成される各シリサイド金属ゲートは、シリサイド金属ゲートの寸法に関わりなく、同じシリサイド金属相および実質的に同じ高さを有する。本発明は、半導体構造物の表面全体にわたってポリSiゲート高さが実質的に同じであるシリサイド接点を有するCMOS構造物を形成するさまざまな方法も提供する。

(もっと読む)

(もっと読む)

961 - 980 / 992

[ Back to top ]