Fターム[4M104FF04]の内容

Fターム[4M104FF04]に分類される特許

61 - 80 / 267

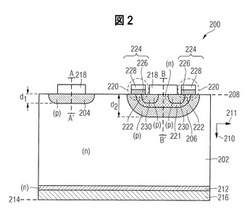

ダイオードを含む半導体装置

【課題】ダイオードを含む半導体装置において、ダイオードの逆回復挙動とオン状態特性とのトレードオフを改善する。

【解決手段】半導体装置200は陰極216と陽極218を含む。陽極は第1のp型半導体陽極領域204と第2のp型半導体陽極領域206を含む。第1のp型半導体陽極領域204は陽極接触領域218に電気的に接続される。第2のp型半導体陽極領域206は、第2のp型陽極領域と陽極接触領域218間を電気的に接続または切断するように構成された、MOSFET228等のスイッチを介し陽極接触領域218に電気的に接続される。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体8をドライエッチングして形成した平坦表面に電極を形成してもオーミック接触させることができない。

【解決手段】p型III族窒化物半導体8の電極形成範囲をドライエッチングして溝8dを形成し、その溝8dに金属20を充填して電極を形成する。p型III族窒化物半導体8のドライエッチング面は、エッチングによって生じた欠陥によってn型化しているために、平坦平面にドライエッチングしておいて電極を形成するとオーミック接触しない。溝8dを設けておくと、欠陥が少ない溝8dの側面においてp型III族窒化物半導体8と電極がオーミック接触し、半導体と電極の接触抵抗が低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】縦型トランジスタとしての機能が低下することなく、安定性の高い半導体装置を提供する。

【解決手段】活性領域T及び活性領域Tを区画する素子分離領域3が形成されて成る半導体基板1と、活性領域Tに設けられた凹部9内に形成され、上面が半導体基板1の主面からなる第1ピラー1Aと、活性領域T及び素子分離領域3に渡って形成され、第1ピラー1Aに隣接する第2ピラー2と、第1ピラー1A及び第2ピラー2の各側面を覆うように形成されたゲート電極層10と、第1ピラー1A上に形成されたエピタキシャル半導体層6と、を具備してなり、第2ピラー2が、活性領域T内において第1ピラー1Aから離間して形成された半導体凸部1Bと、素子分離領域3に埋設された埋め込み絶縁膜からなる絶縁体凸部3Aとから構成され、半導体凸部1Bの上面が埋め込み絶縁膜の一部によって被覆されていることを特徴とする。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置

【課題】ゲート抵抗の増大を抑制しつつ、外部ウェルがトレンチゲート電極によってセル領域のウェルから分断されてしまうことを抑制する。

【解決手段】埋込ゲート電極140のうち平面視でゲートコンタクト領域102と重なる方向に延伸している埋込ゲート電極142は、ゲート電極310と重ならないように、ゲート電極310の手前までしか延伸していない。また埋込ゲート電極142の相互間に位置するソースコンタクトは、図中上下方向において、埋込ゲート電極142よりも短く形成されている。そして埋込ゲート電極142のうちゲート電極310側の端部は、ゲート電極310の手前に設けられた接続用埋込電極141によって互いに接続されている。接続用埋込電極141は、半導体装置の長辺と平行な方向に延伸している。接続用埋込電極141は、埋込ゲート電極142の隣に位置する埋込ゲート電極144には接続していない。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

半導体装置およびその製造方法

【課題】低いオン抵抗を得ながら、優れた耐圧性能を持つ、縦型の半導体装置およびその製造方法を提供する。

【解決手段】開口部28はn−型GaNドリフト層4にまで届いており、開口部の壁面を覆うように位置する再成長層27と、p型GaNバリア層6と、ゲート電極Gと、ソース電極Sとを備え、チャネルが電子走行層22内の電子供給層26との界面に生じる二次元電子ガスにより形成され、p型GaNバリア層6がGaN系積層体15の表層をなし、かつソース電極Sが、再成長層27およびp型GaNバリア層6に接して位置することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】GaAsデバイスにおいて、空洞上に浮遊するGaAs層に素子形成を行うことにより、浮遊容量を抑え、高速化・低電力化を図ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板11上に形成される空洞14と、空洞14上に形成されるGaAsエピタキシャル層13と、GaAsエピタキシャル層13上に形成されるゲート電極15と、それぞれGaAsエピタキシャル層13上に形成され、隣接するゲート電極15を挟むように形成される一対のソース電極16及びドレイン電極17と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置、ショットキーバリアダイオードの特性を向上させる。

【解決手段】禁制帯幅の異なる第1膜と第2膜とが積層されたヘテロ接合部を少なくとも一つ有する積層体Hと、積層体Hと同層の積層物よりなるダミー積層体Dと、積層体Hとダミー積層体Dとの間に設けられた溝Gと、溝内部を含み積層体Hの上部からダミー積層体Dの上部まで延在するように配置され、積層体Hの第1の側壁に接するように配置され、積層体Hとの間にショットキー接続される第1電極SEと、積層体Hの第1の側壁と対向する第2の側壁に接するように配置された第2電極OHEと、で半導体装置を構成する。このように、ダミー積層体Dを残存させ、積層体Hとの間に溝Gを設け、溝内部に充填された第1電極SEによって、側壁コンタクトを実現したので、積層体Hをエッチングする際の欠陥が溝底部に発生する確率を低減でき、逆リーク電流を低減することができる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素MOSFETにおいて、炭化珪素層とゲート絶縁膜との界面に発生する界面準位を十分に低減できず、キャリアの移動度が低下する場合があった。

【解決手段】この発明に係る炭化珪素半導体装置は、炭化珪素層を有し炭化珪素層上にゲート絶縁膜を形成した基板を炉の中に導入する基板導入工程と、基板を導入した炉を加熱して一酸化窒素と窒素とを導入する加熱工程とを備え、加熱工程は、窒素を反応させてゲート絶縁膜と炭化珪素層との界面を窒化する。

(もっと読む)

半導体装置

【課題】作製プロセスに起因する特性劣化を生ぜず、ボンディングパッドの電位変化による特性変化を受け難い小型化した半導体装置を提供する。

【解決手段】半導体装置10は、アクティブ領域12と、アクティブ領域12を覆う第1の絶縁層13と、第1の絶縁層13上に形成されるフローティング導体14と、第1の絶縁層13上およびフローティング導体14上に形成される第2の絶縁層15と、第2の絶縁層17上に形成されたボンディングパッド18と、アクティブ領域12とボンディングパッド18を電気的に接続する導通ビア19,20と、を有する。

(もっと読む)

薄膜トランジスタ及びこれを用いた表示装置、並びに、薄膜トランジスタの製造方法

【課題】オフ電流を抑制するとともにオン電流を確保することができる薄膜トランジスタを提供する。

【解決手段】基板10と、基板の上方に形成されたゲート電極11及びゲート絶縁膜12と、ゲート絶縁膜を介して配置されたチャネル層13と、チャネル層に接続されたバッファ層14と、バッファ層に接続され、不純物が添加された第1コンタクト層15a(15b)と、第1コンタクト層に接続され、第1コンタクト層よりも不純物濃度が高い第2コンタクト層16a(16b)と、第2コンタクト層に接続されたソース電極17S及びドレイン電極17Dとを備える。ソース電極とドレイン電極との間におけるキャリアの移動経路は、チャネル層、バッファ層、第1コンタクト層及び第2コンタクト層を経由してキャリアが移動する第1経路と、チャネル層及び第2コンタクト層を経由してキャリアが移動する第2経路とを含む。

(もっと読む)

炭化珪素半導体装置

【課題】微細化してもソース領域およびベース領域に繋がるコンタクト領域とソース電極とのコンタクトが十分に取れるようにする。

【解決手段】コンタクトホール12aの長手方向、つまりソース電極11とn+型ソース領域4およびp+型ボディ層5とのコンタクト領域の長手方向とn+型ソース領域4およびp+型ボディ層5の長手方向も直交させる。これにより、n+型ソース領域4やp+型ボディ層5それぞれのソース電極11へのコンタクト幅をコンタクトホール12aの幅分とすることが可能となる。このため、コンタクトを広く取ることが可能となる。これにより、素子を微細化してもn+型ソース領域4やp型ベース領域3に繋がるp+型ボディ層5とソース電極11とのコンタクトが十分に取れるようにすることが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、かつ、コンタクト抵抗の増加およびオン電流の減少を防止できる半導体装置の提供。

【解決手段】ピラートランジスタTr1と、前記ピラートランジスタTr1の下部拡散層7aへ信号または電源を供給するとともに、ポリシリコン層10aからの固相拡散し、下部拡散層7aを形成することにより、前記ピラートランジスタTr1のチャネル長d1を厚みにより制御する前記ポリシリコン層10aと、を具備してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

61 - 80 / 267

[ Back to top ]