Fターム[4M104FF27]の内容

半導体の電極 (138,591) | 構造 (12,435) | コンタクト面の位置、配置 (799) | 基板の凹部 (569)

Fターム[4M104FF27]に分類される特許

41 - 60 / 569

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

GaN系化合物半導体装置

【課題】ゲート電極へのリーク電流を大幅に低減できるGaN系化合物半導体装置を提供する。

【解決手段】このGaN系HFETによれば、ゲート電極をなすTiN膜の抵抗率(Ω・μm)を24.7(Ω・μm)とした。このように、ゲート電極のショットキー電極層としてのTiN膜の抵抗率が10Ωμm以上であることによって、ゲート電極をなす金属材料TiNの抵抗率(ゲートメタル抵抗率)が10Ωμm未満である場合に比べて、ゲートリーク電流を著しく低減できる。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体装置

【課題】逆方向リーク電流および閾値電圧を低減することができる半導体装置を提供すること。

【解決手段】表面12および裏面11を有するSiCエピタキシャル層6の表面12に接するように、アノード電極27をショットキー接合させる。そして、ショットキーバリアダイオード1の閾値電圧Vthを0.3V〜0.7Vにし、定格電圧VRにおけるリーク電流Jrを1×10−9A/cm2〜1×10−4A/cm2にする。

(もっと読む)

成膜装置および成膜方法

【課題】銅めっき工程の電極に用いるCu堆積膜による貫通孔開口の閉塞状態を適切に制御できる成膜装置を提供する。

【解決手段】成膜装置100は、貫通孔が形成された基板34Bおよび銅放出源35Bを格納する真空チャンバ30と、真空チャンバ30内を所定の真空度に減圧する真空ポンプ36と、基板34Bに印加する電力を発生する電源80と、基板34Bおよび銅放出源35B間の距離の設定に用いる駆動機構と、を備える。銅放出源35Bから放出された銅材料を基板34Bの一方の主面に堆積させ、主面における貫通孔の開口を銅材料からなる堆積膜によって閉塞させるとき、堆積膜による開口の閉塞状態が、上記距離および上記電力に基づいて調整される。

(もっと読む)

半導体装置及びそれを用いた電力変換装置

【課題】低損失、高耐圧、出力電圧のdV/dtの制御が容易で、製造が容易なIGBTを提供する。

【解決手段】第1導電型の第1半導体層と、第1半導体層の表面の第2導電型の第2半導体層と、第1半導体層の表面に形成されたトレンチと、第1半導体層の表面の半導体凸部と、半導体凸部の表面形成された第3半導体層と、第3半導体層の表面の第4半導体層と、トレンチの内壁に沿って設けられたゲート絶縁層と、トレンチの内壁に沿って設けられた第1層間絶縁層と、ゲート絶縁層を介して第4半導体層に対向する第1導電層と、第1層間絶縁層の第2導電層と、第2導電層の表面を覆う第2層間絶縁層と、第3半導体層と第4半導体層の表面に形成され、前記第4半導体層に電気的に接続される第3導電層と、第3導電層と第3半導体層を接続するコンタクト部と、第2半導体層の表面に形成された第4導電層とを備え、半導体凸部の表面の一部が第1半導体層である。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

ジャンクションバリアショットキーダイオード

【課題】ジャンクションバリアショットキーダイオードの耐圧を低下させることなく、リーク電流の低減とオン電流の増大を両立したダイオードを提供する。

【解決手段】本発明は、ジャンクションバリアショットキーダイオードにおいて、pn接合を形成するp型領域の側部に存在するpn接合の傾きが、当該p型領域の底部に存在するpn接合の傾きより急峻である。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】Ge基板上に形成されたPチャネル型MISFETの第1ソースおよび第1ドレインが、Ge原子とニッケル原子との化合物、Ge原子とコバルト原子との化合物またはGe原子とニッケル原子とコバルト原子との化合物からなり、III−V族化合物半導体からなる半導体結晶層に形成されたNチャネル型MISFETの第2ソースおよび第2ドレインが、III族原子およびV族原子とニッケル原子との化合物、III族原子およびV族原子とコバルト原子との化合物、または、III族原子およびV族原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

窒化物半導体層のエッチング方法及びこれを用いた窒化物半導体装置の製造方法

【課題】高抵抗なダメージ層を形成しない窒化物半導体層のエッチング方法と、これを用いた低抵抗なオーミック電極を備える窒化物半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の窒化物半導体層のエッチング方法は、(a)窒化物半導体層に不純物イオンを注入し、その表面から所定深さまで不純物領域を形成する工程と、(b)前記不純物領域を熱処理する工程と、(c)前記不純物領域の前記表面側の所定領域をウェットエッチングで除去する工程とを備える。

(もっと読む)

半導体装置、金属膜の製造方法及び半導体装置の製造方法

【課題】高集積化することができる半導体装置、金属膜の製造方法及び半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板に形成され、ヒ素を含むヒ素拡散層と、前記ヒ素拡散層上に形成された金属膜と、を備える。前記金属膜は、タングステン、チタン、ルテニウム、ハフニウム及びタンタルからなる群より選択された少なくとも1種の金属、並びにヒ素を含む。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層とオーミック電極とのコンタクト抵抗を低減できる窒化物半導体装置を提供する。

【解決手段】Si基板10上に形成されたアンドープGaN層1,アンドープAlGaN層2と、アンドープGaN層1,アンドープAlGaN層2上に形成されたTi/Al/TiNからなるオーミック電極(ソース電極11,ドレイン電極12)とを備える。上記オーミック電極中の酸素濃度を1×1016cm−3以上かつ1×1020cm−3以下とする。

(もっと読む)

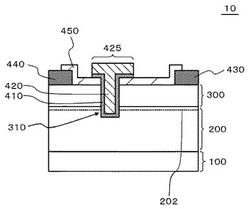

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

ショットキーダイオードおよびPNダイオード

【課題】耐量の大きいダイオードを提供する。

【解決手段】ショットキーダイオードであって、窒化物半導体で形成された半導体層と、半導体層上に形成され、半導体層にショットキー接続されたショットキー電極と、を備え、ショットキーダイオードに逆バイアスがかかったときに、ショットキー電極の端部の下方の半導体層において空乏化する領域は、ショットキー電極の他の一部の下方の半導体層において空乏化する領域より長いショットキーダイオードを提供する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

(もっと読む)

41 - 60 / 569

[ Back to top ]