Fターム[4M104HH01]の内容

Fターム[4M104HH01]に分類される特許

21 - 40 / 153

電界効果型トランジスタ

【課題】電流許容値の低下を抑制する。

【解決手段】Y方向に沿って延在する延在ゲート電極G11と、Y方向に沿って延在するダミーゲート電極DM1と、Y方向に沿って延在する延在ソース電極S11と、Y方向に沿って延在する延在ドレイン電極D11とを含む。延在ソース電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。また、延在ドレイン電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。

(もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

銅導体インク及び導電性基板及びその製造方法

【課題】導電性を低下させることなく、基板との密着性が高い導電層を形成可能な銅導体インク、及び導電層と基板との密着性が高く、該導電層の導電性が高い導電性基板を製造し得る製造方法を提供することにある。

【解決手段】銅系ナノ粒子と、熱硬化前の熱硬化性樹脂とを含有する銅導体インクであって、前記熱硬化性樹脂の含有体積が、銅系ナノ粒子を最密充填したときの空隙体積の1/4の体積より大きく、該空隙体積よりも小さい体積である銅導体インクである。また、前記銅導体インクを基板上に塗布し塗布層を形成し、乾燥する工程Aと、乾燥した塗布層に導体化処理を施し導電層へと変化させる工程Bと、前記工程Aと前記工程Bとの間に、又は前記工程Bの後に、前記熱硬化性樹脂を熱硬化する工程Cと、を含む導電性基板の製造方法である。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トランジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】めっき動作を動的に制御することの可能な電気めっき方法を提供すること。

【解決手段】ウェハ20上に銅層を形成する方法は、ウェハ20を電気めっきチャンバ10内に配置する段階であって、電気めっきチャンバ10が少なくとも一つの電気コンタクト18を通じてウェハ20に電気的に接続される制御システム34を有し、制御システム34がウェハ20に電力を提供する、段階と、ウェハ20に給電して、ウェハ20上に銅を電気めっきする段階と、電気めっき中にウェハ20の電気特性を監視して、電気めっきチャンバ10内の条件を変更すべきときを判断する段階とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】プログラム後の誤読み出しを抑制でき、高い信頼性を備える半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1上のチャンネル領域に形成されたゲート酸化膜3と、前記ゲート酸化膜3上に形成されたゲート電極4と、前記チャンネル領域の少なくとも一部に形成されたシリサイド層2と、を有し、前記シリサイド層2は、前記チャンネル領域のうち前記ゲート電極4の全体を除く領域の少なくとも一部を被覆する。

(もっと読む)

半導体装置

半導体装置が半導体基板上のゲートを含む。ゲートの1つの側壁が少なくとも1つの突出部を含んでいてもよく、ゲートの反対側壁が少なくとも1つの凹部を含んでいてもよい。接触部が、ゲート上に配置された絶縁層を通して形成されている。接触部は、ゲートの少なくとも1つの突出部に少なくとも部分的に重なっている。金属層が絶縁層上に配置されている。金属層は、ゲートの第1の側に移動した第1の構造を含む。接触部が絶縁層を通して第1の構造をゲートに電気的に連結するように、第1の構造は接触部に少なくとも部分的に重なっている。 (もっと読む)

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

Cu−Al合金粉末、それを用いた合金ペーストおよび電子部品

【課題】本発明は、配線や電極をペーストから焼成して製造する電子部品や、ガラス又はガラスセラミックス部材と接する配線を有する電子部品において、酸化による電気抵抗増大を抑制でき、あるいは、ガラス又はガラスセラミックスの気泡の発生を抑制可能で、マイグレーション耐性に優れたCu系配線材料を用いた電子部品を提供することを目的とする。

【解決手段】本発明は、ガラスまたはガラスセラミックス部材と接する配線・電極・コンタクト部材、あるいはガラスまたはガラスセラミックスと共にペーストを形成し焼成して成る配線・電極・コンタクト部材を有する電子部品であって、Cu及びAlを含む合金粉末粒子から構成され、かつ、Cu及びAlを含む合金粉末粒子の表面が80nm未満の酸化Al皮膜(Al2O3)で覆われていることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線に断線が発生することを抑制し、かつエレクトロマイグレーションに対する耐性、及び熱ストレスに起因したボイドの発生に対する耐性を配線に持たせる。

【解決手段】第2導電パターン104は端が第1導電パターン100につながっており、第1導電パターン100より幅が細い。第1導電パターン100及び第2導電パターン104は、シード層110及びメッキ層120を有する。シード層110及びメッキ層120は、それぞれ銅により形成されている。メッキ層120は、底層に、表層より結晶粒が小さい小粒層122を有している。そして第2導電パターン104を形成するメッキ層120は、小粒層122を、第1導電パターン100を形成するメッキ層120より厚く有している。

(もっと読む)

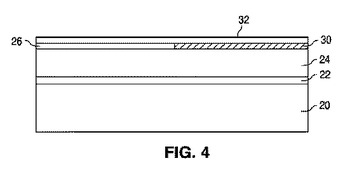

半導体発光デバイスのための反射性コンタクト

半導体構造が、n型領域20とp型領域24との間に配された、発光層22を含んでいる。p側電極が、p型領域の一部の上に配されている。p側電極は、p型領域の第1の部分と直接接触する反射性の第1の材料26と、その第1の部分に隣接するp型領域の第2の部分と直接接触する第2の材料30とを含んでいる。第1の材料26および第2の材料30は、同一の厚さのプラナー状の層として形成される。  (もっと読む)

(もっと読む)

半導体製造方法

【課題】基板面内で均一な膜厚形成を実現すること

【解決手段】この半導体製造方法は、複数の基板に連続してめっき処理を施す半導体製造方法であって、1枚の基板処理に必要なpH調整剤を含む所定量のめっき液を温度調節用容器に収容し、温度調節用容器に収容しためっき液を、めっき処理に必要なめっき成膜速度およびめっき液に含まれるpH調整剤の濃度に応じた所定の温度に調節し、基板を1枚ずつ所定位置に保持し、めっき処理に必要なめっき成膜速度およびめっき液に含まれるpH調整剤の濃度に応じたタイミングで、保持された基板1枚毎に温度調節用容器に収容され温度調節されためっき液全量を、保持された基板の処理面に吐出することを特徴とする。

(もっと読む)

画像表示パネル及び画像表示装置

【課題】製造コストを上昇させることなくマイグレーション耐性の向上及び有機半導体の劣化の抑制を実現可能な画像表示パネル及び画像表示装置を提供する。

【解決手段】第一の基板上にゲート電極、ゲート絶縁膜が積層形成され、ゲート絶縁膜上に空隙を隔ててソース電極及びドレイン電極並びに第二の接着剤が形成され、ソース電極及びドレイン電極の空隙を含む領域に有機半導体層が形成され、ゲート絶縁膜、ソース電極、ドレイン電極の一部、及び有機半導体層を覆うように層間絶縁膜が形成され、層間絶縁膜及びドレイン電極と接合されている導電層上に第一の接着剤、第一の接着剤上に形成された画像表示媒体及び第二の接着剤上に無機膜および第二の基板を有する画像表示パネルであって、第二の接着剤は、画像表示媒体と導電層との間に配置された第一の接着層よりも外側に配置され、無機膜及び親水化処理されたゲート絶縁膜と接合形成する。

(もっと読む)

アモルファスなタンタル−イリジウム拡散バリアを用いた銅相互接続構造、その形成方法、および該方法による半導体デバイス製造方法

【課題】ライナ/銅界面のボイド生成部位の排除により、高い信頼性および生産歩留まりが得られる半導体デバイス製造方法を提供する。

【解決手段】半導体デバイス製造に用いる拡散バリアを形成する方法は、物理蒸着(PVD)工程によって、パターン形成された中間誘電体(ILD)層の上に、イリジウム・ドープされたタンタル・ベースのバリア層を堆積するステップを含み、該バリア層は、原子量で少なくとも60%のイリジウム濃度で、バリア層が結果としてアモルファス構造を有するように堆積される。

(もっと読む)

配線膜用Cu合金膜および配線膜形成用スパッタリングターゲット材

【課題】 平面表示装置等の配線膜のプロセス温度域での低抵抗化が可能であるCu合金膜とそのCu合金膜を形成するためのスパッタリングターゲット材を提供する。

【解決手段】 添加元素としてBを0.1〜1.0原子%、さらにMg、Ti、Zr、Mo、Al、Siから選択される1種または2種以上の元素を0.1〜2.0原子%含み、残部Cuおよび不可避的不純物からなる配線膜用Cu合金膜である。また、上記の配線膜用Cu合金膜を形成するためのスパッタリングターゲット材である。

(もっと読む)

半導体装置およびその製造方法

【課題】配線間リーク電流の増加を抑制できる配線構造を備えた半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に設けられ、シリコン、酸素、炭素および水素を含む、配線溝5が形成された絶縁膜3,4と、配線溝5内に設けられた金属配線8と、金属配線8の上面に選択的に形成されたメタルキャップ10とを具備してなり、絶縁膜4は、その表面を含む第1の領域と、第1の領域下の第2の領域とを備えており、前記第1の領域の炭素濃度は前記表面から深くなるに従って減少し、前記第2の領域内の炭素濃度は、前記第1の領域との界面から一定距離の深さまでは深くなるに従って減少し、前記一定の距離減を越えると深くなるに従って増加し、前記表面における炭素濃度を超えることを特徴とする。

(もっと読む)

集積回路チップ上の電気めっき相互接続構造

【解決課題】 集積回路用のサブミクロン相互接続構造を製作する方法を提供する。

【解決手段】 添加剤を含み、平坦で光沢があり延性があり低応力のCu金属を付着させるのに通常用いられる浴からCuを電気めっきすることによって、ボイドのないシームレスな導体が得られる。ボイドまたはシームを残すことなくフィーチャを超充填できるこの方法の能力は独特であり、他の付着方法より優れている。この方法で電気めっきされたCuを利用する構造のエレクトロマイグレーションの抵抗は、AlCu構造または電気めっき以外の方法で付着されたCuを用いて製作された構造のエレクトロマイグレーションの抵抗より優れている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、電子供給層3上方に形成されたソース電極7s、ドレイン電極7d及びゲート電極7gと、が設けられている。ソース電極7sと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっており、ドレイン電極7dと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっている。

(もっと読む)

21 - 40 / 153

[ Back to top ]