Fターム[4M104HH16]の内容

Fターム[4M104HH16]に分類される特許

201 - 220 / 810

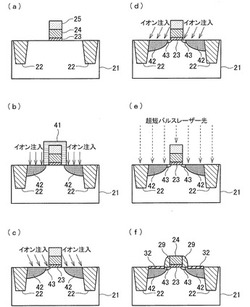

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】パターン間でのシリサイド反応の格差を抑制し、且つ、ニッケルシリサイドの表面の結晶粒上への局所的な酸化物の形成を抑制しながら未反応金属を除去する。

【解決手段】シリコン層上及び絶縁層上にニッケル(Ni)膜とキャップ膜をこの順に成膜する(ステップS1、S2)。電気炉を用いた第1熱処理によりニッケル膜をシリコン層と反応させてニッケルシリサイドを形成する(ステップS3)。SPMを用いて未反応金属を除去する除去処理を行う(ステップS4)。ニッケル膜は50Å以上150Å以下の膜厚に形成する。キャップ膜は50Å以上450Å以下の膜厚に形成する。SPMとしては、61重量%以上82重量%以下のH2SO4と、5重量%以上12重量%以下のH2O2と、13重量%以上28重量%以下のH2Oと、により構成されたものを用いる。除去処理の処理時間の長さは、20秒以上200秒以下とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率材料を含むゲート絶縁膜と、高融点金属等を含むゲート電極とを備え、消費電力の低減と高速動作化とが図られた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、高誘電率膜を含む絶縁膜101aを形成する工程(a)と、上面に酸化膜が形成され、高融点金属または高融点金属の化合物の少なくとも一方を含む第1の導電膜102aを形成する工程(b)と、酸化膜103aを間に挟んで第1の導電膜102a上に、シリコンを含む第2の導電膜104aを形成する工程(c)と、第1の導電膜102aおよび第2の導電膜104aに対してイオン注入を行い、酸化膜103aの構成材料を前記第2の導電膜104a中のシリコンと混合させてミキシング層103bを形成する工程(d)と、熱処理を行ってミキシング層103bを導電層103cにする工程(e)とを備える。

(もっと読む)

堆積錫酸カドミウム層のアニール方法および装置

マルチレイヤ構造を製造する方法は、積層体をアニールする工程を含み、該アニール工程は、不活性ガスの存在下で前記積層体を加熱する工程を含むことができ、前記積層体はカドミウムおよび錫を含む層を含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】酸化処理前における基板表面の初期酸化を抑えることができるとともに、自然酸化膜を除去できるようにする。

【解決手段】基板を処理室内に搬入する工程と、処理室内に酸素含有ガスと水素含有ガスとを供給して前記基板を処理する工程と、処理後の基板を処理室内より搬出する工程とを有し、処理工程では、処理室内の圧力を大気圧未満の圧力として処理室内に水素含有ガスを先行して導入し、続いて水素含有ガスの導入を維持した状態で酸素含有ガスを導入し、その後、水素含有ガスの導入を維持した状態で酸素含有ガスの導入を停止する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層にダメージを与えず、また、オフ電流の小さい薄膜トランジスタを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の手前側にソース電極又はドレイン電極が形成されてなるボトムゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、裏面照射によって紫外線の照射された半導体層部分を高導電率化するものであるため、半導体層へのダメージが生じないため信頼性が向上する。また、ソース電極又はドレイン電極によって紫外線が遮光された半導体層の領域は照射前の導電率と同じとなるため、オフ電流の値を小さくすることができる。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置及び配線

【課題】低抵抗の電極や配線を有する半導体装置を実現する。

【解決手段】本実施形態による配線は、p型不純物が導入されたp型不純物層部分と、n型不純物が導入されたn型不純物層部分と、p型及びn型不純物が導入された(p+n)型不純物層部分と、を含む半導体層と、少なくとも(p+n)型不純物層部分上に形成されたシリサイド層と、を備え、(p+n)型不純物層部分に含まれるp型不純物とn型不純物の総濃度は、5E20cm−3未満である。

(もっと読む)

スパッタリングターゲット及び透明導電膜及び透明導電ガラス基板

【課題】 特定の金属を含有する透明導電材料を画素電極、透明電極に使用することにより、バリヤーメタル等を堆積するための工程が不要な簡略化されたTFT(薄膜トランジスタ)基板の製造方法を提供することである。

【解決手段】 酸化インジウムを主成分とし、W、Mo、Nb、Ni、Pt、Pdからなる第1金属群M1から選ばれた1種又は2種以上の金属又はその金属の酸化物と、ランタノイド系金属からなる第2金属群M2から選ばれた1種又は2種以上の金属の酸化物と、を含むスパッタリングターゲットを利用して、透明導電膜を作製する。この透明導電膜を画素電極として利用することによって、ソース電極7等との接触抵抗を小さく抑えることができる。更に、バリヤーメタル等を用いる必要がなくなったため、バリヤーメタル等を堆積する工程をなくすことができ、TFT基板の製造工程が簡略化される。

(もっと読む)

金属複合体及びその組成物

【課題】非極性溶媒への分散性に優れ、非極性溶媒を用いた塗布法にも適用でき、導電性、電荷注入性に優れる金属複合体、及び、その組成物を提供する。

【解決手段】分子量200以上の共役化合物がアスペクト比1.5以上の金属ナノ構造体に吸着されてなる金属複合体、及び、該金属複合体と、分子量200以上の共役化合物とを含有する組成物。

(もっと読む)

現像液耐性に優れた表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ現像液耐性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で透明導電膜と直接接続されるAl合金膜であって、上記Al合金膜は、グループAに属するNiおよび/またはCoの元素を2.0原子%以下(0原子%を含まない)、並びにグループBに属する少なくとも一種の元素を0.05〜2.5原子%含み、上記グループBの元素はGd、Nd、La、Y、Sc、Pr、Dy、Ce、Ho、Er、Tb、Pm、Tm、Yb、Lu、Hf、Zr、Zn、Mg、Ti、Mn、およびGeから構成されている。

(もっと読む)

スパッタリングターゲット及びこれを利用して製造される半導体素子

【課題】スパッタリングターゲット及びこれを利用して製造される半導体素子を提供する。

【解決手段】重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成されるスパッタリングターゲットであり、また、バリア層と、バリア層上のシード層と、シード層上の導電層と、を備え、導電層は、重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成される、タングステンとニッケルとの合金薄膜を備える半導体素子である。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗を維持しつつ、ガラス基板との密着性に優れると共に、エッチング時にアンダーカットを生じることなく良好にテーパ状にエッチングできるCu合金膜を提供する。

【解決手段】ガラス基板と直接接触する表示装置用Cu合金膜であって、該Cu合金膜は、該基板と直接接触する第一層と該第一層上に形成される第二層とを含み、前記第一層が、窒素を0.4原子%以上5.0原子%未満含むと共に、Ni、Al、Zn、MnおよびFeよりなる群から選択される1種以上の元素(X元素)を0.1原子%以上0.5原子%以下、および/または、Ge、Hf、Nb、MoおよびWよりなる群から選択される1種以上の元素(Z元素)を0.1原子%以上0.3原子%以下含むものであり、かつ前記第一層の膜厚が2nm以上100nm以下であることを特徴とする表示装置用Cu合金膜。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

スパッタリングターゲット

【課題】 平面表示装置等の配線膜のプロセス温度域で、低抵抗化が可能であるとともに、ガラス基板やSi層への密着性が良好で、かつSi拡散バリア性を有するCu系配線膜を形成するために使用されるスパッタリングターゲットを提供する。

【解決手段】 Cuと添加元素と酸素の総和を100原子%とした時に、添加元素としてBを0.1〜1.0原子%、さらにBと化合物を発現する元素の少なくとも1種類以上を0.1〜2.0原子%含むとともに、酸素を3.0〜10原子%含有し、残部がCuと不可避的不純物からなるスパッタリングターゲットである。

(もっと読む)

酸素含有Cu合金膜の製造方法

【課題】 平面表示装置等の配線膜のプロセス温度域での低抵抗化が可能であるとともに、ガラス基板やSi層、SiNX保護膜層との密着性に優れる酸素含有Cu合金膜の製造方法を提供する。

【解決手段】 添加元素としてBを0.1〜1.0原子%、さらにBと化合物を発現する元素の少なくとも1種類以上を0.1〜2.0原子%含み、残部Cuおよび不可避的不純物からなるCu合金ターゲットを用いてArおよび酸素ガスを導入した雰囲気中でスパッタリングし、酸素含有Cu合金膜を得ることを特徴とする酸素含有Cu合金膜の製造方法である。

(もっと読む)

201 - 220 / 810

[ Back to top ]