Fターム[4M104HH16]の内容

Fターム[4M104HH16]に分類される特許

161 - 180 / 810

繰返し加熱における抵抗率安定性に優れるNi合金電極膜およびNi合金電極膜形成用スパッタリングターゲット

【課題】 低電気抵抗で、かつ繰返しの加熱環境にあって抵抗率安定性に優れるNi合金電極膜、そのNi合金電極膜を形成するためのスパッタリングターゲットを提供する。

【解決手段】 基板上に形成される電極膜であって、0.5〜2.0原子%のWを含有し、残部Niおよび不可避的不純物からなる組成を有し、抵抗率が30μΩcm以下である繰返し加熱における抵抗率安定性に優れるNi合金電極膜である。また、繰返し加熱に曝される電極膜形成用に用いられる0.5〜2.0原子%のWを含有し、残部Niおよび不可避的不純物からなる組成を有するNi合金電極膜形成用スパッタリングターゲットである。

(もっと読む)

電子デバイスの導電性フィーチャ

【課題】長期間貯蔵された古い金属ナノ粒子を含有する組成物を用いた場合であっても、高い導電性を有する電子デバイスの導電性フィーチャを提供することである。

【解決手段】電子デバイスの導電性フィーチャは、有機系安定剤が表面上に存在する金属ナノ粒子を含有する組成物を、基材上に成膜して成膜組成物を形成し、前記成膜組成物を加熱し、前記成膜組成物をアルカリ組成物に接触させて導電性フィーチャを形成する、ことを含む方法により形成される。前記アルカリ組成物としては、水酸化ナトリウム、水酸化カリウム、水酸化カルシウム、水酸化マグネシウム、アンモニア、炭酸ナトリウム、酢酸ナトリウム、有機アミン、イミダゾール、ピリジン、又はその混合物を含むことが好ましく、有機安定剤としては、チオール、アミン、カルボン酸、カルボン酸塩、ポリエチレングリコール、又はピリジンであることが好ましい。

(もっと読む)

半導体素子及びその製造方法

【課題】埋め込みビットラインコンタクトホール内にディフュージョンバリアーを形成して素子の特性を改善する。

【解決手段】半導体基板100をエッチングして複数個のピラーパターンを形成する段階と、前記ピラーパターンの表面に絶縁層を蒸着する段階と、前記ピラーパターンの一側の前記絶縁層の一部を除去して前記ピラーパターンが露出されるコンタクトホールを形成する段階と、前記コンタクトホール内にバリアー膜170aを形成する段階と、前記コンタクトホールと接する前記ピラーパターン内に接合180を形成する段階と、前記ピラーパターンの間の底部に前記コンタクトホールと接続して形成された埋め込みビットラインとを含む。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トランジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

成膜方法及びプラズマ処理装置

【課題】シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させることが可能な成膜方法である。

【解決手段】真空排気が可能になされた処理容器22内で被処理体Wの表面に対して薄膜を形成する成膜方法において、原料ガスを用いて処理容器内でプラズマCVD法により薄膜としてチタンを含む金属膜8を形成する金属膜形成工程と、処理容器内で金属膜に対してアニール処理を行うアニール工程とを有する。これにより、シリサイド化反応を十分に行わせることによってコンタクト抵抗を低減化させる。

(もっと読む)

半導体装置の製造方法。

【課題】本発明は、埋込みビットラインの抵抗を減少させ高速動作に有利な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、ハードマスク膜をバリアとして半導体基板をエッチングし、複数の活性領域を画定するトレンチを形成するステップと、ハードマスク膜が突出部となるように前記トレンチ内部を一部ギャップフィルするギャップフィル膜を形成するステップと、突出部の両側側壁を覆うスペーサを形成するステップと、ドープドエッチング障壁膜をエッチングバリアとしてスペーサのうち何れか1つのスペーサを除去するステップと、残留するスペーサをエッチングバリアとして前記ギャップフィル膜をエッチングし、活性領域の一側側壁を露出させる側壁トレンチを形成するステップと、を含む。

(もっと読む)

Al基合金スパッタリングターゲット

【課題】低配線抵抗と耐ヒロック性に優れた金属薄膜の形成に有用であり、好ましくはスパッタリング時のスプラッシュの発生を抑制することができるAl基合金スパッタリングターゲットを提供する。

【解決手段】本発明のAl基合金スパッタリングターゲットは、Feを0.0010〜0.4質量%と、Siを0.0010〜0.50質量%含有することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体素子

半導体素子(例えば、フリップチップ)は、介在層によってドレインコンタクトから分離されたサブストレートを含む。前記介在層を通じて延びる前記素子の動作時において、トレンチ状のフィードスルー要素を用いて、前記ドレインコンタクトおよび前記サブストレートを電気的に接続する。 (もっと読む)

半導体素子

LDMOS(横方向拡散金属酸化物半導体)構造は、ソースを基板及びゲートシールドへと接続させ、この際、このような接点のためにより小さな面積が用いられる。前記構造は、導電性基板層と、ソースと、ドレイン接点とを含む。少なくとも1つの介在層により、前記ドレイン接点が前記基板層から分離される。導電性のトレンチ状のフィードスルー要素が前記介在層を通過し、前記基板及び前記ソースと接触することで、前記ドレイン接点及び前記基板層を電気的に接続する。 (もっと読む)

金属酸化膜の形成方法および金属酸化膜

【課題】所定パターンを有するとともに、表面抵抗率や光透過率等のばらつきが少ない金属酸化膜の形成方法およびそのような金属酸化膜を提供する。

【解決手段】基材上に、所定パターンを有する金属酸化膜の形成方法等であって、基材に対して、金属塩を含有する液状物を塗布して金属塩膜を形成する第1工程と、金属塩膜に対して、所定パターンを設ける第2工程と、金属塩膜に対して、熱酸化処理または所定のプラズマ酸化処理を行い、金属酸化膜とする第3工程と、を含む。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オフ電流および漏れ電流が抑制された薄膜トランジスタ、および前記薄膜トランジスタを歩留り良く製造することのできる薄膜トランジスタの製造方法を提供する。

【解決手段】ゲート電極12上にゲート絶縁膜12を介して順次形成されるSi(i)膜13およびSi(n)膜14上に金属膜を形成し、フォトレジストパターン22をマスクとしてエッチングし、ソース電極15およびドレイン電極16を形成する。酸素を含むプラズマで処理して、フォトレジストパターン22の側面を後退させるとともに、ソース電極15およびドレイン電極16の側面および露出した上面にAl酸化皮膜17を形成する。残存するフォトレジストパターン22およびAl酸化皮膜17をマスクとして、チャネル部18のSi(n)膜14およびSi(i)膜13の表面の一部をエッチングする。

(もっと読む)

薄膜トランジスタアレイ基板、発光パネル及びその製造方法並びに電子機器

【課題】製造中のパーティクルの発生を低減して、歩留まりを改善することができる基板構造を有する薄膜トランジスタアレイ基板、該薄膜トランジスタアレイ基板を適用した発光パネル及びその製造方法、並びに、該発光パネルを実装した電子機器を提供する。

【解決手段】基板11上に形成されるトランジスタTr11、Tr12に接続される配線層のうち、最上層に形成される配線(電源電圧ラインLa、選択ラインLs)表面の少なくとも一部が陽極酸化膜で形成されている。

(もっと読む)

配線構造およびそれを備えた表示装置

【課題】銅配線層の接着性を改善するとともに、銅配線層の抵抗値が大きくなることを抑制する配線構造を提供する。

【解決手段】配線構造10では、ガラス基板11上に、チタンからなる接着層12と、酸化銅からなるバリア層13と、純銅からなる銅配線層14とが順に積層されている。接着層12は、銅配線層14をガラス基板11に確実に接着させて、銅配線層14がガラス基板11から剥がれるのを防止する。バリア層13は、配線構造10を熱処理したときに、接着層12を構成するチタン原子が銅配線層14内に拡散しないようにして、銅配線層14の抵抗値が大きくならないようにする。このため、銅配線層14は、熱処理された後も、比抵抗を小さな値に保つことができるので、信号の遅延を防止できる。

(もっと読む)

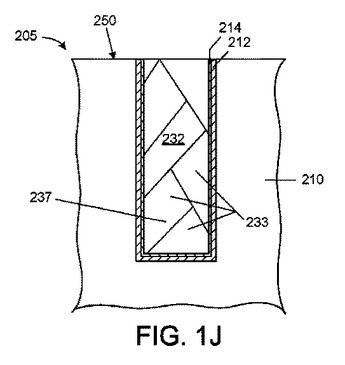

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

多結晶シリコン・ゲート上のサリサイドの抵抗を改善するための方法およびデバイス

【課題】幅の狭いポリサイドゲートにおけるシリサイドの抵抗が改善されたゲート電極構造の製造方法を提供する。

【解決手段】リセスが形成されたシリコン酸化膜からなる厚い内部スペーサ、およびシリコン窒化膜からなる厚い外部スペーサを有する多結晶シリコンゲートを形成する。多結晶シリコン上にチタンをデポジションし、アニールによりチタンシリサイド層260を形成する。チタンシリサイド層は多結晶シリコンより幅広く形成され、シリコン酸化膜からなる厚い内部スペーサによって制約を受けず、応力を受けない。

(もっと読む)

銅薄膜製造方法および銅薄膜

【課題】 金属の微粒子の分散体を用いて絶縁基板上に低体積抵抗率の導電層を得ることができる、金属薄膜の形成方法を提供する。

【解決手段】 銅粒子表面のCu(I)とCu(II)の比が100対0〜30対70モル比の範囲にある銅粒子の分散体からなる塗膜に過熱水蒸気による加熱処理を施す工程を含む、銅薄膜の製造方法およびこの方法で製造された銅薄膜。前記塗膜は銅粒子分散体を絶縁性基板に塗布または印刷されたものであることが好ましい。

(もっと読む)

太陽電池素子の製造方法及び太陽電池素子

【課題】凹凸が小さく滑らかな半円形状で抵抗の低い集電極を備えた曲線因子の高い太陽電池素子を提供する。

【解決手段】半導体基板10上にスクリーン印刷法により導電性ペースト8を複数回重ねて印刷して多層電極を形成するに際し、スクリーン印刷製版7を用いて一層目の電極を印刷した後、上記基板又はスクリーン印刷製版の位置を一層目の電極印刷時の基板又はスクリーン印刷製版位置より一層目の電極の長手方向に沿ってずらした状態で上記一層目の電極の直上にこれと重ねて二層目の電極を印刷し、更に必要により、三層目以降の電極を上記と同じ方向に順次ずらして印刷して多層電極を形成する。

(もっと読む)

161 - 180 / 810

[ Back to top ]