Fターム[4M104HH16]の内容

Fターム[4M104HH16]に分類される特許

101 - 120 / 810

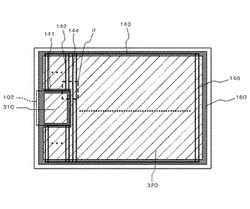

半導体装置

【課題】ゲート抵抗の増大を抑制しつつ、外部ウェルがトレンチゲート電極によってセル領域のウェルから分断されてしまうことを抑制する。

【解決手段】埋込ゲート電極140のうち平面視でゲートコンタクト領域102と重なる方向に延伸している埋込ゲート電極142は、ゲート電極310と重ならないように、ゲート電極310の手前までしか延伸していない。また埋込ゲート電極142の相互間に位置するソースコンタクトは、図中上下方向において、埋込ゲート電極142よりも短く形成されている。そして埋込ゲート電極142のうちゲート電極310側の端部は、ゲート電極310の手前に設けられた接続用埋込電極141によって互いに接続されている。接続用埋込電極141は、半導体装置の長辺と平行な方向に延伸している。接続用埋込電極141は、埋込ゲート電極142の隣に位置する埋込ゲート電極144には接続していない。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

配線材料、配線の製造方法、及びナノ粒子分散液

【課題】焼成無しで、酸素雰囲気に安定であり、かつ低抵抗な配線材料を提供する。また、従来の配線材料よりも低い温度で還元焼成できる配線材料を提供する。

【解決手段】銅と窒素を含む配線材料であって、当該配線材料には、添加材料として、エリンガム図において銅よりも酸化しやすい材料が0.5atm%以上10atm%以下添加されている。添加材料として、例えば、Si、Zr、Ti、Ni、Sn、Mn、Alのうち少なくとも1種類の金属を含む。この配線材料を加熱還元して低抵抗化する場合、1000Pa以下に減圧した雰囲気で加熱を行うことが好ましい。

(もっと読む)

化合物半導体発光素子の製造方法

【課題】化合物半導体発光素子に含まれる透光性酸化物導電膜の光透過率の向上、シート抵抗の低減、シート抵抗の面内分布の均一化、およびコンタクト層に対するコンタクト抵抗の低減の少なくともいずれかを可能ならしめる化合物半導体発光素子の製造方法を提供する。

【解決手段】化合物半導体発光素子の製造方法において、基板(1)上に発光層(3)を含む化合物半導体積層体(2−5)を堆積し、この化合物半導体積層体(2−5)上に透光性酸化物導電膜(8)を堆積し、この透光性酸化物導電膜(8)はアニールされてその後に真空雰囲気中で冷却されることを特徴としている。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線の製造方法は、絶縁膜13内に、配線溝30を形成し、前記配線溝内の全面に、触媒膜14を形成し、前記配線溝内の前記触媒膜上に、前記配線溝の底面に対して垂直方向に積層された複数のグラフェンシート16a〜16eで構成されるグラフェン層16を形成することを具備する。

(もっと読む)

半導体デバイス、その製造方法及び集積回路

【課題】電極領域の抵抗を従来よりも一段と低減させることができる半導体デバイス、その製造方法及び集積回路を提供する。

【解決手段】III−V族化合物半導体層4上にニッケル層17を形成し、RTA処理により加熱することで、ニッケルIII−V族合金(Ni-InxGa1-xAsyP1-y合金)からなるソース領域5及びドレイン領域6が形成される。これにより、MOSFET1では、III−V族化合物半導体層4に対して単に不純物をインプラテーションで注入して形成された従来のソース領域及びドレイン領域の寄生抵抗に比べて、ソース領域5及びドレイン領域6の寄生抵抗を一段と低減させることができる。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタル層の金属配線に対する密着性を向上させつつ、金属配線の低抵抗化を図った半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜15に形成された凹部16、17内にバリアメタル層20を形成した後、凹部16、17内にCu配線層23を形成する。バリアメタル層20の形成工程は、凹部16、17内にTi含有量が50原子%を超える第1のTiNx膜18を形成した後、側壁部上と比較して底部上に相対的に多く形成されるように、Ti含有量が第1のTiNx膜18より多い第2のTiNx膜(またはTi膜)19を形成する。

(もっと読む)

EL表示装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものと

して、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を

有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線

上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層

と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前

記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを

特徴としている。

(もっと読む)

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

トランジスタ及びその製造方法。

【課題】活性層中への電極材の拡散の抑制、電極材の低電気抵抗化、さらには活性層へのダメージ低減を図ることができる、酸化物半導体からなる活性層を有する電界効果型トランジスタ及びその製造方法を提供すること。

【解決手段】本発明の一実施形態に係るトランジスタは、酸化物半導体からなる活性層と、Ti系材料またはMo系材料からなる第1の電極層と、第1の電極層の材料よりも比抵抗の小さい材料からなる第2の電極層とを具備する。

上記構成によれば、酸化物半導体からなる活性層に対する拡散が小さい第1の電極層と、比抵抗が小さい第2の電極層を積層することにより、活性層と電極層の層界面でのFET特性が良好であり、電気抵抗の小さい電極を備えたFETを得ることが可能である。

(もっと読む)

透明導電性薄膜の形成方法および透明導電性薄膜の形成装置

【課題】エピタキシャル成長した透明導電性薄膜の製造方法と製造装置および結晶性薄膜の多層構造による、新たなフォトエレクトロニクスデバイスを提供する。

【解決手段】真空室中の基板5を300℃〜500℃に加熱し、不活性ガス圧力0.05Pa〜0.3Pa、酸素分圧5x10-4Pa〜1.5x10-3Paの範囲に制御し、基板に対して高密度プラズマ照射を行うにより、結晶性基板上に薄膜形成材料をエピタキシャル成長させて透明導電性薄膜を形成する。

(もっと読む)

パターンの製造方法

【課題】本発明は、パターンの製造方法に関し、特に、レーザーを用いてパターンを製造する方法に関する。

【解決手段】パターンの製造方法は、基板上に金属有機インク層(20)を形成する第1の段階;前記金属有機インク層(20)を半固体状態に硬化させる第2の段階;前記半固体状態の金属有機インク層(20)にレーザー光を照射し、照射された部分が固体状態に硬化されてパターンが形成される第3の段階、および、前記半固体状態の金属有機インク層(20)を除去して、前記パターンだけを残す第4の段階を含む。

(もっと読む)

Co膜形成方法

【課題】膜中及び膜表面の不純物が効果的に除去でき、Cu配線構造に適用したときにバリア層及びCu配線層に対する密着性に優れて一層の低抵抗を実現できるCo膜形成方法を提供する。

【解決手段】基材Sを処理室10内に配置して処理室内を真空引きすると共に、基材を一の所定温度に加熱し、アルキル基を有するイオン又は分子がコバルトに配位した有機金属材料Lを気化させ、気化させた有機金属材料を基材表面に供給し、有機金属材料を熱分解させてCo膜を成膜する。その後、同一の処理室内で、またはCo膜が成膜された基材を他の処理室内に配置し、この基材をアンモニアガスと水素ガスとを含む混合ガス雰囲気中にて他の所定温度でアニールする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート−ソース間の容量低減及びソース抵抗を低減させ、且つ耐圧向上、高出力化及び高周波化を、容易且つ確実に可能とする量産化に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極19を形成する際に、4層の電子線レジスト11〜14を用いてゲート開口17を形成し、ゲート開口17内に、キャップ層5の表面との接触面を含む幹状の下方部分19aと下方部分19aから傘状に拡がる上方部分19bとが一体形成されてなり、下方部分19aの接触面がドレイン電極7に比べてソース電極6に偏倚した位置に設けられており、上方部分19bの傘状の下端面のうちソース電極6側の部位がドレイン電極7側の部位よりもキャップ層5の表面からの高さが高いゲート電極19を形成する。

(もっと読む)

接合型電界効果トランジスタ

【課題】 従来のJ−FETでは、動作領域内のゲート領域(トップゲート領域)は、動作領域外周に設けられた深いゲート領域を介してのみ、半導体基板(バックゲート領域)と接続していた。このため動作領域の中央と外周ではゲート抵抗にばらつきが生じ、ゲート抵抗の増加によるノイズ電圧の増加や、不均一動作によるゲインの低下が問題であった。

【解決手段】 格子状のゲート領域(トップゲート領域)を有するJ−FETにおいて、行列状にソース領域と交互に配置されていたドレイン領域の一部を深いゲート領域に置き換え、動作領域内にも深いゲート領域を設ける。ドレイン領域を一部省くことで生じるドレイン電流の流れない無効領域をできる限り減らすため、ソース領域が配置されるセルについてドレイン電流が流れない方向のゲート領域を短くする。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

101 - 120 / 810

[ Back to top ]