Fターム[4M104HH16]の内容

Fターム[4M104HH16]に分類される特許

81 - 100 / 810

酸化物膜の製造方法

【課題】p型の導電膜及びp型の透明導電膜としての高性能な酸化物膜の、量産性に優れた製造方法を提供する。

【解決手段】

本発明の1つの酸化物膜の製造方法は、酸素を含むガスの雰囲気下で、反応性スパッタリング法により、銅(Cu)からなる第1ターゲット30a,30aとニオブ(Nb)およびタンタル(Ta)からなる群から選択される1種類の遷移元素からなる第2ターゲット30b,30bとを用いて交互にスパッタを行うことにより、基板10上に第1酸化物膜(不可避不純物を含み得る)を形成する工程、及びその第1酸化物膜を不活性ガス雰囲気中で加熱焼成することにより第2酸化物膜(不可避不純物を含み得る)を形成する工程を含む。従って、この製造方法によって形成された酸化物膜は、大型基板上への膜の形成が容易になることから、量産性に優れている。

(もっと読む)

Cu配線の形成方法およびCu膜の成膜方法、ならびに成膜システム

【課題】微細なトレンチまたはホール等の凹部にボイドを発生させずに確実にCuを埋め込むことができ、かつ低抵抗のCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202において、トレンチ203の表面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上に、加熱しつつ、PVDによりCuがマイグレーションするようにCu膜206を形成してトレンチ203を埋める工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

低抵抗材料のビーム誘起堆積

【課題】低抵抗率金属を堆積することができるビーム堆積方法を提供する。

【解決手段】ヘキサメチル二スズのようなメチル化又はエチル化金属などの低抵抗率の金属材料を堆積できる前駆体を試料表面に向けて導入し、ガリウム集束イオンビームを試料表面の所望の位置に照射して、その位置に40μΩ・cmと低い抵抗率のスズ膜を堆積する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】材料の選択幅が広く、生産性が高いTFT、アクティブマトリクス基板、およびそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2と、半導体層5と、半導体層5の上に設けられ、半導体層5と電気的に接続されたソース電極7、及びドレイン電極8と、を備えた薄膜トランジスタであって、半導体層5が、透光性半導体膜5aと、透光性半導体膜5a上に配置され、透光性半導体膜5aよりも光透過率の低いオーミック導電膜5bと、を有し、オーミック導電膜5bが、透光性半導体膜5aからはみ出さないように形成され、オーミック導電膜5bが、ソース電極7とドレイン電極8の間のチャネル部9を挟むように分離して形成され、ソース電極7、及びドレイン電極8が、オーミック導電膜bを介して、透光性半導体膜5aに接続されているものである。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

銅含有組成物、金属銅膜の製造方法、および金属銅膜

【課題】銅の高原子価化合物から金属銅膜を製造する組成物、金属銅膜の製造方法、および金属銅膜を提供する。

【解決手段】銅化合物;直鎖、分岐または環状の炭素数1から18のアルコール類;VIII族金属触媒;バインダー樹脂;バインダー樹脂硬化剤および銅錯体から成る銅含有組成物を被膜とし、不活性ガス;水素、または、不活性ガスと水素の混合ガス中で、加熱して金属銅膜を製造する。

また、銅化合物;直鎖、分岐または環状の炭素数1から18のアルコール類;VIII族金属触媒;バインダー樹脂;バインダー樹脂硬化剤;銅錯体およびレオロジー調整剤から成る銅含有組成物を被膜とし、不活性ガス;水素、または、不活性ガスと水素の混合ガス中で、加熱して金属銅膜を製造する。

(もっと読む)

金属銅膜の作製方法及び印刷金属銅パターン

【課題】印刷形成が可能である銅系粒子堆積層を、基板密着性、低体積抵抗率、基板ダメージがなく深部まで還元する処理方法であり、且つ印刷塗布部外への銅の析出を抑制した、金属銅膜の作製方法、及び、作製した印刷金属銅パターンを提供する。

【解決手段】基板上に形成された、酸化銅からなる粒子を含む銅系粒子堆積層を、120℃以上において、ガス状のギ酸と、ガス状の1価のアルコール/エステル/ケトンから選択される少なくとも1種の有機溶剤と混合ガスにより処理する、金属銅膜の作製方法。

(もっと読む)

金属薄膜電極及びその製造方法

【課題】本発明は、金属薄膜電極及びその製造方法に関する。

【解決手段】本発明の一実施例による金属薄膜電極の製造方法は、基材上に金属粉末、有機バインダ及び有機溶媒を含む金属ペーストを塗布して金属薄膜を形成する段階と、金属薄膜を有機酸と水系液の比が10:90〜90:10の雰囲気で還元焼成する段階と、を含む。

(もっと読む)

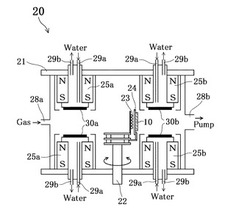

スパッタリング方法

【課題】複数のターゲットの同時放電による反応性スパッタリングにおいて、堆積された膜の組成をコントロールすることを目的とする。

【解決手段】各ターゲットへの反応性ガスの供給量を異ならせることで、一方のターゲットからは反応性ガスとの反応生成物がスパッタされ、他のターゲットからはターゲット材質がスパッタリングされる。これにより、堆積される膜の組成をコントロールすることが可能となる。また、一方のターゲットをポイズンモードとし、他のターゲットをメタルモードとしてスパッタリングを行うことで、反応生成物と金属からなる化合物が成膜される。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、セルの有効面積を増やし、アンバランス動作等を抑制可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、第1層間絶縁膜8に覆われない上面を介して、ゲート電極20と接続された、第1ゲート配線5と、第1ゲート配線5の、上面の一部を除く領域を覆って、第1層間絶縁膜8上に形成された、第2層間絶縁膜80と、第2層間絶縁膜80に覆われない上面を介して、第1ゲート配線5と接続された、第2ゲート配線16とを備え、平面視において、第2ゲート配線16の幅は、第1ゲート配線5の幅よりも広い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】所望の抵抗値を有する制御ゲートを備えた半導体装置の製造方法を提供すること。

【解決手段】シリコン基板13の表面上に第1の絶縁膜15、電荷蓄積層16、第2の絶縁膜17、およびポリシリコン膜21をこの順で形成する工程と、ポリシリコン膜21上および両側壁全面に金属膜25を形成する工程と、金属膜25が形成されたポリシリコン膜21を加熱してシリサイド化する工程と、金属膜25を除去する工程と、を具備する半導体装置の製造方法。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートメタル電極とHigh−k膜とを用いた半導体装置において、低抵抗なゲートメタル電極により仕事関数を調整できるようにする。

【解決手段】半導体装置は、Nウェル102の上に形成された第1のゲート絶縁膜109と、該第1のゲート絶縁膜109の上に形成された第1のゲート電極とを備えている。第1のゲート絶縁膜109は、第1の高誘電体膜109bを含み、第1のゲート電極は、第1の高誘電体膜109bの上に形成され、TiN層110aとAlN層110bとが交互に積層された第1の実効仕事関数調整層110を含む。TiN層110aはAlN層110bよりも抵抗が小さく、且つ、AlN層110bはTiN層110aよりも実効仕事関数の調整量が大きい。

(もっと読む)

タングステンスパッタリングターゲットおよびその製造方法

【課題】基板上に成膜したW膜の膜厚面内均一性を向上させることが可能であり、さらにはパーティクルの発生を減少させることが可能なWスパッタリングターゲットおよびその製造方法を提供する。

【解決手段】Wスパッタリングターゲットは、スパッタリングされる面のX線回折により得られた結晶面(110)のピークの半値幅が0.35以下であることを特徴とする。また、本発明の高純度Wスパッタリングターゲットの製造方法は、高純度W粉末を加圧焼結後、得られた焼結体をターゲット形状に加工後、ロータリー研磨およびポリッシングの少なくとも1種の研磨を施し、さらにエッチングおよび逆スパッタリングの少なくとも1種の研磨を施すことにより仕上げ加工することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 製造工程の増加を招くことなく、タングステン配線の低抵抗化できる半導体装置の製造方法を提供する。

【解決手段】 本発明は、基板表面に、微細形状を有する絶縁層を形成した後、この微細形状を含む絶縁層表面に、Ta膜またはTaN膜からなる下地層を形成する工程と、下地層の表面に、タングステンから膜なる配線層を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】添加元素に起因してNiシリサイド層が高抵抗化することを抑制する。

【解決手段】まず、シリコン層100上に、Niより原子番号が大きい金属元素を含み、Niを含まない反応制御層202を形成する。次いで、反応制御層202上にNiを堆積し、シリコン層100、反応制御層202、及びNiを熱処理することにより、シリコン層100にNiシリサイド層200を形成する。反応制御層202は、Niより原子番号が大きい金属元素から構成されるのが好ましい。

(もっと読む)

半導体装置

【課題】ゲート抵抗の増大を抑制しつつ、外部ウェルがトレンチゲート電極によってセル領域のウェルから分断されてしまうことを抑制する。

【解決手段】埋込ゲート電極140のうち平面視でゲートコンタクト領域102と重なる方向に延伸している埋込ゲート電極142は、ゲート電極310と重ならないように、ゲート電極310の手前までしか延伸していない。また埋込ゲート電極142の相互間に位置するソースコンタクトは、図中上下方向において、埋込ゲート電極142よりも短く形成されている。そして埋込ゲート電極142のうちゲート電極310側の端部は、ゲート電極310の手前に設けられた接続用埋込電極141によって互いに接続されている。接続用埋込電極141は、半導体装置の長辺と平行な方向に延伸している。接続用埋込電極141は、埋込ゲート電極142の隣に位置する埋込ゲート電極144には接続していない。

(もっと読む)

半導体装置の製造方法

【課題】本発明は半導体装置に関する。

【解決手段】本発明は、半導体基板上のセル領域のセルトランジスタ上の層間膜を貫通してコンタクトプラグが形成され、周辺回路領域のトランジスタ上の層間膜を貫通してコンタクトプラグが形成されてなる半導体装置の製造方法であり、セルトランジスタ上の層間膜にコンタクトホールを形成し、その底部側にシリコン膜の下部導電プラグを形成する工程と、その上に金属膜を積層して積層構造のセルコンタクトプラグを形成する工程と、周辺回路用トランジスタ上の層間膜にコンタクトホールを形成し、その内部に金属膜を形成してコンタクトプラグを形成する工程とを具備し、前記セル領域のコンタクトホール内のシリコン膜上に金属膜を形成する工程と前記周辺回路領域のコンタクトホール内に金属膜を形成する工程を同時に行うことを特徴とする。

(もっと読む)

81 - 100 / 810

[ Back to top ]