Fターム[4M104HH16]の内容

Fターム[4M104HH16]に分類される特許

141 - 160 / 810

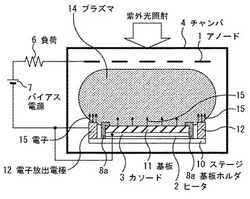

電子デバイスの製造方法

【課題】カーボン膜の抵抗率を低減することができる電子デバイスの製造方法を提供する。

【解決手段】基板11が載置されたチャンバ4内に炭素を含有する原料ガスを供給する。基板11の周囲からチャンバ4内のアノード1に向けて電子を放出させてチャンバ4内にプラズマ14を発生させ、基板11上にグラファイト、グラフェン等のカーボン膜を形成する。

(もっと読む)

電子素子基板及びその製造方法

【課題】酸化物の一部領域又は全領域の比抵抗を低下させることにより、簡易な工程で多様な電子素子を作製できる電子素子基板の製造方法を提供する。

【解決手段】少なくとも最表層の一部が比抵抗1×109Ω・cm以下の酸化物からなる基板における前記酸化物の一部領域又は全領域に対し、前記基板の電位よりも高い電位を印加することにより、前記一部領域又は前記全領域の比抵抗を低下させる低抵抗化処理工程を有する電子素子基板の製造方法である。

(もっと読む)

半導体トランジスタの製造方法

【課題】プロセスの自由度を高めつつ、活性層とオーミックコンタクトをとるオーミック電極を形成できる半導体トランジスタの製造方法を提供する。

【解決手段】GaN系の半導体からなる活性層上に、オーミック電極を形成する半導体トランジスタの製造方法であって、活性層3上に、タンタル窒化物からなる第1の層11と、第1の層11上に積層されたAlからなる第2の層12とを形成する工程と、第1及び第2の層11,12を、520℃以上、600℃以下の温度で熱処理することにより、活性層3とオーミックコンタクトをとるオーミック電極9s,9dを形成する工程とを備える。

(もっと読む)

スパッタリングターゲットとそれを用いたTi−Al−N膜および電子部品の製造方法

【課題】FeRAMやDRAMなどに使用されるTi−Al−N膜などの成膜用のTi−Al合金ターゲットにおいて、不純物量の低減を図った上で、ターゲットの製造歩留りを高めると共に、膜品質の向上などを図る。

【解決手段】スパッタリングターゲットはAlを5〜50原子%の範囲で含有するTi−Al合金からなる。このようなTi−Al合金ターゲットにおいて、Zr含有量およびHf含有量をそれぞれ100ppb以下とする。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】エミッタメサの加工精度を損ねることなく、HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、SiNからなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲には、酸化シリコンからなる第2絶縁層109が形成されている。第2絶縁層の下端部には、レッジ構造部1105aが形成されている領域より外側に延在し、第1絶縁層108およびレッジ構造部105aの側方のベース層104との間に空間を形成する庇部109aが形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】 半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

積層回路材料

【課題】特性インピーダンスを小さくできるために、超高周波又は超高速信号の伝送時においても反射や放射が少なく、かつ低損失である回路材料を提供する。

【解決手段】単一元素からなる原子層が単層若しくは複数層で構成する導体層と、導体層を構成する元素同士間の原子間結合よりもより安定な結合を形成する単一又は復数の元素からなる原子層が単層若しくは複数層で構成する拘束層とからなり、前記導体層と拘束層の原子同士が原子的整合状態(ヘテロ構造)で積層することを特徴とする回路材料の電気抵抗低下方法。

(もっと読む)

液滴吐出装置の洗浄方法

【課題】液滴吐出装置の液滴吐出ヘッドに影響を与えることなく、液滴吐出装置の導体パターン形成用インクの流路における汚れを好適に解消できる液滴吐出装置の洗浄方法を提供すること。

【解決手段】本発明の液滴吐出装置の洗浄方法は、金属粒子が水系分散媒に分散したインクを吐出する液滴吐出装置を洗浄する方法であり、当該液滴吐出装置は、インクを貯留するインク貯留層と、インクを吐出する吐出部を備えた液滴吐出ヘッドと、インク貯留部から液滴吐出ヘッドに向かってインクを搬送する搬送路と、搬送路に設けられ、インクの逆流を防止する自己封止弁と、搬送路の自己封止弁よりもインク貯留部側に設けられたフィルターとを有し、液滴吐出装置の洗浄に用いられる洗浄液を、搬送路に、インクの流れる方向とは反対方向に向かって流すことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

接続されたナノ構造体及びそのための方法

種々の材料及びアプローチの1以上を用いてナノ構造体を接続する。種々の例示的実施形態で、ナノ構造体間の接続部で2つ以上のナノ構造体が接続される。ナノ構造体は、接続部で接触するかほぼ接触してよく、接続材料を接続部で堆積及び核形成させてナノ構造体同士を結合する。種々の用途で、核形成した接続材料はナノ構造体間の伝導率(熱的及び/又は電気的)を向上させる。いくつかの実施形態では、接続材料は更に、例えばナノ構造体に沿って成長することにより及び/又はナノ構造体にドープすることにより、ナノ構造体自身の伝導率を上昇させる。  (もっと読む)

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

太陽電池電極用ペーストおよび太陽電池セル

【課題】良好な印刷性を保持しつつ、体積抵抗率を低く、かつ、アスペクト比を高くすることができ、また、シリコン基板との密着性にも優れる電極を形成することができる太陽電池電極用ペーストおよびそれを用いた太陽電池セルの提供。

【解決手段】銀粉(A)と、所定の式で表される2種の脂肪酸銀塩(B)と、ビヒクル(C)とを含有し、

前記銀粉(A)が、平均粒子径が0.7〜5μmの球状の銀粉末である太陽電池電極用ペースト。

(もっと読む)

密着性を改良するための基板のプラズマアニーリング

【課題】許容可能な拡散バリア特性と基板への密着性を耐熱性金属窒化物が有するように、基板上への窒化チタンなどの耐熱性金属窒化物膜の形成を提供する。

【解決手段】材料の層が、ウェハ上に部分的に形成された集積回路内の基板上に形成される。基板はプラズマアニールを受け、その間に基板はイオンでボンバードされる(工程300)。プラズマアニールは、エネルギーを注入された窒素含有ガスから生成されたプラズマへ基板を曝すことにより実行できる。基板がプラズマアニールされた後、耐熱性金属窒化物の層が基板上に堆積される(工程301)。耐熱性金属窒化物の層は、次に、第1セットのイオンでボンバードされる。第1セットのイオンによる耐熱性金属のこのボンバードは、プラズマアニールを実行することにより達成できる。耐熱性金属窒化物は、更に、第2セットのイオンによりボンバードされる(工程302)。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

141 - 160 / 810

[ Back to top ]