Fターム[4M106AA01]の内容

半導体等の試験・測定 (39,904) | 対象 (8,684) | ウエハ (5,556)

Fターム[4M106AA01]に分類される特許

121 - 140 / 5,556

電気特性取得評価方法

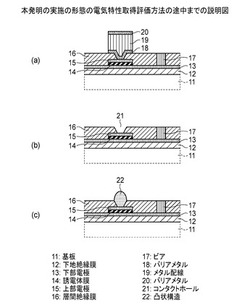

【課題】電気特性取得評価方法に関し、試料側にもプローブ側にも問題を発生させることなく安定な電気特性取得評価を行う。

【解決手段】積層体の表面側電極に対するコンタクトホール21を露出する工程と、前記露出したコンタクトホール21に導電性物質を埋め込んで凸状構造22を形成する工程と、前記凸状構造22を含む領域にカンチレバーを間欠接触測定方式で接触させて前記凸状構造22の位置を認識する工程と、前記凸状構造22の中心軸の方向に前記カンチレバーを押しつけて電気特性を取得する工程とを設ける。

(もっと読む)

シリコン単結晶ウェーハの製造方法並びにシリコン単結晶ウェーハの評価方法

【課題】ゲート酸化膜の厚さが数nmと薄い場合であってもGOIの劣化がないシリコン単結晶ウェーハとその製造方法、並びにGOI劣化がないことをTDDB法などに比べて容易に評価することのできる評価方法を提供する。

【解決手段】少なくとも、シリコン単結晶インゴットを準備する工程と、該シリコン単結晶インゴットをスライスしてスライス基板を複数枚作製する工程と、該複数枚のスライス基板に、ラッピング・エッチング・研磨のうち少なくとも1つを行って複数枚の基板に加工する加工工程と、該複数枚の基板から少なくとも1枚を抜き取る工程と、該抜き取り工程で抜き取った基板の表面粗さをAFMで測定し、波長20nm〜50nmに対応する周波数帯の振幅(強度)を求めて合否を判定する工程と、前記判定が合格の場合は次工程へ送り、不合格の場合は再加工を行う工程と、を含むことを特徴とするシリコン単結晶ウェーハの製造方法。

(もっと読む)

半導体素子の検査処理方法

【課題】磁気センサ等の半導体素子の特性検査から梱包までの一連の作業をトレイを使用することなく効率的に行う。

【解決手段】各半導体素子10をダイシングテープ31上でマトリクス状に並べられた状態に分離する工程と、各半導体素子10をダイシングテープ31毎載置して水平方向及び垂直方向に移動しながらプローブに接触させて検査するプローブ検査工程と、プローブ検査工程を経た後の各半導体素子10をダイシングテープ31上から少なくとも1個ずつピックアップして搬送テーブル32上に搭載し、搬送テーブル32により順次搬送される半導体素子10の第1の主面10aを外観検査する第1の主面検査工程と、第1の主面検査工程を経た後の半導体素子10を把持して反転し、半導体素子10の第2の主面10bを外観検査する第2の主面検査工程と、第2の主面検査工程を経た後の半導体素子10を順次ピックアップして梱包する梱包工程とを備える。

(もっと読む)

配線基板及びその製造方法

【課題】配線基板の内部配線層の数を一定とした場合において、DUT部内に配設することが可能な特定電極パッドの数を導出することが可能な配線基板の製造技術を得、これによって、DUT部内に所定の数の特定電極パッドを配設する際に必要とされる内部配線層の最低数を導出することができ、配線基板を小型化及び簡略化する。

【解決手段】特定内部配線層の層数をA、各DUT部内に配設された複数の表面電極パッドの列数をN、及び各DUT部内に配設すべき特定表面電極パッドの個数をBとした場合において、特定表面電極パッドの個数Bは、

B<(X+1)×A

(Xは、1からNまでの自然数)

なる関係式を満足するようにする。

(もっと読む)

半導体基板の解析方法

【課題】半導体基板中での少数キャリアの拡散定数を簡便に求めることのできる手法を提供する。

【解決手段】第1の面および第2の面の表面再結合速度が2.8×104[cm/sec]以上に調整された第1の半導体基板の一次モードライフタイムτ1(1)(104)、ならびに、第1の面および第2の面の一方の表面再結合速度が2.8×104[cm/sec]以上、他方の表面再結合速度が10[cm/sec]以下に調整された第2の半導体基板の一次モードライフタイムτ1(2)(106)をμ−PCD法により測定し、得られたτ1(1)τ1(2)および半導体基板の厚さWを以下の近似式に代入することで、半導体基板中の少数キャリアの拡散定数Dを簡便に求める。 (もっと読む)

(もっと読む)

絶縁物/半導体界面の評価方法及び評価装置

【課題】MISあるいはMOS界面の欠陥密度(界面準位密度)を簡便かつ高い精度で求める。

【解決手段】絶縁物/半導体界面における界面欠陥に起因する容量CITが無視できる程度の高周波におけるC−V特性を元に、酸化膜容量の影響を排除した半導体容量(CD+CIT)を計算するステップと、1/(CD+CIT)2を低周波(準静電的)C−V特性から計算される表面ポテンシャルψsに対してプロットするステップと、ψs−1/(CD+CIT)2プロットの外挿値が原点を通るように定数項を定めることにより、表面ポテンシャルψsの絶対値を確定するステップと、を有することを特徴とする絶縁物/半導体界面の評価方法。

(もっと読む)

検査計測装置および検査計測方法

【課題】

荷電粒子ビームを用いた計測装置ないし検査装置において、検査の高感度と高安定性とを両立する。

【解決手段】

帯電制御電極A420の被計測試料ないし検査試料側に帯電制御電極B421を設置し,試料の帯電状態に応じて、帯電制御電極Bの帯電制御電極制御部423から一定の電圧を与えることにより、検査前に形成した試料表面の帯電状態と電位障壁の変動を抑制する。帯電制御電極制御部66によりリターディング電位が印加され、試料と同電位に調整される帯電制御電極A420の更に下部に帯電制御電極B421が設けられることにより、一次電子ビーム19が照射されるウェハ9などの試料から放出された二次電子409の試料への戻り量を調整することが可能になり,高感度な検査条件を検査中安定的に維持することが可能となる。

(もっと読む)

半導体装置の検査方法、検査プログラム及び半導体装置の検査装置

【課題】短時間で半導体装置の検査を行うことができる半導体装置の検査方法、検査プログラム及び半導体装置の検査装置を提供すること。

【解決手段】本発明は、記憶部2から半導体装置SD1の特性データDAT1を読み込む。次いで、ストローブ演算式212にNMOSトランジスタの閾値Vt1を代入することにより、半導体装置SD1に対するストローブ値STB1する。次いで、半導体装置SD1にテスト入力信号Dinを出力する。そして、ストローブ値STB1で指定されるタイミングで、半導体装置SD1から出力されるテスト出力信号Doutのパターンが期待値パターンEPと一致するかを判定する。

(もっと読む)

レシピ生成装置、検査支援装置、検査システムならびに記録媒体。

【課題】設計レイアウトに記録された情報を、直接、解析して、所望の領域を抽出し、この抽出方法を用いて検査レシピを生成し、効率的な検査を実現する。

【解決手段】設計レイアウトデータの階層情報を解析して、その内部データであるセル一つ一つが設計レイアウトデータ内での参照回数を計算して、参照回数の多い順に並び替えて、対象を探索し、その上位セルを追跡することによって、メモリマットなどの所望の回路モジュールの領域抽出を容易にする。

(もっと読む)

ウエハ搬送装置

【課題】複数の検査室によって共有することによりフットプリントを削減することができるウエハ搬送装置を提供する。

【解決手段】本発明のウエハ搬送装置10は、筐体Fを収納するウエハ収納室11と、ウエハ収納室11の下側に配置されたプリアライメント室12と、ウエハ収納室11及びプリアライメント室12に沿って上下方向に配置され且つウエハ収納室11とプリアライメント室12との間で半導体ウエハを搬送する第1のウエハ搬送機構13を有する第1のウエハ搬送室14と、第1のウエハ搬送室14とでプリアライメント室12を挟む位置に配置されアライメント室15と、第1のウエハ搬送室14、プリアライメント室12及びアライメント室15の配列方向に沿って移動すると共に上下方向に移動する第2のウエハ機構16を有する第2のウエハ搬送室17と、を備えている。

(もっと読む)

膜厚測定装置

【課題】本発明は、被測定物との距離に依存することなく、被測定物の膜厚を高い精度を測定することが可能な膜厚測定装置を提供する。

【解決手段】本発明は、光源10と、第1光路と、第1集光レンズと、分光測定部40と、第2光路と、第2集光レンズと、データ処理部50を備える膜厚測定装置100である。光源は、所定の波長範囲をもつ測定光を照射する。第1光路は、光源10から照射した測定光を被測定物に導く。第1集光レンズは、第1光路から出射する測定光を被測定物に集光する。分光測定部40は、反射率または透過率の波長分布特性を取得する。第2光路は、被測定物で反射された光または被測定物を透過した光を、分光測定部に導く。第2集光レンズは、第2光路の端部に集光する。データ処理部50は、分光測定部40で取得した波長分布特性を解析することで、被測定物の膜厚を求める。

(もっと読む)

パワーデバイス用のプローブカード

【課題】プローブとテスタ間の測定ラインと載置台とテスタ間の測定ラインそれぞれの抵抗を格段に低減し、プローブ装置の実機として使用しても信頼性を十分に確保することができるパワーデバイス用のプローブカードを提供する。

【解決手段】本発明のプローブ装置10は、パワーデバイスSのエミッタ電極に電気的に接触する第1のプローブ11と、第1のプローブ11が接続されたブロック状の第1の接続端子12と、パワーデバイスDのゲート電極に電気的に接触する第2のプローブ13と、第2のプローブ13に接続されたブロック状の第2の接続端子14と、パワーデバイスDのコレクタ電極側に電気的に接触し得るコンタクトプレート15と、コンタクトプレート15に固定されたブロック状の第3の接続端子16と、を備え、第1、第2、第3の接続端子12、14、16は、それぞれが対応するテスタ側の接続端子に電気的に直に接触される。

(もっと読む)

半導体装置、半導体装置の検査方法及び製造方法

【課題】コンタクト周りのキラー欠陥検査を容易にするパターンを有する半導体装置、半導体装置の検査方法及び製造方法を提供する。

【解決手段】半導体基板の第1導電型領域の表面に設けられ、それぞれ第1の方向に延在する複数の第2導電型領域と、複数の第2導電型領域とそれぞれ複数の個所で交差することにより各第2導電型領域にソースとドレインが直列に接続された複数のMOSトランジスタを形成するゲート配線と、複数のMOSトランジスタとゲート配線との表面を覆う絶縁膜と、絶縁膜の表面から複数のMOSトランジスタのソースドレイン領域にそれぞれ設けられた複数の第1のコンタクトと、絶縁膜の表面からゲート配線の各領域に共通に接続された第2のコンタクトと、を有する。

(もっと読む)

検査装置

【課題】多チャンネル化された伝送線路を含んで構成されるシステムにおいて、スキュー補正を行うデータずれ補正装置およびデータずれ補正方法の提供。

【解決手段】1.初期状態のようにCH0(402a)が最初に到着し、CH1(402b)が遅れて到着し、最後にCH2(402c)の信号が到着する。2.第一遅延挿入のように、データ同期信号STROBEの立ち上がりエッジと各チャンネルのデータを同期させる第一遅延を挿入するが、CH0には遅延量410a分、CH1には遅延量ゼロ、CH2には遅延量410bである。第一遅延を加えたことによるライン同期信号および各チャンネルデータ間のずれを修正するため、3.第二遅延挿入に示すようにライン同期信号LINE_VALID(400)とCH0(402a)とCH1(402b)に、必要に応じて、チャンネルデータの1データを受信する時間を第二遅延量として、設定する。

(もっと読む)

多層配線基板の製造方法およびウエハ一括コンタクトボード

【課題】配線層が絶縁層を介して積層された多層配線基板の反り量が小さい多層配線基板及びその製造方法の提供。

【解決手段】絶縁層を介して複数の配線層を積層し、絶縁層に形成された開口部を介して複数の配線層を導通してなる多層配線基板の製造方法であって、ガラス基板51を用い、ガラス基板51の第1の表面に圧縮応力層40A、第2の表面に圧縮応力層40B、を形成する工程と、圧縮応力層40Aの表面上に第1配線パターン52aを形成する配線パターン形成工程と、第1配線パターン52a上に絶縁層53を形成する絶縁層形成工程と、絶縁層53に上下配線層を導通するための開口部54を形成する開口部形成工程と、配線パターン形成工程、及び、絶縁層形成工程、及び、開口部形成工程、を複数繰り返す工程を有し、ガラス基板51の第2の表面圧縮応力層40Bを所定の厚さ除去する圧縮応力層除去工程を有する。

(もっと読む)

高電圧試験方法

【課題】簡単な構成でウェハの高電圧試験において空気放電を防止できる高電圧試験方法を提供する。

【解決手段】電極パッド形成工程の後のレジストパターン形成工程において、互いに隣接するソース電極パッド3とドレイン電極パッド4との間の隙間領域上とその隙間領域の近傍のソース電極パッド3とドレイン電極パッド4の外縁領域上とを覆うように、かつ、互いに隣接するソース電極パッド3の露出部3aとドレイン電極パッド4の露出部4aの最短距離が予め設定された電極間距離よりも長くなるように、レジストパターン6を形成する。

(もっと読む)

プローブ針

【課題】

実施形態は、パッド部と接触容易なプローブ針を提供する。

【解決手段】

本実施形態のプローブ針100は、半導体装置の検査に用いられるプローブ針100であって、前記半導体装置内のパッドと接触する面を含む端子部10(10a、10b)と、前記端子部10(10a、10b)と一体に接続され、前記端子部を支持する支持部20とを備えることを特徴とする。

また、本実施形態のプローブ針100は、前記端子部20は第1の面及び第2の面を有し、前記第1の面は、前記第2の面と異なる方向に延びるようにしてもよい。

(もっと読む)

半導体試験装置のベースユニット

【課題】半導体試験装置のベースユニットにおいて、プローブカードが、高温測定時の熱等の影響によって被試験デバイス方向に変形することを防ぐ。

【解決手段】ベースユニット本体と、ベースユニット本体の下方向に配置され、ベースユニット本体に対する傾きを変更可能な、プローブカードを固着するユニットの上部に設けられ、下面の両側に斜面が形成されたテーパブロックと、ベースユニットの下部において、テーパブロックの傾斜方向に設けられたガイド沿って直線移動可能であり、テーパブロックを挟んで配置された1対の下部プレートとを備え、1対の下部プレートは弾性手段により互いに連結され、それぞれの下部プレートは、ガイドに対する停止手段と、テーパブロックの斜面と接触する位置に設けられ、移動方向に回転する回転手段とを備えているベースユニット。

(もっと読む)

半導体欠陥検査装置ならびにその方法

【課題】回路設計データを用いた半導体ウェーハ上の欠陥を自動的に検出し、欠陥発生原因の推定を行う半導体欠陥検査装置ならびにその方法を提供する。

【解決手段】回路設計データ1160から検査対象回路パターンと比較するために,欠陥発生要因毎に定められた形状変形項目について設計データに変形を加え,複数の形状を作成する(1192)。作成された形状群302と実パターンの比較により欠陥を検出する。また、それらの欠陥の発生原因を推定し,原因別に欠陥を分類する。

(もっと読む)

半導体試験装置、電気長測定方法

【課題】測定経路端を接地して電気長を測定する場合に、経路に断線があっても測定結果を得られるようにする。

【解決手段】測定経路端を接地して電気長を測定する半導体試験装置であって、測定経路に測定信号を出力する信号発生手段と、測定経路から分岐して入力される入力信号と、任意の閾値電圧とを比較する比較手段と、信号発生手段に測定信号を出力させ、比較手段の入力信号が第1閾値電圧以上となってから第2閾値電圧以下となるまでの時間を計測し、所定時間内に計測された場合には、計測された時間に基づいて測定経路の電気長を算出し、所定時間内に計測されなかった場合には、比較手段の入力信号が第1閾値電圧以上となってから、第1閾値電圧よりも高い第3閾値電圧以上となるまでの時間を計測して、測定経路の異常箇所までの電気長を算出する電気長測定制御手段とを備える。

(もっと読む)

121 - 140 / 5,556

[ Back to top ]