Fターム[4M118AA05]の内容

Fターム[4M118AA05]に分類される特許

41 - 60 / 2,039

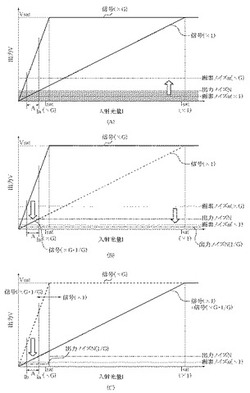

撮像システムおよび撮像システムの駆動方法

【課題】 S/N比の向上ならびにダイナミックレンジを拡大することのできる撮像システムを提供することを目的とする。さらに、これに適した撮像システムの駆動方法を提供することを目的とする。

【解決手段】 行列状に配列された複数の画素と、複数の画素の各列に設けられた列増幅部と、列増幅部で増幅されたことに基づく画像信号を出力する出力部と、を有する固体撮像素子と、画像信号を受ける信号処理部と、を備える撮像システムにおいて、列増幅部は、画素から出力される一の信号を1よりも大きいq倍のゲインで増幅し、信号処理部はq倍のゲインで増幅されたことに基づく画像信号に対して、1を下回る倍率をかける。

(もっと読む)

画像センサにおける複数ゲイン電荷感知

【課題】画像センサにおける複数ゲイン電荷感知を提供すること。

【解決手段】画像センサであって、該画像センサは、

入射光に応答して光電荷を蓄積するための感光性領域(PSR)のアレイと、

該PSRのうちの少なくとも1つと関連付けられている出力チャネルと

を備えており、該出力チャネルは、

光電荷を電圧に変換するための感知ノードと、

該感知ノードに接続されているキャパシタンス制御ユニットと、

該感知ノードに接続されており、第1の相互コンダクタンスを有している第1の増幅回路と、

該キャパシタンス制御ユニットに接続されており、該第1の相互コンダクタンスよりも大きい第2の相互コンダクタンスを有している第2の増幅回路と

を備えている、画像センサ。

(もっと読む)

光電変換装置及びその製造方法

【課題】 対象物に光を照射して応答を検出する際の検出感度の向上及びノイズの低減をはかる。

【解決手段】 不透明な配線層107,108を有する基板100上に、複数の発光素子200と複数の受光素子300を基板面内方向に離間して形成した光電変換装置であって、発光素子200及び受光素子300は基板100上に形成したバンク202,302の開口部にそれぞれ形成されている。発光層の半導体材料203〜205と受光層の半導体材料303,305とは異なり、発光素子200及び受光素子300の上部電極層207,307とは共通である。さらに、配線層107,108は、バンク202,302の開口部で規定される各領域の外側の領域に形成されている。

(もっと読む)

CCD画像センサにおける暗基準

【課題】光が暗基準領域に衝突することを防止しつつ、終結していない結合の不動態化を可能にして、画像における暗レベルの向上した較正を可能にするCCD画像センサを提供すること。

【解決手段】画像センサであって、該画像センサは、撮像アレイと、暗基準領域と、第1の実質的に不透明な光シールドと、第2の実質的に不透明な光シールドとを備え、該暗基準領域内において、該第1の光シールドにおける該開口部は、感光性エリアまたはVCCD領域の上に配置され、両方の上には配置されず、該第1の光シールドにおける該開口部が、感光性エリアの上に配置される場合、該暗基準領域における各感光性エリアは、該感光性エリアの上に2つ以上の開口部を有しておらず、該第1の光シールドにおける該開口部が、VCCD領域の上に配置される場合、該暗基準領域における各VCCD領域は、該VCCD領域の上に2つ以上の開口部を有していない、画像センサ。

(もっと読む)

MOS型固体撮像素子及び撮像装置

【課題】クロストークによる画質劣化を防止することができるMOS型固体撮像素子を提供する。

【解決手段】MOS型の固体撮像素子100は、半導体基板内に二次元状に配置形成されたN型不純物層からなる複数のフォトダイオード(PD)10と、各PD10で発生した電荷に応じた信号を読み出す半導体基板に形成された信号読み出し回路Cとを有する。PD10の行と行の間の境界領域、及び、PD10の列と列の間の境界領域の一方において、当該一方の境界領域の伸びる方向に信号読出し回路Cを構成するMOSトランジスタが配列され、2つの境界領域の他方におけるPD10同士の間の領域の半導体基板には、入射した光に応じて電荷を発生して当該電荷を蓄積するN型不純物層からなる電荷蓄積部11が形成されている。

(もっと読む)

光検出素子、光検出素子の制御方法

【課題】光電変換部での飽和の可能性を低減して光電変換部の小型化を可能にし、全体としてのサイズの小型化を可能にする。

【解決手段】分離電極14aと蓄積電極14bとが障壁制御電極14cを挟んで配置される。分離電極14aと蓄積電極14bと障壁制御電極14cとに正極性の電圧が印加されてウェル12にポテンシャル井戸が形成された状態で光照射による電子が集積される。その後、障壁制御電極14cに印加された電圧に応じて形成されるポテンシャル障壁の高さが調節されることにより、規定した一定量の不要電荷が電荷分離部で分離される。電子の集積と不要電荷の分離とが複数回繰り返された後、蓄電電極14bに対応して形成された電荷蓄積部に流れ込んだ有効電荷が受光出力として取り出される。

(もっと読む)

着色組成物、並びに、これを用いたカラーフィルタの製造方法、カラーフィルタ、及び、固体撮像素子

【課題】カラーフィルタの更なる薄膜化を達成すべく、着色剤を高濃度で含有しながらも、耐熱性に優れたカラーフィルタを製造可能な着色組成物を提供する。更に、上記着色組成物を用いたカラーフィルタの製造方法、カラーフィルタ、及び、固体撮像素子を提供する。

【解決手段】着色剤と樹脂とを含有する着色組成物であって、前記着色組成物の全固形分に対する前記着色剤の含有量が50質量%以上であり、かつ、前記樹脂の固形分酸価が80mgKOH/g超過である、着色組成物、及びこれを用いたカラーフィルタの製造方法、カラーフィルタ、及び、固体撮像素子。

(もっと読む)

固体撮像素子および製造方法、並びに電子機器

【課題】より良好な画素信号を得る。

【解決手段】固体撮像素子は、入射する光を電荷に変換する光電変換素子、および、光電変換素子により光電変換された電荷を一時的に保持する電荷保持部が形成された半導体基板と、少なくとも半導体基板の光電変換素子および電荷保持部の間の領域に延在するように埋め込まれる埋め込み部を有する遮光部とを備える。さらに、遮光部は、光電変換素子に光が入射する側である半導体基板の裏面側において、少なくとも電荷保持部を覆うように配置される蓋部をさらに有する。本技術は、例えば、裏面照射型のCMOSセンサに適用できる。

(もっと読む)

撮像装置及びその駆動方法

【課題】ランダムノイズの影響を低減した撮像装置を提供することを課題とする。

【解決手段】入射光に応じて発生した電荷を蓄積して信号を出力する複数画素の有効画素領域及び入射光に依存しない信号を出力する複数画素の非有効画素領域を含む画素部と、前記画素部の画素の列毎に設けられる複数の垂直信号線と、前記画素部の画素を行単位に走査して選択することにより前記選択された同一行の画素の信号を前記複数の垂直信号線に出力させる垂直走査回路と、前記複数の垂直信号線の信号を走査して選択することにより前記選択された垂直信号線の信号を出力させる水平走査回路とを有し、前記垂直走査回路は、1フレームの間に前記有効画素領域の同一行の画素を行単位で1回選択し、1フレームの間に前記非有効画素領域の同一行の画素を行単位で複数回選択することを特徴とする撮像装置が提供される。

(もっと読む)

撮像装置

【課題】1フレームの画像を撮像するための時間を長くすることなく、暗電流による画質劣化を低減する。

【解決手段】撮像装置は、互いに近接する第1及び第2の光電変換部PDA,PDBの組を複数有する撮像素子4と、前記各組の第1の光電変換部PDAを同時に一旦リセットしてから前記各組の第1及び第2の光電変換部PDA,PDBを露光した後に、前記各組の前記第1の光電変換部PDAをリセットすることなく前記各組の第2の光電変換部PDBを同時に一旦リセットした後、前記各組の第1及び第2の光電変換部PDA,PDBに蓄積された信号を読み出す制御を行う制御手段と、を備える。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能する第1導電型の半導体層11、チャネル領域を囲み、半導体層11に活性領域を定義する素子分離絶縁膜21、活性領域の一方に設けられた第2導電型の第1主電極領域62、活性領域の他方に設けられた第2導電型の第2主電極領域63、活性領域の表面のゲート絶縁膜22、多結晶シリコン層を含んで、ゲート絶縁膜22の上に設けられたゲート電極54を備える。多結晶シリコン層は、第1主電極領域62,第2主電極領域63に接する部分は第2導電型の第1多結晶シリコン領域54-2、チャネル領域と素子分離絶縁膜21との境界領域の上部は第1導電型の第2多結晶シリコン領域54-1である。

(もっと読む)

固体撮像装置

【課題】記憶部で発生するリーク電流の量を抑制した固体撮像装置を提供する。

【解決手段】前記固体撮像装置は、半導体基板70に配置される複数の画素部と、複数の記憶部と、垂直走査回路6とを備える。前記半導体基板70内には、第一導電型のウエル61が形成される。前記複数の記憶部の各々は、ウエル61に形成される書き込みトランジスタ31を有する。ウエル61と、書き込みトランジスタ31のソース又はドレインである第二導電型の前記拡散領域72とは接合される。垂直走査回路6は、前記記憶部に画素信号を記憶させるための記憶期間中に、ウエル61と前記拡散領域72との接合部の電界強度を低減させる所定電圧を、ウエル61に印加する。

(もっと読む)

画素をバーストリセット動作と統合することにより改善された性能を有するCMOSイメージセンサ

【課題】小型画素及び高性能CMOSイメージセンサアレイで使用することができる実質

的な画素設計を提供すること。

【解決手段】本発明のリセットトランジスタは、電荷を検出するフローティング拡散領域

と、電荷を排出する接合領域と、リセット信号の制御を受けて、前記フローティング拡散

領域から前記接合領域への電荷転送を制御するゲートと、該ゲートの下部に統合された電

位井戸とを備えることを特徴とする。

(もっと読む)

固体撮像素子

【課題】 暗電流の抑制や受光部の入射光量の増大により、得られる画像データ画質を改善した固体撮像素子を提供する。

【解決手段】 固体撮像素子1は、半導体から成る基板10と、基板10中に形成され光電変換によって生じた電荷を蓄積する基板とは逆の導電型の半導体から成る受光部11と、基板10上に設けられる絶縁層12と、絶縁層12上に設けられ受光部11が蓄積する電荷と同じ極性の固定電荷を有する固定電荷層13と、固定電荷層13上に設けられる反射防止層14と、基板10中の受光部11と隣接する位置に設けられ受光部11から読み出された電荷が一時的に蓄積される電荷転送部15と、少なくとも電荷転送部15の直上に設けられる転送電極16と、を備える。反射防止層14は、受光部11の直上の領域内に設けられる。

(もっと読む)

固体撮像素子および固体撮像装置

【課題】製造工程を増加させることなく、スミアシェーディングを抑制し、画質を向上させる。

【解決手段】画素領域にて行列状に配列される複数の電荷蓄積部3と、半導体基板11に設けられる電荷転送部13、および半導体基板11上に設けられる転送電極14を有する複数の垂直転送部と、電荷蓄積部3とこの電荷蓄積部3により生成された信号電荷が読み出される垂直転送部との間に設けられる読み出し部6と、電荷蓄積部3の読み出し部6が設けられる側と反対側にて電荷蓄積部3と垂直転送部との間に設けられるチャネルストップ部7と、半導体基板11の入射光が入射する側に設けられ、電荷蓄積部3に対応する位置に開口部を有する遮光膜16と、を備え、電荷蓄積部3、電荷転送部13、読み出し部6、およびチャネルストップ部7は、水平方向について、画素領域の中央部に対して画素領域の周辺部では、開口部に対して外側へずれた位置に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能向上を図ることができる技術を提供する。

【解決手段】層間絶縁膜を形成した後、マイクロ波アニールを実施する。このマイクロ波アニールによれば、シリコン結晶に共鳴吸収される周波数(5.8GHz)のマイクロ波を使用することにより、シリコン結晶の格子振動を直接誘起するため、例えば、400℃以下という低温においても、半導体基板の内部に形成されている結晶欠陥を回復させることができる。

(もっと読む)

固体撮像装置

【課題】 内部電界が弱い領域では、ホトダイオードPDより深い領域で発生した光電荷は横方向に拡散してしまい、隣接画素等への光電子流入(クロストーク)により感度低下が生じていた。

【解決手段】 クロスストーク防止層DNW9をホトダイオードPD形成部及び、画素−周辺回路間に設ける。

【効果】 画素−画素間または画素領域−周辺回路領域間のクロストークを低減し、光感度を向上させる。

(もっと読む)

カラー撮像素子

【課題】偽色の発生の抑圧及び高解像度化が可能な単板式のカラー撮像素子を提供する。

【解決手段】水平及び垂直方向に配列された光電変換素子からなる複数の画素上に、所定のカラーフィルタ配列のカラーフィルタが配設されてなる単板式のカラー撮像素子である。このカラー撮像素子のカラーフィルタ配列は、R、G、Bの全ての色のフィルタが、水平及び垂直方向の全ラインに配列された所定の基本配列パターンPを含み、この基本配列パターンPが水平方向及び垂直方向に繰り返して配置されている。特にGフィルタは、基本配列パターン内において、水平、垂直、及び斜め(NE,NW)方向の各方向(4方向)にそれぞれ2以上隣接する部分が含まれるように配置されており、これらの隣接するGフィルタに対応するG画素の画素値により、4方向の輝度の相関度を最小画素間隔で判断することができる。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、電子機器

【課題】ランダムノイズの低減が図られた固体撮像装置を提供することを目的とする。また、その固体撮像装置を備えることにより、画質の向上が図られた電子機器を提供することを目的とする。

【解決手段】増幅トランジスタTraのドレイン側では、高濃度不純物領域28のみでドレイン領域38を構成し、ソース側では、増幅ゲート電極22側に形成され、ドレイン領域38を構成する高濃度不純物領域28よりも不純物濃度が低い低濃度不純物領域29からなるソース領域32を構成する。ドレイン領域38において、低濃度不純物領域を形成しないことで、実効ゲート長Leffを長くできる。また、増幅ゲート電極22のソース側では、増幅ゲート電極22側に低濃度不純物領域29が形成されるため、基板表面のポテンシャル変動を抑えることができる。

(もっと読む)

固体撮像素子および電子機器

【課題】画質の低下を回避する裏面照射型のCMOS型固体撮像素子を提供する。

【解決手段】固体撮像素子21は、受光した光を電気信号に変換するPD32が平面的に配置された半導体基板42と、半導体基板42に入射する光の透過を制御するシャッター層44とを備えて構成される。そして、半導体基板42とシャッター層44との間の間隔が、シャッター層44に形成されるシャッター素子33の間隔以下に設定される。また、シャッター層44は、PD32に対する光の入射角に応じて、光を遮光する箇所を調整する。

(もっと読む)

41 - 60 / 2,039

[ Back to top ]