Fターム[4M118EA01]の内容

Fターム[4M118EA01]の下位に属するFターム

Fターム[4M118EA01]に分類される特許

61 - 80 / 2,074

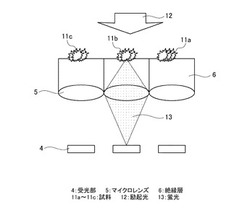

イメージセンサ及びその製造方法並びに検査装置

【課題】集光効率が高く、かつ画素間のクロストークが少ないイメージセンサ及びその製造方法並びに検査装置を提供する。

【解決手段】複数の受光素子を備え、入射した光を電気信号に変換する光源変換部と、各受光素子の直上域に配置され、その直下に位置する受光素子に向けて光を集光する複数のレンズと、このレンズ上に形成され、光透過材料からなる絶縁層とを備えるイメージセンサにおいて、絶縁層の表面に、受光素子毎にそれぞれ離間して形成され、その中心が、各受光素子の受光部の中心とその直上に配置されたレンズの中心とを結んだ線の延長線上に位置する検出領域を設ける。そして、検出対象の試料を、少なくともこの検出領域に固定する。

(もっと読む)

放射線検出器、放射線検出器の製造方法、及び放射線画像撮影装置

【課題】光電変換素子の静電破壊を防止することができると共に、画像がぼけやすくなるのを防ぐことができる。

【解決手段】放射線検出器10Aは、基板1上に形成されたTFTスイッチ4と、基板1上に形成され、照射された光に応じた電荷を発生する光電変換素子としての半導体層6と、半導体層6上に形成され、一部に帯電防止性を有する遮光部材32が形成された平坦化層34と、平坦化層34上に形成され、照射された放射線に応じた光を発生するシンチレータ70と、を備える。

(もっと読む)

光電変換基板、放射線検出器、及び放射線画像撮影装置

【課題】光電変換素子の静電破壊を防止する共に、帯電防止膜を設けたことによる副作用を防止することができる、光電変換基板、放射線検出器、及び放射線画像撮影装置光電変換素子の静電破壊を防止する。

【解決手段】基板1上に形成されたTFTスイッチ4及びセンサ部103の上面が平坦化層18により平坦化されており、当該平坦化層18の略全面(本実施の形態では画素領域20Aの全面)に帯電防止機能を有する導電膜30が形成されている。導電膜30は、接続配線42により接続部44に接続されており、接続部44は、接続配線42を共通電極配線25を介してバイアス電源110またはグランドに接続するように構成されている。また、光電変換基板60(導電膜30)の上には、シンチレータ70が形成されており、シンチレータ70は、光電変換基板60に近い方から非柱状部71及び柱状部72を備えている。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置、固体撮像装置の製造方法、電子機器

【課題】MOSトランジスタのサイズを変えることなく、ノイズの低減が図られた半導体装置とその製造方法を提供することを目的とする。また、そのMOSトランジスタを備えることにより、ノイズの低減が図られた固体撮像装置とその製造方法を提供することを目的とする。

【解決手段】埋め込みチャネル型のMOSトランジスタにおいて、素子分離部24側に接する領域に、斜め方向からのイオン注入により形成した第1の不純物拡散領域14aと、ゲート電極26下の領域全面に形成した第2の不純物拡散領域14bとによりチャネル領域14を構成する。第1の不純物拡散領域14aの形成により、チャネル領域14の素子分離部24側で発生する不純物濃度の低下分を補填でき、実効ゲート幅の拡大が可能となる。

(もっと読む)

固体撮像装置および固体撮像装置の製造方法

【課題】電荷の転送効率を向上させることができる固体撮像装置を提供すること。

【解決手段】固体撮像装置10は、第1の不純物層23、第2の不純物層24、第3の不純物層25、およびゲート電極28、を具備する。第1の不純物層23は、半導体基板11に一定の深さを有するように形成され、照射された光に応じて電荷を発生させる。第2の不純物層24は、第1の不純物層23の表面に、所定の方向に向かって深さが浅くなるように形成される。所定の方向は、第1の不純物層23から第3の不純物層25に向かう方向である。第3の不純物層35は、半導体基板11の表面において、第1の不純物層23および第2の不純物層24と離間した位置に形成され、第1の不純物層23で発生した電荷を電圧に変換する。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び、電子機器

【課題】飽和電荷量の向上が可能な固体撮像素子を提供する。

【解決手段】半導体基体51の表面51A側に形成された第1フォトダイオードPD1と、裏面51B側に形成された第2フォトダイオードPD2を備える。そして、第2フォトダイオードPD2を構成する第1導電型半導体領域59と第2導電型半導体領域58との接続面の不純物濃度が、第2導電型半導体領域58の第1導電型半導体領域59と反対側の層との接続面の不純物濃度以上である固体撮像素子50を構成する。

(もっと読む)

半導体装置とその駆動方法

【課題】1フレーム期間以上のデータの保持が可能であり、少ない素子数で差分演算を行うことができるイメージセンサを提供する。

【解決手段】マトリクス状に配置された複数の画素にフォトセンサを設け、該画素は1フレーム期間以上にわたってデータ保持部に電荷を蓄積し、該データ保持部に蓄積された電荷によってフォトセンサの出力を変化させる。データ保持部の書き込みスイッチ素子としては、リーク電流の小さい(1×10−14Aより十分に小さい)トランジスタを用いる。リーク電流の小さいトランジスタとしては、酸化物半導体層にチャネルが形成されるトランジスタが挙げられる。

(もっと読む)

光電変換装置の製造方法

【課題】 光電変換素子に対するマイクロレンズの位置が高精度に制御された光電変換装置を提供する。

【解決手段】 半導体ウエハ1000の活性領域110を画定する分離領域120を形成する工程(S1)と、分離領域120によって画定された活性領域120に光電変換素子130を形成する工程(S4)と、光電変換素子130の上にマイクロレンズ600を形成する工程(S16)と、を有し、光電変換素子130を形成する工程(S4)におけるアライメント(A4)およびマイクロレンズ600を形成する工程(S16)におけるアライメント(A16)を、分離領域110を形成する工程(S1)で形成されたアライメントマーク(AM1)を基準にして行う。

(もっと読む)

集積回路構造及び裏面照射型イメージセンサデバイス

【課題】裏面照射(BSI)型イメージセンサチップのパッド構造を提供する。

【解決手段】前面及び背面を含む半導体基板、前記半導体基板の前記前面に配置される低k誘電体層、前記低k誘電体層に配置される非低k誘電体層、前記非低k誘電体層に配置される金属パッド、前記半導体基板の背面から延伸し、前記半導体基板、前記低k誘電体層、及び低k誘電体層を貫通し、前記金属パッドの表面を露出する開口、及び前記開口の側壁及び底部上に形成され、前記開口の底部は、前記金属パッドの前記露出された表面を部分的に覆う保護層を含む集積回路構造。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

撮像装置、撮像システムおよび撮像装置の製造方法

【課題】 遮光膜で反射した光の影響を低減する。

【解決手段】 遮光膜40の上面41は銀色を呈する材料で構成されており、第1膜10が遮光膜40の上面41に近接して遮光膜40と通過部44を覆い、第1膜10の屈折率とは異なる屈折率を有する第2膜20が、光路部45および通過部44に位置するとともに第1膜10と界面200を成しており、界面200と光電変換部2との距離D3が、通過部44の出射端442と光電変換部2との距離D2よりも大きい。

(もっと読む)

半導体装置、電子機器、及び、半導体装置の製造方法

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置1を、接合界面Sj側の表面に形成された第1金属膜16を有する第1半導体部10と、接合界面Sjで第1金属膜16と接合された第2金属膜26を有する第2半導体部20と、界面バリア部28とを備える構成とする。第2金属膜26の接合界面Sj側の表面面積は第1金属膜16の接合界面Sj側の表面面積より小さくする。そして、第1金属膜16の接合界面Sj側の面領域のうち第2金属膜26と接合しない面領域を含む領域に界面バリア部28を設ける。

(もっと読む)

固体撮像装置およびその製造方法、並びに電子情報機器

【課題】半導体基板の、光電変換素子が形成された一方の面とは反対側の他方の面から入射した光を一方の面に形成した反射膜により効率よく反射させることができ、これにより感度向上した固体撮像装置を実現する。

【解決手段】固体撮像装置100aにおいて、第1導電型の半導体基板100内に形成され、入射光の光電変換により信号電荷を生成する光電変換素子PD1およびPD2と、該半導体基板100の第1主面上に形成され、該光電変換素子PD1およびPD2で生成された信号電荷を転送する転送トランジスタTt1およびTt2とを備え、該転送トランジスタのゲート電極107を、該光電変換素子を構成する電荷蓄積領域102の第1主面側の表面を覆うよう形成し、該転送ゲート電極107をポリシリコン層107aとその表面を覆う高融点金属シリサイド層からなる反射膜107bにより構成した。

(もっと読む)

固体撮像装置

【課題】 隣接画素間でのクロストークを防止して、混色の発生を防止でき、再生画面上での色再現性の向上に対して有利な固体撮像装置を提供する。

【解決手段】 半導体基板404に、光電変換部及び信号走査回路部を含み単位画素行列を配置して成る撮像領域を具備し、撮像領域は、隣接する単位画素との境界部分に対応して各単位画素を囲むように設けられる素子分離絶縁膜408を備え、素子分離絶縁膜は、信号走査回路部が形成される半導体基板の表面から半導体基板中にオフセットされて設けられ且つ半導体基板の裏面に達している。

(もっと読む)

マイクロレンズの製造方法および露光用マスク

【課題】固体撮像素子に設けるマイクロレンズを、隣接するマイクロレンズとのギャップを狭くして高い集光性能を与えるとともに、各マイクロレンズの形状が均一になるように形成する製造方法を提供すること。

【解決手段】固体撮像素子10におけるマイクロレンズ7の製造方法であって、マイクロレンズを構成する第一の層81を設けた後に、マイクロレンズを構成する第二の層85を、第一の層とは異なる形状で第一の層に積層して設け、その後両層を熱処理して一体化することにより、所望の形状のマイクロレンズを形成する工程を含み、第一の層の形状が、各画素の中央から画素境界に向かう放射状パターンを含み、第二の層の形状が、多角形状の各画素の形状に近く、画素境界を越えない凸図形パターンである。

(もっと読む)

改善されたカラークロストークを有するイメージセンサ

【課題】改善されたカラークロストークを有する、小型ピクセルを有するイメージセンサ

を提供すること。

【解決手段】本発明のイメージセンサは、第1導電型の基板と、該第1導電型の基板にア

レイされた第1ピクセル及び第2ピクセルと、該第2ピクセルに該当する前記基板内には

配置されることなく、前記第1ピクセルに該当する前記基板内に配置されたポテンシャル

障壁とを備える。ここで、前記第2ピクセルは、前記第1ピクセルに対応するカラーより

も相対的に長波長を有するカラーに対応するものである。また、前記ポテンシャル障壁は

、高エネルギーのイオン注入によるドーパントを有し、前記P型エピタキシャル層のエピ

タキシャル成長中にイオンの注入又は拡散により形成されたドーパントを有する。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】周辺領域に配線を設けた裏面照射型の固体撮像装置において、画素領域における絶縁膜の薄膜化を図ることにより光電変換部での受光特性の向上を図る。

【解決手段】光電変換部20が配列形成された画素領域4を有するセンサ基板2と、センサ基板2の受光面Aとは逆の表面側に設けられた駆動回路と、センサ基板2における受光面A上に設けられ、画素領域4の膜厚が周辺領域7の膜厚よりも薄い段差構造を有する絶縁層14と、受光面A側における周辺領域7に設けられた配線8と、絶縁層14上に光電変換部20に対応して設けられたオンチップレンズ19とを備えた固体撮像装置1-1である。

(もっと読む)

赤外線検知器及び赤外線検知器の製造方法

【課題】2波長赤外線イメージセンサにおいて、同じ画素ピッチにおける画素面積を広くする。

【解決手段】共通コンタクト層の一方の面に積層形成された第1の赤外光吸収層及び第1のコンタクト層と、前記共通コンタクト層の他方の面に積層形成された第2の赤外光吸収層及び第2のコンタクト層と、前記第2の赤外光吸収層及び前記第2のコンタクト層を分離する上側画素分離溝と、前記共通コンタクト層を介し、前記上側画素分離溝に対応する位置に形成された前記第1の赤外光吸収層及び前記第1のコンタクト層を分離する下側画素分離溝と、前記上側画素分離溝及び前記下側画素分離溝により分離された各々の画素ごとに、前記第2のコンタクト層、前記第2の赤外光吸収層、前記共通コンタクト層、前記第1の赤外光吸収層を除去することにより形成されたコンタクト穴と、を有することを特徴とする赤外線検知器により上記課題を解決する。

(もっと読む)

固体撮像素子

【課題】出力ムラの発生を抑制し、低スミアの固体撮像素子を提供する。

【解決手段】半導体基板に設けられた受光部と、半導体基板に設けられた転送チャネルと、受光部を垂直方向に挟むように配置され、水平方向に延びるように設けられた第1の転送電極と、転送チャネルの上に配置され、隣接する前記第1の転送電極間に挟まれるように配置された第2の転送電極と、第1の転送電極の上に配置され、複数の第2のコンタクトを介して第1の転送電極と接続する第2の遮光膜と、第2の転送電極の上に配置され、複数の第1のコンタクトを介して第2の転送電極と接続する第1の遮光膜とを有し、第1の遮光膜には、第1の転送電極の上において、第1の開口部と第2の開口部が設けられており、第1の開口部には、第2のコンタクトが配置されており、第2の開口部には、第2のコンタクトが配置されていないことを特徴とする固体撮像素子を提供する。

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器

【課題】装置の信頼性や、製品の歩留まりなどを向上させる。

【解決手段】第1の開口と第2の開口との内部に金属材料を埋め込んで第1プラグと第2プラグとを設けると共に、第1プラグと第2プラグとの間を接続する接続配線を設けることで、接続導電層を形成する。そして、接続導電層において接続配線の上面を被覆するようにパッシベーション膜を形成する。このパッシベーション膜の形成工程では、高密度プラズマCVD法などのように埋め込み性に優れた成膜法で、SiO2などの絶縁膜を成膜することによって、パッシベーション膜を形成する。

(もっと読む)

61 - 80 / 2,074

[ Back to top ]