Fターム[4M118EA01]の内容

Fターム[4M118EA01]の下位に属するFターム

Fターム[4M118EA01]に分類される特許

41 - 60 / 2,074

メモリ用シフトレジスタ

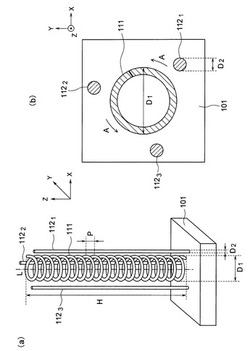

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

固体撮像素子の製造方法

【課題】歩留まりを向上させることができる固体撮像素子の製造方法を提供する。

【解決手段】本発明は、基板に画素電極と、入射光に応じた電荷を生成する有機膜を有する光電変換部と、透明な対向電極と、封止層とが形成された固体撮像素子の製造方法である。基板の画素電極が設けられた側表面にメタルマスクを磁力で密着させる工程と、基板の画素電極が設けられた側表面に、有機物を蒸着し、有機膜を形成する工程と、有機膜形成後、メタルマスクを取り外す工程と、有機膜上に対向電極を形成する工程と、対向電極を覆う封止層を形成する工程とを有する。メタルマスクは、ハーフエッチングが施されており、このハーフエッチングが施された側を画素電極に向けて密着されている。

(もっと読む)

撮像素子、撮像装置、並びに、製造装置および方法

【課題】黒レベルの基準値の検出をより正確に行うことができるようにする。

【解決手段】本開示の撮像素子は、有効画素領域の画素値の黒レベルの基準値を検出するための領域であり、半導体基板外部からの光が遮光膜により遮光されるオプティカルブラック画素領域に、前記オプティカルブラック画素領域の前記半導体基板内部に存在する電荷を、前記オプティカルブラック画素領域の外部に伝送する伝送路領域を備える。本開示は撮像素子、撮像装置、並びに、製造装置および方法に適用することができる。

(もっと読む)

固体撮像装置

【課題】フォトダイオードの縦方向の微細化を図る。

【解決手段】実施形態に係わる固体撮像装置は、光の入射側の第1の面及びそれと反対側の第2の面を有する半導体基板11と、半導体基板11内のフォトダイオード12と、半導体基板11の第1の面側においてフォトダイオード12の全体を覆い、半導体基板11の外側から内側に向かう光を透過し、半導体基板11の内側から外側に向かう光を反射する機能を有する機能層13と、半導体基板11の第2の面の全体を覆い、半導体基板11の内側から外側に向かう光を反射する機能を有する反射層14とを備える。

(もっと読む)

光電変換基板、放射線検出器、及び放射線画像撮影装置

【課題】本発明は上記問題点を解決するために成されたものであり、光電変換素子の静電破壊を防止することができると共に、導電体を任意の電圧に設定することができる、光電変換基板、放射線検出器、及び放射線画像撮影装置を提供する。

【解決手段】基板1上に形成されたTFTスイッチ4及びセンサ部103の上面が平坦化層18により平坦化されており、当該平坦化層18の略全面に帯電防止機能を有する導電膜30が形成されている。導電膜30は、接続配線52と一体的に形成されており、切替部54に接続されている。また、切替部54は、制御装置106から入力される制御信号に応じて、接続配線52の接続先を、バイアス電源110、内部電源56、及びグランドのいずれかに切り替える。光電変換基板60の上には、シンチレータ70が形成されており、シンチレータ70は、光電変換基板60に近い方から非柱状部71及び柱状部72を備えている。

(もっと読む)

プラズマ損傷からフォトダイオードを保護するCMOSイメージセンサの製造方法

【課題】暗電流の原因となるプラズマ損傷や感光膜除去工程による重金属汚染を防止する

ことのできるCMOSイメージセンサのフォトダイオードの製造方法を提供すること。

【解決手段】本発明のCMOSイメージセンサの製造方法は、所定の工程が完了した基板

を用意するステップと、該基板のフォトダイオードの形成される領域の上部にパターニン

グされたブロック層を形成するステップと、該パターニングされたブロック層を残した状

態で、前記フォトダイオードの形成される領域を除く残りの領域に対して、マスクを用い

たイオン注入を行うステップと、前記マスクを除去するステップとを含む。

(もっと読む)

固体撮像素子および製造方法、並びに電子機器

【課題】より良好な画素信号を得る。

【解決手段】固体撮像素子は、入射する光を電荷に変換する光電変換素子、および、光電変換素子により光電変換された電荷を一時的に保持する電荷保持部が形成された半導体基板と、少なくとも半導体基板の光電変換素子および電荷保持部の間の領域に延在するように埋め込まれる埋め込み部を有する遮光部とを備える。さらに、遮光部は、光電変換素子に光が入射する側である半導体基板の裏面側において、少なくとも電荷保持部を覆うように配置される蓋部をさらに有する。本技術は、例えば、裏面照射型のCMOSセンサに適用できる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガスを用いた酸化シリコン膜で形成する。

(もっと読む)

裏面照明ピクセルアレイの動作方法

【課題】光を感知するピクセル面積量が減少することがなく、低照度性能が低下することがないイメージセンサを提供する。

【解決手段】裏面照明(「BSI」)イメージセンサピクセル(400)は、フォトダイオード領域(420)と、ピクセル回路(430)とを含む。フォトダイオード領域は、BSIイメージセンサピクセルの裏面上に入射する光に応答してイメージ電荷を蓄積するために半導体ダイ内に配置される。ピクセル回路が、半導体ダイの前面とフォトダイオード領域との間で半導体ダイ内に配置されたトランジスタピクセル回路を含む。ピクセル回路の少なくとも一部はフォトダイオード領域に重なり合っている。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】画素間においての混色を防止することが可能で、これにより撮像特性の向上が図られた固体撮像装置を提供することを目的とする。

【解決手段】固体撮像装置1-1は、半導体層30と、半導体層30の内部に半導体層30の表面に対して2次元的に配列されたn+型(第1導電型)の電荷蓄積領域31とを備えている。さらに半導体層30の内部には、半導体層30の表面から電荷蓄積領域31までの深さにわたってp+型(第2導電型)の界面領域37が設けられている。特に、電荷蓄積領域31を囲む位置には、界面領域37に対してp型不純物が追加で導入されたp++型の高濃度領域39が電荷移動防止領域として設けられている。

(もっと読む)

光電変換装置及び撮像システム

【課題】既存のCMOS形成製造方法を用いながら、撮像性能向上に寄与するPD形成用ウエル構造を実現する。

【解決手段】光を信号電荷に変換する光電変換領域を含む画素と、該画素が形成された画素領域外に、前記信号電荷を処理するための回路を含む周辺回路が同一基板上に配置された光電変換装置において、前記基板に形成された第一導電型の第1の半導体領域と前記信号電荷と同導電型である第二導電型の第2の半導体領域を含んで前記光電変換領域が形成され、第一導電型の第3の半導体領域を含んで前記周辺回路が形成されており、前記第1の半導体領域の不純物濃度は前記第3の半導体領域の不純物濃度よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】歩留まりの向上、およびコスト削減を図る。

【解決手段】半導体装置は、デバイス基板600と、前記デバイス基板上に接合された支持基板200と、を具備する。前記デバイス基板は、前記支持基板との接合面側の外周部に溝50を有する。

(もっと読む)

固体撮像素子および電子機器

【課題】画質の低下を抑制する。

【解決手段】センサチップは、複数のPDが配置された半導体基板を有している。信号処理チップは、センサチップに積層され、センサチップを駆動するためのロジック回路が形成された半導体基板を有している。そして、センサチップの半導体基板と、信号処理チップの半導体基板との間に、信号の送受信を行う配線を有する配線層が配置されており、その配線層において配線が形成されていない領域に、遮光性を備えた遮光膜が配設される。本技術は、例えば、裏面照射型のCMOS型固体撮像素子に適用できる。

(もっと読む)

固体撮像素子及び固体撮像素子の実装構造

【課題】外部回路や載置部材などのコストや準備期間を容易に削減することが可能な固体撮像素子及び固体撮像素子の実装構造を提供すること。

【解決手段】固体撮像素子IS1は、光感応領域3を有する半導体基板1と、半導体基板1の主面1a上に配列された複数の第一電極パッド10と、半導体基板1の主面1a上に、複数の第一電極パッド10が配列された方向に沿う方向に配列された複数の第二電極パッド12と、複数の第一電極パッド10と複数の第二電極パッド12とを1対1に接続する複数の配線14と、を備えている。複数の配線14は、複数の第一及び第二電極パッド10,12の配列方向に直交する中心線lに対して線対称となる位置関係にある第一電極パッド10と第二電極パッド12とを接続している。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能向上を図ることができる技術を提供する。

【解決手段】層間絶縁膜を形成した後、マイクロ波アニールを実施する。このマイクロ波アニールによれば、シリコン結晶に共鳴吸収される周波数(5.8GHz)のマイクロ波を使用することにより、シリコン結晶の格子振動を直接誘起するため、例えば、400℃以下という低温においても、半導体基板の内部に形成されている結晶欠陥を回復させることができる。

(もっと読む)

光電変換素子、固体撮像素子、撮像装置、光電変換素子の製造方法

【課題】有機材料を含む受光層を有する光電変換素子において、受光層の材料の選択幅を狭めることなく、光電変換素子の耐熱性を向上させること。

【解決手段】基板101上に酸化膜で構成された絶縁膜102が形成され、当該絶縁膜102上に並べて形成された複数の画素電極104と、複数の画素電極104の上にこれらを覆って形成された有機材料を含む受光層107と、受光層107上に形成された対向電極108とを有する固体撮像素子であって、画素電極104が、酸化窒化チタンで構成され、受光層107を形成する直前における画素電極104の組成が、(1)画素電極104全体に含まれる酸素量がチタン量の75atm%以上、又は、(2)画素電極104の基板101側から10nmまでの範囲或いは画素電極104の基板101側から画素電極104厚みの2/3までの範囲において、酸素量がチタン量の40atm%以上の条件を満たしている。

(もっと読む)

放射線検出器、放射線検出器の製造方法、及び放射線画像撮影装置

【課題】光電変換素子の静電破壊を防止することができると共に、発光層と光電変換基板との密着性を向上させることができる。

【解決手段】放射線検出器10Aは、基板1上に形成されたTFTスイッチ4と、基板1上に形成され、照射された光に応じた電荷を発生する光電変換素子としての半導体層6と、半導体層6上に形成された平坦化層34と、平坦化層34上に形成されたメッシュ状の帯電防止層32と、平坦化層34及び帯電防止層32上に形成され、照射された放射線に応じた光を発生するシンチレータ70と、を備える。

(もっと読む)

熱型光検出器、熱型光検出装置、電子機器および熱型光検出器の製造方法

【課題】測定する波長帯域を広く設定できる熱型光検出器を提供する。

【解決手段】シリコン基板10と、シリコン基板10上に形成され凹部30を有するスペーサー部材20と、スペーサー部材20の凹部30に向き合いスペーサー部材20に支持される支持部材40と、支持部材40上に形成され熱を検出する焦電型の赤外線検出素子60と、を含み、凹部30は、底面にスペーサー部材20の厚み方向に対して交差する方向に形成された第1平面31と、底面と支持部材40との間に、スペーサー部材20の厚み方向に対して交差する方向に形成された第2平面32と、を備え、第1平面31および第2平面32に光を反射する反射膜36が形成されている。

(もっと読む)

光電変換基板、放射線検出器、放射線画像撮影装置、及び放射線検出器の製造方法

【課題】光電変換素子の静電破壊を防止することができる、光電変換基板、放射線検出器、放射線画像撮影装置、及び放射線検出器の製造方法を提供する。

【解決手段】基板1上に形成されたTFTスイッチ4及びセンサ部103の上面が平坦化層18により平坦化されており、当該平坦化層18の略全面に帯電防止機能を有する導電膜30が形成されている。導電膜30は、グランド配線32及びグランド接続端子34と一体的に形成されており、グランド接続端子34を介してグランドに接続可能に構成されている。また、光電変換基板60(導電膜30)の上には、シンチレータ70が形成されており、シンチレータ70は、光電変換基板60に近い方から非柱状部71及び柱状部72を備えている。導電膜30をグランド接続端子34を介してグランドに接続した状態で、光電変換基板60の表面に表面処理を施す。

(もっと読む)

固体撮像素子用半導体基板及びそれを用いた固体撮像素子の製造方法

【課題】 固体撮像素子を製造するために適用した場合、製造後の固体撮像素子に終点検出部が残存せず、半導体素子部への拡散等の問題もなく、高精度の薄膜化を実現することが可能な固体撮像素子用半導体基板を提供する。

【解決手段】 素子部形成領域となる表面側の表層部を残す裏面側からのバック加工が適用される固体撮像素子用半導体基板であって、

前記素子部形成領域となる表面側の表層部と、この表層部より裏面側方向内部に形成され、BMD密度が1×1010/cm3以上1×1012/cm3以下の前記バック加工が適用される第1のバルク層と、この第1のバルク層より裏面側方向内部に形成され、前記第1のバルク層よりBMD密度が低く、その密度が1×109/cm3以上1×1010/cm3以下の前記バック加工が適用される第2のバルク層とを備えることを特徴とする固体撮像素子用半導体基板。

(もっと読む)

41 - 60 / 2,074

[ Back to top ]