Fターム[4M119AA11]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | 高集積化,微細化 (354)

Fターム[4M119AA11]に分類される特許

21 - 40 / 354

不揮発性半導体記憶装置

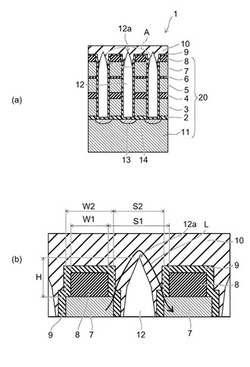

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】磁壁移動型MRAMのメモリセルの面積を低減する。

【解決手段】メモリセル200−1が、固定層11と磁気記録層21とリファレンス層41とトンネルバリア膜31とMOSトランジスタ51とを備えており、メモリセル200−2が、固定層13と磁気記録層22とリファレンス層42とトンネルバリア膜32とMOSトランジスタ52とを備えている。固定層11、13は、第1方向に固定された磁化を有している。第1方向と反対の第2方向に固定された磁化を有する固定層12が磁気記録層21、22に接合されている。固定層12と共通ビット線CBLとが、それらの間の電気的接続が分離不能であるように接続される。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

コバルト薄膜およびその形成方法ならびにナノ接合素子およびその製造方法ならびに配線およびその形成方法

【課題】厚さが35nm以下でも十分に高い保磁力および角型比を有する磁性のコバルト薄膜を得ることができるコバルト薄膜の形成方法およびこの方法により形成したコバルト薄膜を用いたナノ接合素子を提供する。

【解決手段】ポリエチレンナフタレート基板11上に真空蒸着法などによりコバルト薄膜12を35nm以下の厚さに成膜する。こうしてポリエチレンナフタレート基板11上にコバルト薄膜12を成膜した積層体を二つ用い、これらの二つの積層体をそれらのコバルト薄膜12のエッジ同士が、必要に応じて有機分子を挟んで、互いに対向するように交差させて接合することによりナノ接合素子を構成する。このナノ接合素子により不揮発性メモリや磁気抵抗効果素子を構成する。ポリエチレンナフタレート基板11の代わりに、少なくとも一主面がSiO2 からなる基板、例えば石英基板を用いてもよい。

(もっと読む)

記憶装置及びその製造方法

【課題】多値化にあたり素子構造及び製造工程の簡素化を達成する。

【解決手段】記憶装置は、第1信号線、第2信号線、トランジスタ、第1記憶領域、第2記憶領域、を備える。トランジスタは、第1、第2信号線間を流れる第1方向及びこれと反対の第2方向の電流の導通を制御する。第1記憶領域は、第1信号線とトランジスタの一方端とのあいだに接続される。第1記憶領域は、第1の平行閾値以上の電流が第1方向に流れると磁化の向きが平行になり、第1の反平行閾値以上の電流が第2方向に流れると反平行になる第1磁気トンネル接合素子を有する。第2記憶領域は、第2信号線とトランジスタの他方端とのあいだに接続される。第2記憶領域は、第1の平行閾値よりも大きな第2の平行閾値以上の電流が第2方向に流れると平行になり、第1の反平行閾値よりも大きな第2の反平行閾値以上の電流が第1方向に流れると反平行になる第2磁気トンネル接合素子を有する。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

記憶装置及びその製造方法

【課題】磁気トンネル接合素子を用いた構造において、製造工程の簡素化を達成することができる記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、第1信号線と、第2信号線と、トランジスタと、記憶領域と、導通領域と、を備える。トランジスタは、第1信号線と、第2信号線と、のあいだを流れる第1方向の電流及びこれと反対の第2方向の電流の導通を制御する。記憶領域は、第1信号線と、トランジスタの一方端と、のあいだに接続され、第1の平行閾値以上の電流が第1方向に流れると磁化の向きが平行になり、第1の反平行閾値以上の電流が第2方向に流れると磁化の向きが反平行になる第1磁気トンネル接合素子を有する。導通領域は、第2信号線と、トランジスタの他方端と、のあいだに接続される。

(もっと読む)

結晶性化合物及びこれを用いた可変抵抗素子並びに電子デバイス

【課題】磁気抵抗効果の大きい新たな可変抵抗素子を提供する。

【解決手段】本発明による可変抵抗素子は、次の3つの特徴を備えた結晶性化合物を含む。第1の特徴は、トポロジカル誘電体特性を示すことにより、伝導帯と価電子帯がディラックコーンを形成する点である。第2の特徴は、ディラックコーンを構成する伝導帯の谷と価電子帯の山との間に、バンドギャップが形成される点である。第3の特徴は、異なるスピンが入る二つのバンドがΓポイントを中心に時間反転対称を持つことである。これら3つの特徴を全て備えることにより、著しい磁気抵抗効果が発現する。

(もっと読む)

プラズマエッチング方法

【課題】CO含有プラズマの条件によらず、安定してクリーニングプラズマを生成する方法を提供する。

【解決手段】被エッチングウェハ802上に形成された磁性膜を、真空容器801内に導入されたCとOの元素を含むCO含有ガスにソース電力を印加することでCO含有ガスをプラズマ化し、生成したCO含有プラズマを用い加工する際に、該CO含有プラズマにて被エッチングウェハ802上に形成された磁性膜に所定の加工を施した後、ソース電力806を印加したまま、クリーニングガスを導入し、その後CO含有ガスの導入を停止することで、所定のクリーニングガスを用いたクリーニングプラズマを生成する。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】磁壁移動型MRAMのメモリセルの面積を小さくする。

【解決手段】磁気ランダムアクセスメモリが、メモリセルC1〜C3が形成されたメモリセルライン1と、書き込みビット線12−1〜12−4とを具備する。メモリセルライン1は、磁気記録層4と、磁化固定層3−1〜3−4と、リファレンス層6−1〜6−3と、スペーサ層5−1〜5−3と、nMOSトランジスタ2−1〜2−4とを備えている。スペーサ層5−iとリファレンス層6−iとは、磁化固定層3−iと磁化固定層3−(i+1)の間に位置している。磁化固定層3−1、3−3と、磁化固定層3−2、3−4は、互いに逆の方向に固定された磁化を有している。リファレンス層6−1〜6−3も、固定された磁化を有している。nMOSトランジスタ2−iは、書き込みビット線12−iと磁化固定層3−iの間に設けられている。

(もっと読む)

スイッチング磁界の改善された分散を伴う磁気ランダムアクセスメモリセル

【課題】従来のMRAMセルに比べて向上された切替効率とより低い電力消費と切替磁場の改善された分散を呈するMRAMセルを提供する。

【解決手段】磁気トンネル接合2が、第1強磁性層21、所定の高温閾値の下で第2強磁性層23の異方性軸60に合わせて指向され得る第2磁化方向231を呈する第2強磁性層23、及びトンネル障壁22から構成される。第1電流ライン4が、第1方向70に沿って延在し且つ前記磁気トンネル接合2とやりとりし、この第1電流ライン4は、界磁電流41の通電時に前記第2磁化方向231を指向させるための磁場42を提供するために形成されている。前記磁場42の少なくとも或る成分が、この磁場42の供給時に前記異方性軸60に対してほぼ垂直にあるように、MRAMセル1が、前記第1電流ライン4に関連して形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

半導体装置及び磁気ランダムアクセスメモリ

【課題】高速な読み出し動作に適しながらメモリセルの面積を低減することができる磁壁移動型の磁気ランダムアクセスメモリを提供する。

【解決手段】メモリセル10が、磁気記録層2と、固定層11、12と、磁気記録層2に対向するように設けられたリファレンス層41、42、43と、トンネルバリア膜31、32、33とを備えている。固定層11は上方向に固定された磁化を有し、固定層12は、下方向に固定された磁化を有している。リファレンス層41、42、43は、上方向に固定された磁化を有している。リファレンス層41、42、43及びトンネルバリア膜31、32、33は、固定層11、12の間の位置に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

【課題】ソース及びドレインにハーフメタルを用いたトランジスタを提供する。

【解決手段】一方のスピンに対し金属的スピンバンド構造を、他方のスピンに対し半導体的スピンバンド構造をとるハーフメタルからなり、スピン偏極した伝導キャリアを注入する強磁性ソースと、注入されたスピン偏極した伝導キャリアを受けるハーフメタルからなる強磁性ドレインと、強磁性ソースと強磁性ドレインとの間に設けられた半導体層と、強磁性ソースと半導体層との間及び強磁性ドレインと半導体層との間に設けられた金属層と、半導体層に対して形成されるゲート電極と、ソース及びドレインに対して形成された非磁性コンタクトと、を有し、金属層は、半導体層との界面において、ショットキー接合を形成し、非磁性コンタクトのフェルミエネルギーは、それぞれ強磁性ソース及び強磁性ドレインの半導体的スピンバンドのバンドギャップ中を横切るトランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法

【課題】単純な方式で集積度が向上し電気的特性が改善された3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は、互いに異なるレベルに配置され、2つの交差点を定義する第1、第2、及び第3導線と、2つの交差点の各々に配置される2つのメモリセルを備え、第1及び第2導線は互いに平行に延長され、第3導線は延長されて第1及び第2導線と交差し、第1及び第2導線は垂直断面で見た時に第3導線の長さに沿って交互に配列され、第3導線は第1及び第2導線から垂直に離隔される。

(もっと読む)

21 - 40 / 354

[ Back to top ]