Fターム[5E319BB09]の内容

印刷回路に対する電気部品等の電気的接続 (35,455) | 接続材料 (4,656) | 形状、性質又は組成が特定されているはんだ (3,830) | Auを含有するはんだ (75)

Fターム[5E319BB09]に分類される特許

21 - 40 / 75

導電接続シートの製造方法、端子間の接続方法、接続端子の形成方法、半導体装置および電子機器

【課題】金属層に亀裂や皺が生じることなく、金属層と樹脂組成物層との間で優れた密着性が維持された導電接続シートを製造することができる導電接続シートの製造方法、かかる製造方法により製造された導電接続シートを用いた端子間の接続方法、接続端子の形成方法、信頼性の高い半導体装置、および、電子機器を提供すること。

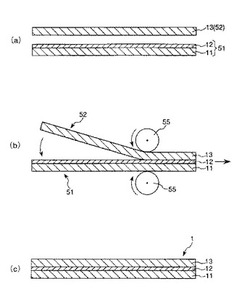

【解決手段】本発明の導電接続シートの製造方法で製造される導電接続シート1は、樹脂組成物層11、13と、樹脂組成物層11、13同士の間でこれらに互いに接合する金属層12とを有するものであり、この導電接続シート1は、樹脂組成物層11と金属層12とを備えるシート51および樹脂組成物層13を備えるシート52をそれぞれ用意する工程と、金属層12の樹脂組成物層11と反対側の面と、樹脂組成物層13の一方の面とが対向するようにして、シート51とシート52とを圧着する工程とを経ることにより製造される。

(もっと読む)

Au−Sn合金はんだペースト、およびこれにより形成されるAu−Sn合金はんだ

【課題】 280℃以下の低温で接合が可能なAu−Sn合金はんだペーストであって、かつこのペーストにより形成されたAu−Sn合金はんだは、Sn−Ag系鉛フリーはんだによるセカンドリフロー時にも溶融しない。LED素子にやさしい接合が可能でかつ、セカンドリフロー時にも溶融することがなく、低Au化による材料コスト低減を可能とするAu−Sn合金はんだペーストを提供する。

【解決手段】 AuとSnとの合計100質量部に対して、Snを55〜70質量部含むAu−Sn混合粉末と、(B)フラックスとを含み、成分(A)が、(A1)AuとSnとの合計100質量部に対して、Snを18〜23.5質量部含むAu−Sn合金はんだ粉末、および(A2)AuとSnとの合計100質量部に対して、Snを88〜92質量部含むAu−Sn合金はんだ粉末を含む。

(もっと読む)

チップ部品接合装置、チップ部品接合方法

【課題】光素子を基板に実装する際に、光素子の厚さ寸法公差の影響や基板の光素子を実装する電極の厚さ寸法公差や基板の反り変形により、基板の実装面と光素子の受発光面との高さ方向の寸法がばらつく事を防止し、光モジュールの特性を安定させる。

【解決手段】光素子の受発光面を搭載ステージの上面に密接するように固定し、基板を搭載加圧するZステージの下面に固定された基板の基準面または基板に設けた台座の基準面を同じ搭載ステージの上面に接触させた時のZステージの変位を記憶した後、所望の変位で実装すべくZステージをZ駆動機構とコントローラにより制御して光素子と基板とを接合材を介して接合する。

(もっと読む)

透明の基板の上にデバイスを導電性結合する方法

本発明は、少なくとも1つの導電性層と電気デバイスを導電性結合する方法に関するものであり、導電性層は光の可視波長領域で実質的に透明の基板に塗布され、次の各ステップを含んでおり、すなわち、電気デバイスまたは導電性層にデバイスが導電性層と結合されるべき領域ではんだ材料が施され、はんだ材料にエネルギー源から放出されるエネルギーが供給され、それにより、はんだ材料が溶融し、取外し可能でない物質接合式の導電性結合が電気デバイスと導電性層との間に構成される。 (もっと読む)

半田付け用AuGe合金球

【課題】電子部品などの接合、封止用半田付け用AuGe合金球の半田付け特性向上。

【解決手段】AuGe合金中のAu含有率が84.5〜89.0質量%の範囲において、Au、Ge以外の金属元素含有量総量を120ppm未満とすることによってGe微粒子が均一微細に分散した組織とする。

これらGeの共晶組成付近において、不純物含有量を上記範囲に抑制することによって、合金球の真球度が向上し、Au初晶及びデンドライトの発達が抑制され、均一一様で微細な共晶組織からなるAuGe合金球が得られる。

この組織を有するAuGe合金球は、流れ性が著しく向上し、電子部品の接合、封止の半田付けにおける半田付け不良を改善する。

(もっと読む)

バンプ形成方法、この方法によりバンプが形成された基板、およびバンプ形成装置。

【課題】高さの高いバンプを低コストで製造可能なバンプ形成方法及び装置を提供する。

【解決手段】電気回路が形成された基板Wに回路接続用のバンプを形成するバンプ形成装置BSは、基板Wを保持する基板保持装置1と、ノズル30に供給された銅微粒子Gをノズル内部のガス気流に分散させて流下させ、下端の噴射口35から気体とともに噴射する噴射装置3とを備える。そして、基板保持装置1に保持された基板Wに、噴射口35から銅微粒子Gを気体とともに噴射して衝突固着させ、常温かつ常圧下で、基板Wの表面に銅バンプを形成する。

(もっと読む)

ろう付け方法及びろう付け装置

【課題】 本発明の目的は、鉛フリー半田を用いても、例えば、配線基板の如き装着物と、例えば、これに搭載する電子部品の如き被装着物との接合強度が高く、かつそのばらつきも少なく、しかもその接合強度の経時的変化が少なく、長期的に信頼性の高いろう付け方法及びこのろう付け方法を採用したろう付け装置を提供することにある。

【解決手段】 本発明のろう付け方法は、鉛フリーのろう材を加熱溶融させろう付けを行うろう付け方法において、加熱溶融させたろう材の冷却工程を超音波を付加しながら時間―温度制御することを特徴とする。

(もっと読む)

吸着コレットおよび実装方法

【課題】六角錘状の錐体を有するチップを傾きなく安定して保持することができるとともにチップの破損を防止することができる吸着コレット、および六角錘状の錐体を有するチップの破損を防止しつつ当該チップを実装基板に対して位置精度良く実装することが可能な実装方法を提供する。

【解決手段】吸着コレット30は、六角錘状の錐体11を有するチップたるLEDチップ10を吸着するためのチップ吸着用凹所31がコレット本体30aの先端部に形成され、当該コレット本体30に、チップ吸着用凹所31に連通する真空吸着孔32が形成されている。チップ吸着用凹所31は、六角形状に開口され六角錘状の錐体31の各側面11aそれぞれに面接触可能な6つの傾斜面31aで囲まれた六角錘状の凹所からなり、コレット本体30aは、全芳香族ポリイミド樹脂により形成されている。

(もっと読む)

鉛フリーソルダペースト

【課題】従来のSn-Zn系鉛フリーは、Znが数10μm程度に大きく晶出し、粗大な晶出物を抑制するこは困難であり、はんだ付け温度を変更させずに接合強度を向上させることは困難であった。はんだに微量の1B属を添加して、強度を改善した合金もあったが、溶融温度が高くなってしまい、Sn-Pbと同じ温度プロファイルではリフローできないという一長一短を有するものであった。

【解決手段】Sn-Zn系鉛フリーソルダペーストのはんだ粉末に、粒子径が5〜300nmで、Ag、Au、Cuから選ばれた1種類以上含んだナノ粒子を含有したエタノール溶液とフラックスとはんだ粉末を混和したソルダペーストを使用することで、はんだ付け時にAg、AuおよびCuとZnの合金を作ることによって、液相中に微細なクラスターを形成させ、溶融後に微細なはんだ組織を得る。

(もっと読む)

ボール搭載装置

【課題】吐出ヘッドから吐出したフラックスの到達位置精度を高くすることができるボール搭載装置を提供すること。

【解決手段】ワークとして基板Wの表面に設けられた複数の電極Tの上に導電性ボールBを搭載するボール搭載装置100は、基板Wを移動するワーク移動手段としての搬送ステージ2と、電極Tに対し液状のフラックスを吐出するフラックス吐出手段としてのフラックス吐出装置10とを有し、フラックス吐出装置10は、ボール搭載装置100に対して固定位置とされ、搬送ステージ2は、基板Wを、電極Tがフラックス吐出装置10のフラックスの到達位置に位置するように移動することとしている。

(もっと読む)

基板上にはんだ堆積物を形成する方法

はんだ堆積物を基板上に形成する方法であって、次の工程i)少なくとも1つのコンタクト領域を含む表面を有する電気回路構成を含む基板を準備し、ii)前記基板表面上に配置され、かつパターン形成されるはんだマスク層を形成して前記少なくとも1つのコンタクト領域を露出させ、iii)前記はんだマスク層及び前記少なくとも1つのコンタクト領域を含む全基板領域を、導電性層を前記基板表面上に設けるのに適した溶液と接触させ、iv)スズ又はスズ合金を含有するはんだ堆積物層を前記導電性層上へ電気めっきし、及びv)スズ又はスズ合金を含有する前記はんだ堆積物層及び前記導電性層を、前記はんだ堆積物層と前記導電性層の双方ともを前記はんだマスク層領域から、前記少なくとも1つのコンタクト領域上にはんだ堆積物層を残して除去するのに十分な量をエッチ除去することを含んでなる方法が記載される。  (もっと読む)

(もっと読む)

位置合わせ性に優れたはんだペーストを用いた基板と被搭載物の接合方法

【課題】はんだペーストを用いて基板に対して被搭載物を同じ位置および方向となるように接合する方法を提供する。

【解決手段】メタライズ層を形成した基板におけるメタライズ層とメタライズ層を形成した正方形状を有する被搭載物4におけるメタライズ層との間にはんだペースト3を搭載または塗布したのちリフロー処理して基板と正方形状を有する被搭載物4をはんだペーストを用いた基板と正方形状を有する被搭載物を接合する際に、前記基板の表面に形成されるメタライズ層の面積が被搭載物4のメタライズ層の面積よりも小さいメタライズ層本体部分6と前記メタライズ層本体部分6の周囲から突出した少なくとも2個のはんだ誘引部メタライズ層7とからなる平面形状を有していると、リフロー処理中に正方形状の被搭載物4の対角線と前記はんだ誘引部メタライズ層7の突出方向とが一致するように回転してはんだ付けされる。

(もっと読む)

回路基板の製造方法

【課題】 めっき用給電配線を有さず、回路配線、外部電極及びボンディングパッドの寸法が、最終的に通電やボンディングに必要な容量を有する断面積を有する回路基板の製造方法を提供する。

【解決手段】

絶縁体表面に下地金属層を有する基材を用いて、最終的に電解めっき用の給電配線が無い回路基板を製造する方法であって、下地金属層上に形成する前駆体として最終的に必要な回路配線の厚さよりも厚く、且つ最終的に必要な回路配線幅より広い幅を有する前駆体を形成し、前記下地金属層と共に該前駆体をエッチング除去して所定寸法の回路配線、外部電極及びボンディングパッドを形成する。

(もっと読む)

金属および乳酸縮合物から構成される物質および電子部品

本発明は、銅、銀、および金の群から選択される金属と乳酸縮合物とを含む物質、ならびに金属、セラミック、または酸化物でできた表面を有する電子部品、ならびに電子部品上に金属表面を生成するための方法に関する。 (もっと読む)

位置合わせ性に優れたはんだペーストを用いた基板と被搭載物の接合方法

【課題】はんだペーストを用いて基板に対して被搭載物を同じ位置および方向となるように接合する方法、特にAu−Sn合金はんだペーストを用いて基板に対して素子を同じ位置および方向となるように接合する方法を提供する。

【解決手段】メタライズ層を有する基板のメタライズ層とメタライズ層を有する被搭載物のメタライズ層との間にはんだペースト3を搭載または塗布したのち非酸化性雰囲気中でリフロー処理して基板と被搭載物を接合するはんだペーストを用いた基板と被搭載物の接合方法において、前記基板のメタライズ層を図1(a)のように面積が被搭載物4のメタライズ層の面積よりも小さいメタライズ層本体部分6と前記メタライズ層本体部分6の周囲から突出したはんだ誘引部7とからなる平面形状を有するようにすると、被搭載物が図1(b)の如くはんだ誘引部7の方向に揃ってはんだ付けされる。

(もっと読む)

ボイド発生の少ないAu−Sn合金はんだペーストを用いた基板と素子の接合方法

【課題】Au−Sn合金はんだ接合部にボイドが発生することの少ないAu−Sn合金はんだペーストを用いた基板と素子の接合方法を提供する。

【解決手段】基板1のメタライズ層2と素子4のメタライズ層2´との間にAu−Sn合金はんだペースト3を搭載または塗布したのち非酸化性雰囲気中でリフロー処理して基板1と素子4を接合するAu−Sn合金はんだペーストを用いた基板と素子の接合方法において、前記基板1のメタライズ層2の面積が素子4のメタライズ層2´の面積よりも小さいことを特徴とする。

(もっと読む)

プリント回路基板の製造方法および使用ならびにプリント回路基板

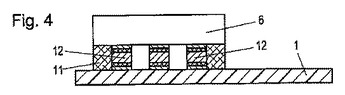

本発明は、構成部品(6)をプリント回路基板(1)へ、またはプリント回路基板内に固定する、および/またはプリント回路基板の個々の素子を接続する方法で、相互接続または互いに固定される構成部品(6)および/またはプリント回路基板(1)の領域が少なくとも1つのそれぞれのはんだ層(4、5、9、10)とともに備えられ、はんだ層(4、5、9、10)は周囲条件に対して高められた圧力および温度で互いに接触および相互接続され、金属間拡散層(12)が形成され、それにより、高い強度の接続を実現する。さらに本発明は前記方法の使用およびプリント回路基板(1)にも関するものである。  (もっと読む)

(もっと読む)

ピン転写用Au−Sn合金はんだペースト

【課題】ピン転写量にバラツキが少ないピン転写用Au−Sn合金はんだペーストを提供する。

【解決手段】RAフラックス:10越え〜25質量%と、残部がSn:15〜25質量%を含有し、残りがAuおよび不可避不純物からなる成分組成を有するAu−Sn合金はんだ粉末とからなるピン転写用Au−Sn合金はんだペーストにおいて、前記ピン転写用Au−Sn合金はんだペーストに含まれるAu−Sn合金はんだ粉末は平均粒径:5μm未満でかつ最大粒径:10μm以下の粒度分布を有し、前記ピン転写用Au−Sn合金はんだペーストの粘度は10〜50Pa・s未満の範囲内にあることを特徴とする。

(もっと読む)

半田ペースト及び半田接合部の製造方法

【課題】半田接合部のボイドの発生を抑制することができる半田ペーストを提供する。

【解決手段】半田金属粉と、予め水素を吸蔵させた水素吸蔵合金粉と、フラックスとを含有する半田ペーストを用いて、水素吸蔵合金が大気圧下で水素を放出する温度以上に加熱することによって、半田を溶融させると共に、水素吸蔵合金から水素を放出させてペースト系外に水素を吐き出させて半田接合部を製造することにより、水素と共に、ボイド発生の原因となるガスおよびブラックス成分を系外に吐き出させることができ、半田接合部のボイドの発生を抑制することができる。

(もっと読む)

多層バンプ構造物及びその製造方法

ベース基板を封止実装するための保護基板に電気的に連結されて前記ベース基板と前記保護基板を予め設定された間隔だけ離間させる第1層と、前記第1層と電気的に連結され、前記ベース基板の表面上に共融接合される第2層を含むことを特徴とする多層バンプ構造物が開示される。前記第1層は、前記第2層と前記ベース基板の共融温度よりも高い溶融点を有することができる。前記多層バンプ構造物を使用すれば、ベース基板の表面上に形成されたMEMS素子などのような微細構造物が駆動するための空間を確保することができ、封止実装過程で接合物質の拡がりによって基板上の隣接構造物又は電極間で接触が発生しないという利点がある。 (もっと読む)

21 - 40 / 75

[ Back to top ]