Fターム[5E346HH01]の内容

多層プリント配線板の製造 (97,916) | 目的、課題、効果 (10,213) | 電気的特性に関するもの (2,662)

Fターム[5E346HH01]の下位に属するFターム

低インピーダンス化 (111)

特性インピーダンスの整合 (248)

クロストークの低減化 (188)

伝播遅延時間の低減化 (69)

高周波性能の向上 (427)

電気的接続性 (824)

絶縁性 (181)

Fターム[5E346HH01]に分類される特許

61 - 80 / 614

多層基板の製造方法

【課題】ピール強度が高く、耐熱性及び耐クラック性に優れ、伝送損失が小さい多層基板の製造方法、及び前記多層基板を提供すること。

【解決手段】表面粗度(Rz)が2500nm以下である導体層の表面にシクロオレフィンポリマーをグラフトして樹脂層1を形成する工程(A)、及び樹脂層1を加熱硬化するか、又は樹脂層1の上に、有機ポリマーを含む樹脂層2を少なくとも1層積層し、加熱硬化して、絶縁層を形成する工程(B)を有する、多層基板の製造方法、及び前記製造方法により得られる多層基板。

(もっと読む)

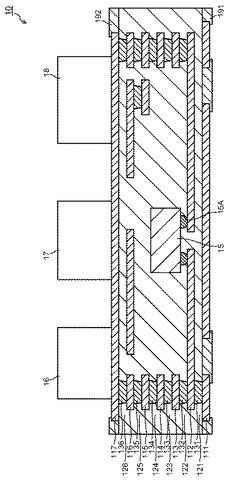

電圧変換モジュール

【課題】電圧変換用ICを内蔵させた多層配線板上に、入力側コンデンサ、並びに出力側コンデンサ及びインダクタを配列してなる電圧変換モジュールにおいて、入力電圧に重畳されるノイズを低減して、安定した出力電圧を得る。

【解決手段】互いに離隔して順次に積層されてなる複数の配線パターン、これら複数の配線パターン間それぞれに位置する絶縁部材、及び前記複数の配線パターン間を電気的に接続する層間接続体を有し、電圧変換用IC15が内蔵された多層配線板10上において、第1のコンデンサ16、第2のコンデンサ17及びインダクタ18を実装し、第1のコンデンサの入力部と記インダクタとの間に、第1のコンデンサにおける他方の電極部又は第2のコンデンサにおける電極部の一方を位置させ、他方の電極部又は電極部の一方を電気的にグランドに設定する。

(もっと読む)

電子回路装置及びその製造方法

【課題】本発明は、薄型化並びに小型化を実現しつつ、積層基板のエレクトロマイグレーションに起因する導電体間の短絡を防止することができ、磁性体を含む素子の電気的特性を向上することができる電子回路装置及びその製造方法を提供する。

【解決手段】電子回路装置において、第1の絶縁基材121(2)と、第1の絶縁基材121(2)の表面上に配設された第1の導電体128(1)と、第1の絶縁基材121(2)の裏面上に配設された第2の導電体126(1)と、第1の絶縁基材121(2)の裏面上に第2の導電体126(1)を介在し接着された第2の絶縁基材122(1)とを備えたトランス基板12と、トランス基板12に配設された磁性体と、基板12の第1の絶縁基材121(2)の端面から第2の絶縁基材122(1)の端面に渡って配設された絶縁性を有する樹脂被膜129とを備える。

(もっと読む)

配線基板

【課題】半導体集積回路素子に対して十分な電源供給を行なって半導体集積回路素子を良好に作動させることが可能な配線基板を提供すること。

【解決手段】第2のビア群における隣接する複数個ずつが第2のパッド7GのピッチP1より狭いピッチP2で寄り集まった複数のビアグループ6Bを形成しているとともに、隣接するビアグループ6Bに接続されたビアランド3L同士の間に第1の電源プレーン3Pが介在し、ビアランド3L同士の間の第1の電源プレーン3Pを通して第1のパッド7P群の各列から第1のスルーホール5Pへの導電路が形成されている特徴とする配線基板である。半導体素子接続パッド7への電源供給路が多数確保され半導体集積回路素子Sに対して十分な電源供給を行なって半導体集積回路素子Sを良好に作動させることができる。

(もっと読む)

半導体搭載装置用基板、半導体搭載装置

【課題】高い信頼性を得ることができる半導体搭載装置用基板を提供すること。

【解決手段】本発明の半導体搭載装置用基板10では、多層配線基板11の第1主面12の半導体チップ搭載領域23に、半導体チップ21がフリップチップ接続方式で表面実装されうる。多層配線基板11の第2主面13において半導体チップ21の直下となる箇所には、板状部品搭載領域53をなす複数の第2主面側はんだバンプ52が形成されている。複数の第2主面側はんだバンプ52を介して、無機材料を主体とする板状部品101がフリップチップ接続方式で多層配線基板11上に表面実装されている。第2主面13と板状部品101との隙間S2に設けられた第2主面側アンダーフィル107により、複数の第2主面側はんだバンプ52が封止されている。

(もっと読む)

コンデンサとその製造方法ならびに多層配線基板

【課題】簡便・安価に製造可能な浮遊インダクタンスの小さいコンデンサ部品と、その製造方法を提供する。また、前記コンデンサ部品を低背化した部品と、その低背コンデンサを内蔵した多層配線基板を提供する。

【解決手段】有機材料の単分子膜を誘電体とするコンデンサにおいて、コンデンサ用電極のうち少なくとも一つが、誘電体単分子膜に担持された触媒物質によって開始する無電解めっきで形成されることを特徴とするコンデンサ。コンデンサを支持基材の上に形成することで、薄膜コンデンサを部品として扱うことが可能となる。また、前記支持基材を薄く研削することで、部品の低背化が可能となる。

(もっと読む)

電子装置及び電子モジュール

【課題】ノイズの遮蔽を十分に行うことができ、かつLSIを3次元的に配置する際に空間を有効的に利用することができるようにする。

【解決手段】配線基板100には半導体装置103が内蔵されている。配線基板100には、平面視で半導体装置103と重なる領域に互いに離間して設けられた複数の第1導体106と、複数の第1導体106の少なくとも一つを半導体装置103に接続するビア120と、半導体装置103を介して複数の第1導体106とは反対側に設けられ、平面視で複数の第1導体106を覆っている第2導体102と、複数の第1導体106を介して半導体装置103とは反対側に設けられ、平面視で第1導体106を覆っている第3導体101と、第2導体102と第3導体101によって挟まれた空間に、半導体装置103を囲むように設けられ、繰り返し構造を有する構造体とを備える。

(もっと読む)

キャパシタおよびその製造方法、回路基板、半導体装置

【課題】ビルドアップ基板中に内蔵できるキャパシタを、エアロゾルデポジション法を使って形成する。

【解決手段】金属よりなる第1の基体上に第1のセラミック膜を形成する工程と、金属よりなる第2の基体上に第2のセラミック膜を形成する工程と、前記第1および第2のセラミック膜の一方の表面に銅よりなる第1の電極パタ―ンと第1のビアプラグパタ―ンとを、相互に離間して形成する工程と、前記第1および第2の基体を互いに押圧することにより、前記第1のセラミック膜と前記第2のセラミック膜とを、前記第1の基体と前記第2の基体とが押圧された状態で、前記第1の基体と前記第2の基体との間にパルス電圧を印加することにより、前記第1および第2のセラミック膜を、前記第1の電極パターンおよび前記第1のビアプラグパタ―ンを介して相互に接合する工程と、前記第2の基体を除去する工程と、を含む。

(もっと読む)

高周波スイッチ

【課題】出力特性が優れた高周波スイッチを提供する。

【解決手段】本発明の実施形態の高周波スイッチは、入力端子ANT1と複数のスイッチング素子と複数の高周波信号線と複数の出力端子RF1〜RF8とからなる高周波スイッチ回路部を有する高周波スイッチICチップ10を備える。前記入力端子ANT1と前記複数の出力端子の各出力端子RF1〜RF8は、それぞれ等しい長さの高周波信号線H1〜H8で接続される。前記複数の出力端子RF1〜RF8は、前記高周波スイッチICチップの外周の表面上に配置される。前記入力端子ANT1は、前記高周波スイッチ回路部の中心に配置される。

(もっと読む)

多層回路基板、基板装置、および多層回路基板の異常判定方法

【課題】スイッチング素子の駆動により生じる熱について精度よく検出することのできる多層回路基板を提供する。

【解決手段】パワー基板4の基板本体10は、積層された複数の絶縁層11,12,13の間に導電層21,22が配置された構成を有している。基板本体10の上面10aにベアチップ実装された半導体チップ15は、スイッチング素子28と、上温度センサ29と、を含んでいる。CPU7は、上温度センサ29の検出温度T1、およびスイッチング素子28の発熱量Q1を用いて疑似熱抵抗TR1を演算する。CPU7は、疑似熱抵抗TR1が大きいとき、パワー基板4に異常が生じていると判定する。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できると共に高い信頼性を有するプリント配線板を提供する。

【解決手段】 コンデンサ20を収容するコア基板30に樹脂絶縁層144,244と導体回路158,258とを積層してなるプリント配線板10であって、コア基板30は、コンデンサ20を収容する通孔11Aの形成された第1のコア基板11の上下に第2、第3のコア基板12U,13Dを積層してなり、第1、第2、第3のコア基板11,12U,13Dは、芯材に樹脂を含浸してなり、樹脂絶縁層144,244は、芯材を有しない樹脂材料からなり、第2、第3のコア基板12U、13Dの少なくとも一方に、コンデンサ20の電極21,22に接続するバイアホール60を形成し、バイアホール60とコンデンサ20の電極21,22との間に電気的接続を取る。

(もっと読む)

部品内蔵配線板

【課題】半導体チップ接続の信頼性および配線板としての機能性を保全した上で、低コストで製造が可能な部品内蔵配線板を提供すること。

【解決手段】積層状に位置する、第1、第2の絶縁層と、端子パッドを有し該端子パッドを有する面が第1の絶縁層に対向するように、第2の絶縁層中に埋設された半導体チップと、第1の絶縁層上に、第2の絶縁層との間に挟まれるように設けられた、すずが含有される金属の皮膜によって被覆されたフリップ接続用のランドを含みかつ該ランドの表層を除いては該皮膜で被覆されていない第1の配線パターンと、半導体チップの端子パッドと第1の配線パターンのランドとの間に挟設された金バンプと、金バンプをその内部に封止するように設けられたアンダーフィル樹脂と、第1の絶縁層の第1の配線パターンが設けられた側の面とは反対の側の面上に設けられた第2の配線パターンとを具備する。

(もっと読む)

回路基板の製造方法

【課題】導電性ペーストによるビア接続を具備する回路基板に対して、極めて容易かつ確実にビア接続が確保できる回路基板の製造方法を提供する。

【解決手段】プリプレグシート11の両面に有機質フィルム12を備え、かつ所望の位置に導電性ペーストが充填された貫通穴13を具備する回路基板の製造方法であって、その貫通穴13において(前記有機質フィルムの穴径rf1、rf2/前記有機質フィルムの厚みtf1、tf2)が3以上であることを特徴とする。

(もっと読む)

配線基板及びその実装構造体

【課題】本発明は、信号伝送特性に優れた配線基板及びその実装構造体を提供するものである。

【解決手段】本発明の一形態にかかる配線基板3は、樹脂層7と該樹脂層7上に配された導電層13とを備え、樹脂層7は、基材10と、該基材10を被覆するとともに該基材10よりも誘電率の低い樹脂部11と、を有し、基材10は、長手方向が互いに平行な複数の第1繊維10xfからなる第1繊維束10xと、長手方向が互いに平行な複数の第2繊維10yfからなり、第1繊維束10xと交差する第2繊維束10yと、を具備し、樹脂部11の一部は、第1繊維10xf同士の間、第2繊維10yf同士の間及び第1繊維10xfと第2繊維10yfとの間に配されるとともに空隙Vを含んでおり、第1繊維束10xと第2繊維束10yとの交差領域Cにおける空隙Vの密度は、非交差領域Nにおける空隙Vの密度よりも高い。

(もっと読む)

配線基板及びその製造方法

【課題】簡易な方法で、配線に対するガラス繊維密度の疎密の影響を低減することが可能な配線基板及びその製造方法を提供する。

【解決手段】本配線基板は、複数の第1繊維束、及び前記複数の第1繊維束とは異なる方向に配置された複数の第2繊維束が織り込まれた補強部材と、絶縁性の樹脂と、を含む絶縁層と、前記絶縁層上に配置された並走する一対の差動配線と、を有し、前記絶縁層の一部の領域において、前記第1繊維束及び前記第2繊維束は平面方向に蛇行しており、前記差動配線は、前記絶縁層の一部の領域上に配置されていることを要件とする。

(もっと読む)

サスペンション用基板、サスペンション、ヘッド付サスペンション、ハードディスクドライブおよびサスペンション用基板の製造方法

【課題】本発明は、伝送信号強度の損失を抑制しつつ、反りの発生抑制および低剛性化を図ることができるサスペンション用基板を提供することを主目的とする。

【解決手段】本発明は、ライト側配線構造およびリード側配線構造を有し、上記ライト側配線構造は、ライト側凹部を有する第一絶縁層と、上記ライト側凹部に形成されたライト側第一配線層と、上記ライト側第一配線層を覆う第二絶縁層と、上記第二絶縁層上であり、かつ、上記ライト側第一配線層に厚さ方向において重複するライト側第二配線層とを有し、上記リード側配線構造は、リード側凹部を有する上記第一絶縁層と、上記リード側凹部に形成されたリード側第一配線層と、上記リード側第一配線層を覆う上記第二絶縁層と、上記第二絶縁層上であり、かつ、上記リード側第一配線層に厚さ方向において重複するリード側第二配線層とを有することを特徴とするサスペンション用基板を提供することにより、上記課題を解決する。

(もっと読む)

半導体装置

【課題】製造工程を簡素化しつつ、スイッチング素子起因の高周波ノイズを抑制し、且つ、製造時における電子部品の信頼性を向上できる半導体装置を提供する。

【解決手段】複数の樹脂フィルムとともに電子部品を積層して積層体とし、この積層体を加圧・加熱することで、一括で樹脂フィルムを一体化しつつ電子部品を封止してなる。配線部のうち、ハーフブリッジ回路及びコンデンサの接続点とスイッチング素子とを接続する第1配線部、スイッチング素子を接続する第2配線部、接続点とコンデンサを接続する第3配線部、ゲート電極と制御ICを接続する第4配線部が、絶縁基材の厚さ方向に沿って設けられている。上記配線部を除く配線部である第5配線部は、導体パターンの表面及び該表面の裏面に層間接続ビアがそれぞれ接続され、2つの層間接続ビアが絶縁基材の厚み方向に垂直な方向において、互いに重ならないように離間して配置された配線部分を含む。

(もっと読む)

セラミック多層基板および電子モジュール

【課題】ESD保護機能を有し、低コストで小型のセラミック多層基板および電子モジュールを提供する。

【解決手段】セラミック多層基板は、セラミックを含む複数の絶縁層が積層されており、内部に配線導体が形成されている基板層11と、基板層11の一方の主面に形成されている端子電極21と、前記一方の主面であって端子電極21と離れた位置に形成されているグランド電極22と、端子電極21およびグランド電極22から引き出されており、端子電極21とグランド電極22との間の領域に、互いに対向するように形成されている一対の放電電極31、32と、端子電極21の周縁の少なくとも一部及びグランド電極22の周縁の少なくとも一部を覆い、一対の放電電極31、32の対向する部分を含むように空洞35を形成する空洞形成層33と、を有するESD保護素子と、を備える。

(もっと読む)

多層配線基板

【課題】不要放射ノイズを十分に低減することができる多層配線基板を得る。

【解決手段】第1の信号電極層40、グランド電極層30、電源電極層20及び第2の信号電極層10をこの順で積み上げて積層体を構成した多層配線基板。多層配線基板の上面にはIC60が実装され、裏面には3端子コンデンサ46が実装される。第1の信号電極層40は、入力側実装用ランド42、該入力側実装用ランド42に接続した入力側電源供給パターン41、出力側実装用ランド43、該出力側実装用ランド43に接続した出力側電源供給パターン44及びグランド側実装用ランド45が設けられている。電源電極層20には電源電極21が設けられている。第2の信号電極層10にはIC実装用ランド11が設けられている。

(もっと読む)

電子機器

【課題】伝送損失を改善してデータ伝送の高速化に無理なく対応できるとともに、容易に製造できるフレキシブルプリント配線板を得る。

【解決手段】フレキシブルプリント配線板15は、第1の絶縁層18と、第1の絶縁層に積層された信号ライン24と、第1の絶縁層に積層されたグランドライン25と、グランドラインに積層されるとともに、グランドラインの上に開口された複数の開口部28が設けられた第2の絶縁層20と、信号ラインを覆い、グランドラインに電気的に接続されたグランド層21と、グランド層を覆う第3の絶縁層22と、を含む。グランド層は、開口部から露出されたグランドラインを覆うように開口部に充填された第1の導電性ペースト30と、第1の導電性ペーストおよび第2の絶縁層を連続して覆うように塗布された第2の導電性ペースト31とで構成されている。第2の導電性ペーストは、前記第1の導電性ペーストよりも体積抵抗率が小さい。

(もっと読む)

61 - 80 / 614

[ Back to top ]