Fターム[5F004DA16]の内容

半導体のドライエッチング (64,834) | 処理に用いるガス (14,486) | CHF3 (793)

Fターム[5F004DA16]に分類される特許

61 - 80 / 793

半導体装置の製造方法および半導体装置

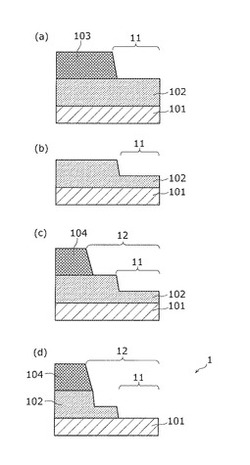

【課題】良好な側壁形状の開口を有する半導体装置の製造方法および半導体装置を提供する。

【解決手段】GaAs基板101上に形成された誘電体膜102の一部を誘電体膜102の表面から所定の深さまでエッチングする第1のエッチング工程と、第1のエッチング工程により誘電体膜102がエッチングされた第1のエッチング領域11において誘電体膜102をエッチングしてGaAs基板101の表面を露出し、かつ、第1のエッチング領域11を包含する第2のエッチング領域12において第1のエッチング領域11以外の領域に配置された誘電体膜102を所定の膜厚までエッチングする第2のエッチング工程とを含む。

(もっと読む)

エッチング装置及び方法

【課題】シリコン等をエッチングするための反応ガスの利用効率を高め、エッチングレートを高くする。

【解決手段】被処理物9を搬入側排気チャンバー20、処理チャンバー10、搬出側排気チャンバー30の順に搬送する。処理チャンバー10内に反応ガスを導入する。排気手段5によって、排気チャンバー20,30の内圧が外部の圧力及び処理チャンバー10の内圧より低圧になるよう、排気チャンバー20,30内のガスを吸引して排気する。好ましくは、連通口13,14におけるガス流の流速を0.3m/sec〜0.7m/secとする。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

プラズマ処理チャンバ

【課題】プラズマエッチングリアクタの静電チャックの寿命を向上させるチャンバ洗浄機構を提供する。

【解決手段】一実施形態において、プラズマを生成するよう構成されたプラズマ処理チャンバ100は、基板を受けるよう構成された内側下部電極131と、内側下部電極の外側に配置された外側下部電極133とを備えた下部電極アセンブリを備えている。プラズマ処理チャンバは、上部電極111を備え内側下部電極131と外側下部電極133との真上に配置された上部電極アセンブリ112を、さらに備える。

(もっと読む)

フォトマスクブランク、フォトマスク、反射型マスクブランクおよび反射型マスク並びにこれらの製造方法

【課題】極めて微細なパターンを形成できるフォトマスクブランク及びそのフォトマスクブランクに微細パターンを形成したフォトマスクを提供する。

【解決手段】透明基板上に、少なくとも2層からなる薄膜を有するフォトマスクブランクであって、前記薄膜は、タンタル、窒素、およびキセノンを含む材料からなる第1の層と、該第1の層の上面に積層されるタンタル、酸素、およびアルゴンを含む材料からなる第2の層とを有することを特徴とする。

(もっと読む)

レジストパターン形成方法およびそれを用いたパターン化基板の製造方法

【課題】レジストパターンの形成において、残膜をエッチングする工程後のレジストパターンの凸部の幅が、残膜をエッチングする工程前におけるレジストパターンの凸部の幅以上の所望の幅となることを可能とする。

【解決手段】凹凸パターンが転写されたレジスト膜2の残膜エッチング工程が、エッチングの際に堆積物4を生成する堆積性ガスを含有する第1のエッチングガスを用いて、レジストパターンにおける凸部の側壁に堆積物4が堆積しかつ残膜がエッチングされる条件でレジスト膜2をエッチングする第1のエッチング工程を含み、堆積物4を含めた上記凸部の幅が残膜エッチング工程前における上記凸部の幅以上の所望の幅となるように第1のエッチング工程以後の工程によってレジスト膜2をエッチングする。

(もっと読む)

プラズマエッチング方法および記憶媒体

【課題】無機膜をマスクとして有機膜をエッチングする場合に、ボーイング等のエッチング形状不良を生じさせずにエッチングすることができるプラズマエッチング方法を提供すること。

【解決手段】処理容器内に、その表面がシリコン含有物からなる上部電極と、被処理基板が載置される下部電極とが配置され、上部電極と下部電極との間にプラズマを形成して被処理基板に対してプラズマエッチングを行うプラズマエッチング装置を用い、無機膜をマスクとして被処理基板の有機膜をプラズマエッチングするにあたり、有機膜を途中までプラズマエッチングし、その後、プラズマを形成しつつ上部電極に負の直流電圧を印加して、エッチング部位の側壁に上部電極のシリコン含有物を含む保護膜を形成し、その後、プラズマエッチングを継続する。

(もっと読む)

シリコン基板のエッチング方法、及びシリコン基板のエッチング装置

【課題】シリコン絶縁層とシリコン基板とを貫通する孔の加工の精度を配線が含まれる領域にて高めることのできるシリコン基板のエッチング方法、及びシリコン基板のエッチング装置を提供する。

【解決手段】ダミー配線13d,15dの埋め込まれた凹部を有して該凹部の内面にはバリアメタル層13b,15bが形成されたシリコン絶縁層13a,15aを有するシリコン基板11に対して、シリコン絶縁層13a,15aとシリコン基板11とを貫通する孔をダミー配線13d,15dが含まれる領域に形成する。ダミー配線13d,15d、バリアメタル層13b,15b、シリコン絶縁層13a,15aをエッチングした後にシリコン基板11をエッチングする。加えて、シリコン基板11のエッチングを終了する前に、シリコン絶縁層13a,15a及びシリコン基板11の少なくとも1つを希ガスでスパッタする。

(もっと読む)

プラズマ処理装置及びプラズマ処理方法

【課題】基板に対してプラズマ処理を行う装置についてダミー基板を用いずにプラズマによりクリーニングするにあたり、載置台表面の損傷を抑制することのできる技術を提供すること。

【解決手段】プラズマエッチング処理後に、サセプタ3の表面を露出した状態でプラズマエッチング装置の真空容器1の内部をプラズマPによりクリーニングし真空容器1の内部に付着した反応生成物Aを除去する。このとき、プラズマPに直流電圧を印加する。これにより、高密度なプラズマPを得ながらそのプラズマPのイオンエネルギーを低減させることができるため、良好なクリーニングを行いつつサセプタ3の表面の損傷を抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】 反射電極の表面にダメージを与えることなく、異物を除去する技術が望まれている。

【解決手段】 半導体ウエハのチップ領域に、複数の反射電極を形成する。反射電極の表面を覆うように、半導体ウエハの上に絶縁膜を形成する。反射電極が絶縁膜で覆われた状態で、チップ領域とは異なるナンバリング領域に、凹凸による識別標識を形成する。識別標識を形成した後、反射電極の上面が露出するまで絶縁膜を除去する。

(もっと読む)

表面処理用ノズル装置

【課題】 ワーク表面に均一な濃度で処理ガスを吹き付けることができる表面処理用ノズル装置を提供する。

【解決手段】

ノズル装置のガス通路は、処理ガスが供給されるガス供給口と、上記ガス供給口からの処理ガスを分け、一直線上に間隔をおいて水平に並んだ多数の分岐下流端12bへと送る通路分岐部と、これら分岐下流端12bの配列方向と平行をなして直線的に連続して延びる合流部80と、流れ方向変更部90と、吹出スリット61とを有している。流れ方向変更部90は、多数の分岐下流端12bから合流部80へ送られてきた処理ガスを、下向きに送る第1通路部分91と、上向きに送る第2通路部分92と、下向きに送る第3通路部分93とを有し、この第3通路部分93からの処理ガスが吹出スリット61からワークWに向かって下向きに吹き付けられる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

プラズマ反応装置部品の製造方法及び装置

【課題】イットリア部品の製造方法を提供する。

【解決手段】固形イットリアサンプルが処理開始時に用意される。固形イットリアサンプルを高温環境に曝露することでイットリアサンプルを焼結し、機械加工して部品を形成し、部品を既定の加熱速度で加熱してアニーリングする。部品を一定のアニーリング温度で維持し、部品を既定の冷却速度で冷却することを含む。この方法を用いて製造したバルクイットリア部品は、例えば応力の軽減や強化された耐化学薬品性を含む、特性の改善を示すことが判明した。

(もっと読む)

プラズマ処理装置用電極板

【課題】プラズマの逆流を防止して冷却板の損傷を防ぐことができ、被処理基板に面内均一なプラズマ処理を行わせることができるプラズマ処理装置用電極板を提供する。

【解決手段】電極板3は、厚さ方向に貫通する通気孔11が複数設けられてなり、通気孔11は、径が大きい第1穴部21と、第1穴部21より径が小さい第2穴部22とが互いに連通して形成されており、第1穴部21は被処理基板側の放射面3aに開口し、電極板3の中央部に配置される通気孔11の第2穴部22の長さBは、電極板3の外周部に配置される通気孔11の第2穴部22に比べて短く設定されている。

(もっと読む)

半導体装置の製造方法及びコンピュータ記録媒体

【課題】効率良く多段の良好な形状の階段状の構造を形成することのできる半導体装置の製造方法及びコンピュータ記録媒体を提供する。

【解決手段】第1の誘電率の第1の膜と、第1の誘電率とは異なる第2の誘電率の第2の膜とが交互に積層された多層膜と、多層膜の上層に位置しエッチングマスクとして機能するフォトレジスト層とを有する基板をエッチングして、階段状の構造を形成する半導体装置の製造方法であって、フォトレジスト層をマスクとして第1の膜をプラズマエッチングする第1工程と、水素含有プラズマにフォトレジスト層を晒す第2工程と、フォトレジスト層をトリミングする第3工程と、第3工程によってトリミングしたフォトレジスト層及び第1工程でプラズマエッチングした第1の膜をマスクとして第2の膜をエッチングする第4工程とを有し、第1工程乃至第4工程を繰り返して行うことにより、多層膜を階段状の構造とする。

(もっと読む)

表面処理方法及び装置

【課題】被処理基板の第1面の表面処理を抑制又は防止しながら、第1面とは反対側の第2面を反応ガスにて表面処理する。

【解決手段】搬送手段2にて被処理基板9を搬送路3に沿って搬送し、反応室10に搬入する。被処理基板9の第1面9aを搬送路3と直交する方向の第1側に向け、かつ第2面9bを第2側に向ける。反応ガスを供給部30の供給口39から反応室10に供給する。反応室10内の搬送路3より第1側の第1室部11のうち被処理基板9にて第2室部12と隔てられた第1隔室部分11aに置換手段50から不活性ガスからなる置換ガスを供給し、第1隔室部分11aのガスを置換ガスに置換する。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】窓部の損傷を低減させることができるプラズマ処理装置およびプラズマ処理方法を提供する。

【解決手段】プラズマ処理装置は処理容器2と、前記処理容器の内部を減圧する減圧部9と、被処理物を載置する載置部4と、内部にガスを供給するガス供給部18と、電磁波を透過させる窓部3と、前記窓部の外方に配置され、電磁場を発生させる複数の導体部21と複数の容量部とを有した負荷部20と、前記負荷部20に電力を印加する電源6bと、を備えている。前記導体部21と前記容量部とは電気的に交互に接続され、被処理物のプラズマ処理を行う場合には、前記容量部同士の間に設けられた前記導体部21において電位差の虚数成分が0(ゼロ)となる位置が生じるようにされ、前記負荷部20の第1の端子と、第2の端子と、の間における電位差の虚数成分の値が電位差の実数成分の値以下とされている。

(もっと読む)

モノフルオロメタンの製造方法

【課題】

半導体工業で求められている、フッ素以外のハロゲンを実質上含まないモノフルオロメタンを実用的かつ効率的に製造する方法を提供する。

【解決手段】

本発明は、1−メトキシ−1,1,2,2−テトラフルオロエタンを触媒と接触させて熱分解する熱分解工程と、熱分解生成物からモノフルオロメタンを回収する工程とを少なくとも有するモノフルオロメタンの製造方法であり、回収する工程において行われる分離は、蒸留、吸収、反応などによることができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

パターン形成方法及び半導体装置の製造方法

【課題】基板の温度が100℃以下の低温環境下において、基板上の被処理膜をエッチングする際のマスクを所定のパターンに適切に形成する。

【解決手段】ウェハWの被処理膜400上に反射防止膜401とレジストパターン402が形成される(図10(a))。レジストパターン402がトリミングされると共に、反射防止膜401がエッチングされる(図10(b))。ウェハWの温度を100℃以下に維持した状態でプラズマ処理を行い、レジストパターン402及び反射防止膜パターン403上に、100MPa以下の膜ストレスを有するシリコン窒化膜404が成膜される(図10(c))。シリコン窒化膜404がエッチングされ、レジストパターン402及び反射防止膜パターン403が除去されて、被処理膜400上にシリコン窒化膜パターン405が形成される(図10(d))。

(もっと読む)

61 - 80 / 793

[ Back to top ]